# Dual (180° Out-of-Phase) PWM and Linear Controller

## **ISL6446**

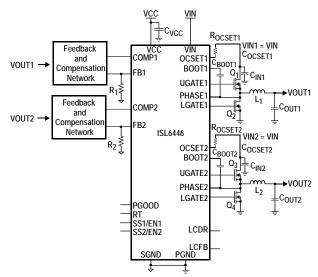

The ISL6446 is a high-performance, triple output controller that provides a single high-frequency power solution primarily for Broadband, DSL and Networking applications. This device integrates complete control, monitoring and protection functions for two synchronous buck PWM controllers and one linear controller. Input voltage ripple and total RMS input current is substantially reduced by synchronized 180° out-of-phase operation of the two PWMs.

The two PWM buck converters provide simple voltage mode control. The output voltage of the converters can be precisely regulated to as low as 0.6V, with a maximum tolerance of  $\pm 1.5\%$  over-temperature and line variations. Programmable switching frequency down to 100kHz provides optimized low cost solution for ATX power supplies. It's also able to operate up to 2.5MHz to deliver compact solutions. The linear controller provides a low-current output.

Each PWM controller has soft-start and independent enable functions combined on a single pin. A capacitor from SS/EN to ground sets the soft-start time; pulling SS/EN pin below 1V disables the controller. Both outputs can soft-start into a pre-biased load.

The ISL6446 incorporates robust protection features. An adjustable overcurrent protection circuit monitors the output current by sensing the voltage drop across the upper MOSFET  $r_{DS(ON)}.$  Latch-off mode overcurrent operation protects the DC/DC converters from damage under overload and short circuit conditions. A PGOOD signal is issued when soft-start is complete and PWM outputs are within 10% of their regulated values and the linear regulator output is higher than 75% of its nominal value. Thermal shut-down circuitry turns the device off if the IC temperature exceeds +150  $^{\circ}$  C.

## **Features**

- 4.5V to 5.5V or 5.5V to 24V input voltage range

- · Three programmable power output voltages

- Two PWM controllers with out-of-phase operation

- Voltage-mode PWM control

- One linear controller

- · Programmable switching frequency from 100kHz to 2.5MHz

- · Fast transient response

- High-bandwidth error amplifier

- · Extensive circuit protection functions

- Undervoltage, and over-temperature

- Overvoltage with latch-off mode

- Programmable overcurrent limit with latch-off mode

- Lossless current sensing (no sense resistor needed)

- · Externally adjustable soft-start time

- Independent enable control

- Voltage tracking capability

- Able to soft-start into a pre-biased load

- · PGOOD output with delay

## **Applications**

- · ATX power supplies

- DSP, ASIC, and FPGA point of load regulation

- · Industrial and security networking applications

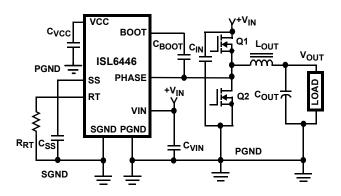

FIGURE 1. TYPICAL APPLICATION

FIGURE 2. EFFICIENCY vs LOAD CURRENT (OBTAINED FROM ISL6446EVAL1Z)

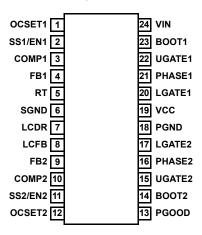

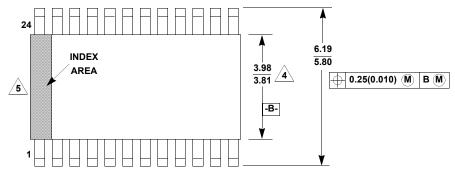

# **Pin Configuration**

ISL6446 (24 LD QSOP) **TOP VIEW**

# **Pin Descriptions**

| SYMBOL    | PIN#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                              | DESCRIPTION                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                 |  |  |  |  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| B00T1, 2  | 23, 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | These pins power are the upper MOSFET drivers of each PWM converter. The anode of each internal bootstrap diode is connected to the VCC pin. The cathode of the bootstrap diode is connected to this pin, which should also connect to the bootstrap capacitor.                                                                                              |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                 |  |  |  |  |

| UGATE1, 2 | 22, 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | These pins provide t                                                                                                                                                                                                                                                                                                                                         | he gate drive for upper MOSFETs, bootstrapped from the VCC pin.                                                                                                                                                                      |                                                                                                                                                                                                                                                                 |  |  |  |  |

| PHASE1, 2 | 21, 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                                                                                                                                                                                                                                                                                                                                                            | on points of the upper MOSFET sources, the output filter inductor and lower MOSFET drains. Connect thes he respective converter.                                                                                                     |                                                                                                                                                                                                                                                                 |  |  |  |  |

| LGATE1, 2 | 20, 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | These are the output                                                                                                                                                                                                                                                                                                                                         | s of the lower N-Channel MOSFET drivers, sourced from the VCC pin.                                                                                                                                                                   |                                                                                                                                                                                                                                                                 |  |  |  |  |

| PGND      | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                              | power ground connection for the lower gate drivers. This pin should be connected to the source of the lower and PWM2 and the negative terminals of the external input capacitors.                                                    |                                                                                                                                                                                                                                                                 |  |  |  |  |

| FB1, 2    | 4, 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | •                                                                                                                                                                                                                                                                                                                                                            | ected to the feedback resistor divider and provide the voltage feedback signals for the respective controller. The e of the converter. In addition, the PGOOD circuit and OVP circuit use these inputs to monitor the output voltage |                                                                                                                                                                                                                                                                 |  |  |  |  |

| COMP1, 2  | 3, 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •                                                                                                                                                                                                                                                                                                                                                            | These pins are the error amplifier outputs for the respective PWM. They are used, along with the FB pins, as the compensation point for the PWM error amplifier.                                                                     |                                                                                                                                                                                                                                                                 |  |  |  |  |

| PGOOD     | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | This is an open drain logic output used to indicate the status of the output voltages. This pin is pulled low when either of the two PWM outputs is not within 10% of the respective nominal voltage or when the linear output drops below 75% of its nominal voltage. To maintain the PGOOD function if the linear output is not used, connect LCFB to VCC. |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                 |  |  |  |  |

| SGND      | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | This is the signal ground, common to both controllers, and must be routed separately from the high current grounds (PGND). All voltage levels are measured with respect to this pin.                                                                                                                                                                         |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                 |  |  |  |  |

| VIN       | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 24                                                                                                                                                                                                                                                                                                                                                           | ceramic capacitor as                                                                                                                                                                                                                 | controllers with an internal linear regulator (if VIN > 5.5V) and must be closely decoupled to ground using solose to the VIN pin as possible. The VIN is the input voltage applied to the upper FET of both converters <b>LE 1. INPUT SUPPLY CONFIGURATION</b> |  |  |  |  |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | INPUT                                                                                                                                                                                                                                                                                                                                                        | PIN CONFIGURATION                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                 |  |  |  |  |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5.5V to 24V                                                                                                                                                                                                                                                                                                                                                  | Connect the input supply to the VIN pin. The VCC pin will provide a 5V output from the internal voltage regulator.                                                                                                                   |                                                                                                                                                                                                                                                                 |  |  |  |  |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5V ±10%                                                                                                                                                                                                                                                                                                                                                      | Connect the input supply to the VCC pin.                                                                                                                                                                                             |                                                                                                                                                                                                                                                                 |  |  |  |  |

| VCC       | This pin supplies the bias for the regulators, powers the low-side gate drivers and external boot circuitry for high-side gate The IC may be powered directly from a single 5V (±10%) supply at this pin; when used as a 5V supply input, this pin mu externally connected to VIN. When VIN > 5.5, VCC is the output of the internal 5V linear regulator output. The VCC pin must be decoupled to power ground with a minimum of 1μF ceramic capacitor, placed very close to the pin. |                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                 |  |  |  |  |

# Pin Descriptions (Continued)

| SYMBOL             | PIN#  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

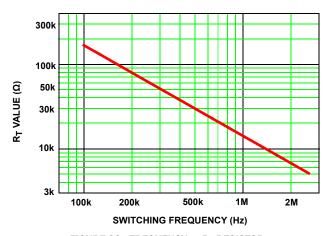

| RT                 | 5     | This is the operating frequency adjustment pin. By placing a resistor from this pin to the SGND, the oscillator frequency can be programmed from 100kHz to 2.5MHz.                                                                                                                                                                                                                                                                    |

| SS1/EN1<br>SS2/EN2 | 2, 11 | These pins provide enable/disable and soft-start function for their respective controllers. The output is held off when the pin is pulled to ground. When the chip is enabled, the regulated 30µA pull-up current source charges the capacitor connected from the pin to ground. The output voltage of the converter follows the ramping voltage on the SS/EN pin. See "Soft-Start and Voltage Tracking" on page 11 for more details. |

| LCFB               | 8     | This pin is the feedback pin for the linear controller. An external voltage divider network connected to this pin sets the output voltage of the linear controller. If the linear controller is not used, tie this pin to the VCC.                                                                                                                                                                                                    |

| LCDR               | 7     | Open drain output PNP Transistor or P-channel MOSFET Driver. The LCDR connects to the base of an external PNP pass transistor or the gate of the MOSFET to form a positive linear regulator. A small resistor can be inserted between the LCDR and the base of the PNP pass transistor or the gate of the MOSFET to alleviate thermal stress at output short condition.                                                               |

| OCSET1, 2          | 1, 12 | These pins are the overcurrent set points for the respective PWM controllers. Connect a resistor ( $R_{OCSET}$ ) from this pin to the drain of the upper MOSFET. $R_{OCSET}$ , an internal 110 $\mu$ A current source, and the upper MOSFET ON-resistance $r_{DS(ON)}$ set the converter overcurrent (OC) trip point according to Equation 1:                                                                                         |

|                    |       | $I_{OC} = \frac{I_{OCSET} \cdot R_{OCSET}}{r_{DS(ON)}} $ (EQ. 1)                                                                                                                                                                                                                                                                                                                                                                      |

|                    |       | I <sub>OC</sub> includes the DC load current, as well as the ripple current. An overcurrent trip initiates hiccup mode.  The voltage on the OCSET pin should not exceed 0.7V above the VIN pin voltage for proper current sensing when the UGATE is turned on.                                                                                                                                                                        |

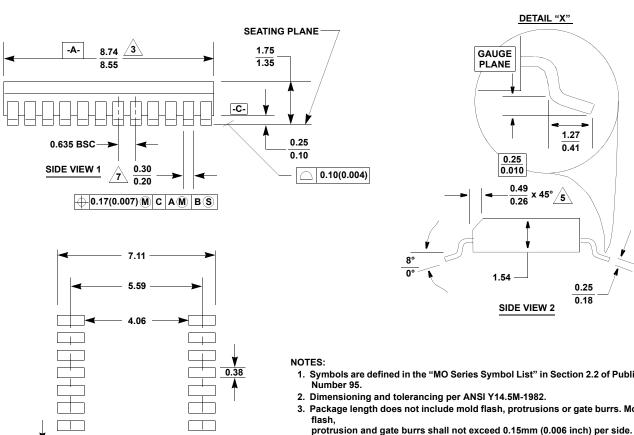

# **Ordering Information**

| PART NUMBER     | PART        | TEMP       | PACKAGE    | PKG.   |

|-----------------|-------------|------------|------------|--------|

| (Notes 1, 2, 3) | MARKING     | RANGE (°C) | (Pb-free)  | DWG. # |

| ISL6446IAZ      | ISL 6446IAZ | -40 to +85 | 24 Ld QSOP | M24.15 |

## NOTES:

- 1. Add "-T\*" suffix for tape and reel. Please refer to <a href="IB347">IB347</a> for details on reel specifications.

- 2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 3. For Moisture Sensitivity Level (MSL), please see device information page for ISL6446. For more information on MSL please see tech brief TB363.

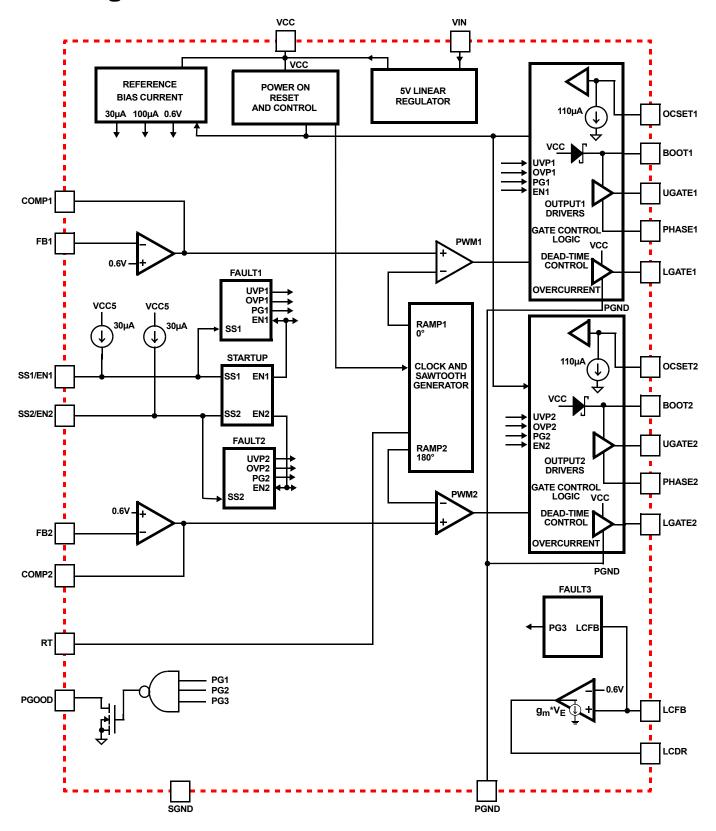

# **Block Diagram**

FIGURE 3. BLOCK DIAGRAM

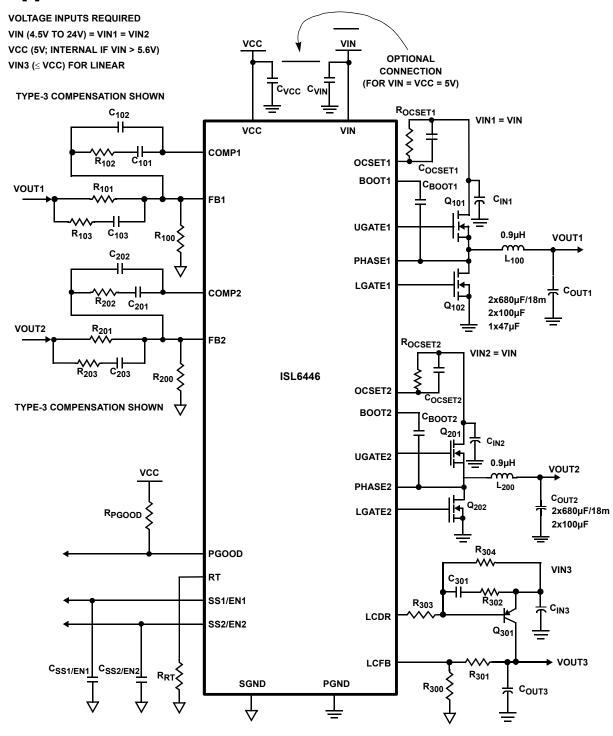

# **Typical Application Schematics**

FIGURE 4. ISL6446 TYPICAL APPLICATION

## **Absolute Maximum Ratings** (Note 4)

| SS1/EN1, SS2/EN2, COMP1, COMP2 to SGND0                | .3V to +6.0V  |

|--------------------------------------------------------|---------------|

| VCC, FB1, FB2, RT, PGOOD to SGND0                      | .3V to +6.0V  |

| LCDR, LCFB to SGND0                                    | .3V to +6.0V  |

| VIN, OCSET1, and OCSET2 to PGND                        | 0.3V to +28V  |

| BOOT1 and BOOT2 to PGND                                | 0.3V to +33V  |

| BOOT1 to PHASE1, and BOOT2 to PHASE2                   | .3V to +6.0V  |

| UGATE1 to PHASE10.3V to (B                             | 00T1 +0.3V)   |

| UGATE2 to PHASE20.3V to (B                             | 00T2 +0.3V)   |

| LGATE1, LGATE2 to PGND                                 | (VCC+0.3V)    |

| PHASE1, PHASE2 to PGND                                 | 1V to 28V     |

| SGND to PGND                                           | -0.3V to 0.3V |

| ESD Rating                                             |               |

| Human Body Model (Tested per JESD22-A114E)             | 2500V         |

| Machine Model (Tested per JESD22-115-A)                | 150V          |

| Latch Up (Tested per JEDEC-78B Level II Class A) ±100r | nA @ +85°C    |

## **Thermal Information**

| Thermal Resistance (Typical)              | $\theta_{JA}$ (°C/W) | θ <sub>JC</sub> (°C/W) |

|-------------------------------------------|----------------------|------------------------|

| QSOP Package (Notes 5, 6)                 | 75                   | 36                     |

| Maximum Junction Temperature (Plastic Pac | kage)5               | 5°C to +150°C          |

| Maximum Storage Temperature Range         | 6                    | 5°C to +150°C          |

| Temperature Range                         | 4                    | 10°C to +85°C          |

| Pb-Free Reflow Profile                    |                      | see link below         |

| http://www.intersil.com/pbfree/Pb-FreeRe  | eflow.asp            |                        |

## **Recommended Operating Conditions**

| V <sub>CC</sub> Supply Voltage | 5V ±10%     |

|--------------------------------|-------------|

| V <sub>IN</sub> Supply Voltage | 5.5V to 24V |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 4. All voltages are measured with respect to GND.

- 5.  $\theta_{\text{JA}}$  is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief IB379 for details.

- 6. For  $\theta_{\mbox{\scriptsize JC}},$  the "case temp" location is taken at the package top center.

**Electrical Specifications** Operating Conditions Unless Otherwise Noted:  $V_{IN} = 12V$ , or  $V_{CC} = 5V \pm 10\%$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ . Typical values are at  $+25^{\circ}C$ . Boldface limits apply over the operating temperature range,  $-40^{\circ}C$  to  $+85^{\circ}C$

| PARAMETER                                                    | SYMBOL                                   | TEST CONDITIONS                                                                                                              | MIN<br>(Note 9) | TYP    | MAX<br>(Note 9) | UNITS |

|--------------------------------------------------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------|--------|-----------------|-------|

| VIN SUPPLY                                                   |                                          |                                                                                                                              |                 |        |                 | 1     |

| Input Operating Supply Current                               | I <sub>CC_op</sub>                       | V <sub>IN</sub> = 5.5V or 12V; LGATE <sub>x</sub> , UGATE <sub>x</sub> Open, FB forced above regulation point (no switching) |                 | 4.5    | 7.5             | mA    |

| Input Standby Supply Current                                 | I <sub>CC_sb</sub>                       | V <sub>IN</sub> = 5.5V, 12V, 24V;<br>SS1/EN1 = SS2/EN2 = 0V                                                                  |                 | 1.25   | 3               | mA    |

| VCC INTERNAL REGULATOR                                       | I.                                       |                                                                                                                              | 11              |        |                 | 1     |

| Output Voltage                                               | v <sub>vcc</sub>                         | V <sub>IN</sub> = 5.6V, SS1/EN1 = SS2/EN2 = 0V<br>No Additional Load                                                         | 4.5             | 5.35   |                 | V     |

| Output Voltage                                               | V <sub>VCC</sub>                         | V <sub>IN</sub> = 24V, SS1/EN1 = SS2/EN2 = 0V<br>No Additional Load                                                          |                 | 5.36   | 5.6             | V     |

| Output Voltage                                               | V <sub>VCC</sub>                         | V <sub>IN</sub> = 12V, SS1/EN1 = SS2/EN2 = 0V<br>IVCC= 80mA                                                                  | 4.5             | 5.2    |                 | V     |

| VCC Current Limit (Note 7)                                   | I <sub>ICC_CL</sub>                      | VCC is pulled to PGND; (Note 8)                                                                                              |                 | 300    |                 | mA    |

| REFERENCE AND SOFT-START                                     |                                          |                                                                                                                              |                 |        |                 |       |

| Reference Voltage at FB1, FB2                                | V <sub>REF1</sub> ,<br>V <sub>REF2</sub> | V <sub>IN</sub> = 5V or 12V; T <sub>A</sub> = +25°C                                                                          |                 | 0.6000 |                 | v     |

|                                                              |                                          | V <sub>IN</sub> = 5V or 12V; T <sub>A</sub> = 0 °C to +85 °C                                                                 | 0.5925          |        | 0.6085          | V     |

|                                                              |                                          | V <sub>IN</sub> = 5V or 12V; T <sub>A</sub> = -40°C to +85°C                                                                 | 0.5900          |        | 0.6085          | V     |

| Reference Voltage at FB1, FB2                                | V <sub>REF1</sub> ,                      | V <sub>IN</sub> = 24V; T <sub>A</sub> = +25°C                                                                                |                 | 0.6015 |                 | V     |

|                                                              | V <sub>REF2</sub>                        | V <sub>IN</sub> = 24V; T <sub>A</sub> = 0°C to +85°C                                                                         | 0.5930          |        | 0.6100          | V     |

|                                                              |                                          | V <sub>IN</sub> = 24V; T <sub>A</sub> = -40°C to +85°C                                                                       | 0.5915          |        | 0.6100          | ٧     |

| EN <sub>x</sub> /SS <sub>x</sub> Soft-Start Current          | I <sub>SSx</sub>                         |                                                                                                                              | 20              | 30     | 40              | μΑ    |

| EN <sub>X</sub> /SS <sub>X</sub> Enable Threshold            | V <sub>ENx</sub>                         |                                                                                                                              | 850             | 940    | 1050            | mV    |

| EN <sub>x</sub> /SS <sub>x</sub> Enable Threshold Hysteresis | V <sub>ENx_hys</sub>                     | (Note 7)                                                                                                                     |                 | 15     |                 | mV    |

## **ISL6446**

**Electrical Specifications** Operating Conditions Unless Otherwise Noted:  $V_{IN} = 12V$ , or  $V_{CC} = 5V \pm 10\%$ ,  $T_A = -40 ^{\circ}C$  to  $+85 ^{\circ}C$ . Typical values are at  $+25 ^{\circ}C$ . Boldface limits apply over the operating temperature range,  $-40 ^{\circ}C$  to  $+85 ^{\circ}C$  (Continued)

| PARAMETER                                                          | SYMBOL                 | TEST CONDITIONS                                         | MIN<br>(Note 9) | TYP  | MAX<br>(Note 9) | UNITS |

|--------------------------------------------------------------------|------------------------|---------------------------------------------------------|-----------------|------|-----------------|-------|

| EN <sub>X</sub> /SS <sub>X</sub> Soft-Start Top of Ramp<br>Voltage | V <sub>SSx_top</sub>   | (Note 7)                                                |                 | 3.12 |                 | V     |

| POWER-ON RESET ON VCC                                              |                        |                                                         |                 |      |                 |       |

| Rising Threshold                                                   | V <sub>POR_r</sub>     |                                                         | 4.2             | 4.4  | 4.48            | ٧     |

| Falling Threshold                                                  | V <sub>POR_f</sub>     |                                                         | 3.85            | 4.0  | 4.1             | ٧     |

| PWM CONVERTERS                                                     |                        |                                                         |                 |      |                 |       |

| Minimum UGATE on Time                                              | t <sub>UGATE_min</sub> | (Note 7)                                                |                 | 100  |                 | ns    |

| Maximum Duty Cycle                                                 | DC <sub>max</sub>      | V <sub>IN</sub> = 5.0V or 12V; F <sub>SW</sub> = 300kHz | 95              |      |                 | %     |

| Maximum Duty Cycle                                                 | DC <sub>max</sub>      | V <sub>IN</sub> = 5.0V; F <sub>SW</sub> = 2.58MHz       | 80              |      |                 | %     |

| FB <sub>X</sub> Pin Bias Current                                   | I <sub>FBx</sub>       | VFB1 = VFB2 = 600mV                                     | -250            | 30   | 250             | nA    |

| OSCILLATOR                                                         |                        |                                                         |                 |      |                 |       |

| Low End Frequency                                                  | F <sub>SW</sub>        | V <sub>IN</sub> = 12V; RT = 163kΩ                       |                 | 103  |                 | kHz   |

| Oscillation Frequency                                              | F <sub>SW</sub>        | V <sub>IN</sub> = 5V or 12V; RT = 52.3kΩ                | 270             | 300  | 330             | kHz   |

|                                                                    |                        | V <sub>IN</sub> = 24V; RT = 52.3kΩ                      | 270             | 305  | 340             | kHz   |

| High End Frequency                                                 | F <sub>SW</sub>        | $V_{IN}$ = 5V; RT = 4.75k $\Omega$                      | 2.25            | 2.5  | 2.75            | MHz   |

|                                                                    |                        | V <sub>IN</sub> = 12V; RT = 4.75kΩ                      | 2.25            | 2.59 | 2.85            | MHz   |

| Frequency Adjustment Range                                         | F <sub>SW</sub>        | RT = 163kΩ; (Note 7)                                    |                 | 0.1  |                 | MHz   |

|                                                                    |                        | RT = 4.75kΩ; (Note 7)                                   |                 | 2.6  |                 | MHz   |

| PWM Sawtooth Ramp Amplitude<br>(Peak-to-Peak)                      | V <sub>P-P</sub>       | (Note 8)                                                |                 | 1.25 |                 | V     |

| PWM Sawtooth Ramp Offset                                           | V <sub>PWM_OFF</sub>   | (Note 8)                                                |                 | 1.25 |                 | ٧     |

| PWM CONTROLLER GATE DRIVER                                         | S (Note 7)             |                                                         |                 |      |                 |       |

| Upper Gate Pull-up Resistance                                      |                        |                                                         |                 | 2.6  |                 | Ω     |

| Upper Gate Pull-down Resistance                                    |                        |                                                         |                 | 2    |                 | Ω     |

| Lower Gate Pull-up Resistance                                      |                        |                                                         |                 | 2.6  |                 | Ω     |

| Upper Gate Pull-down Resistance                                    |                        |                                                         |                 | 2    |                 | Ω     |

| Rise Time                                                          |                        | C <sub>L</sub> = 3300pF                                 |                 | 25   |                 | ns    |

| Fall Time                                                          |                        | C <sub>L</sub> = 3300pF                                 |                 | 25   |                 | ns    |

| Dead Time Between Drivers                                          |                        |                                                         |                 | 20   |                 | ns    |

| ERROR AMPLIFIERS                                                   |                        |                                                         |                 |      |                 |       |

| DC Gain                                                            | Gain                   | (Note 8)                                                |                 | 88   |                 | dB    |

| Gain-Bandwidth Product                                             | GBWP                   | (Note 8)                                                |                 | 15   |                 | MHz   |

| Slew Rate                                                          | SR                     | COMP = 10pF (Note 8)                                    |                 | 5    |                 | V/µs  |

| Maximum Output Voltage V <sub>EA</sub>                             |                        | I <sub>COMP_SRC</sub> = 40μA                            | 3.9             | 4.2  |                 | ٧     |

| Minimum Output Voltage                                             | V <sub>EA_L</sub>      | -<br>I <sub>COMP_SINK</sub> = 40μA                      |                 | 0.8  | 1.1             | ٧     |

| PROTECTION AND OUTPUT MONIT                                        |                        |                                                         |                 |      | 1               |       |

| Overvoltage Threshold OV                                           |                        |                                                         | 111             | 116  | 121             | %     |

| Overvoltage Threshold                                              |                        |                                                         |                 |      |                 |       |

| Overvoltage Threshold Undervoltage Threshold                       | UV                     |                                                         | 77              | 82   | 88              | %     |

## **ISL6446**

**Electrical Specifications** Operating Conditions Unless Otherwise Noted:  $V_{IN} = 12V$ , or  $V_{CC} = 5V \pm 10\%$ ,  $T_A = -40 ^{\circ}C$  to  $+85 ^{\circ}C$ . Typical values are at  $+25 ^{\circ}C$ . Boldface limits apply over the operating temperature range,  $-40 ^{\circ}C$  to  $+85 ^{\circ}C$  (Continued)

| PARAMETER                        | SYMBOL              | TEST CONDITIONS                                                                        | MIN<br>(Note 9) | TYP   | MAX<br>(Note 9) | UNITS |

|----------------------------------|---------------------|----------------------------------------------------------------------------------------|-----------------|-------|-----------------|-------|

| OCSET Current Source             | IOCSET              | V <sub>OCSET</sub> = 4.5V, T <sub>A</sub> = +25°C                                      |                 | 110   |                 | μA    |

| OCSET Current Source             | IOCSET              | V <sub>OCSET</sub> = 4.5V, T <sub>A</sub> = +85°C                                      |                 |       | 140             | μA    |

| LINEAR CONTROLLER                |                     |                                                                                        |                 |       |                 |       |

| Drive Sink Current               | I <sub>LCDR</sub>   | LCDR                                                                                   | 50              |       |                 | mA    |

| LCFB Feedback Threshold          | V <sub>LCFB</sub>   | T <sub>A</sub> = +25°C                                                                 |                 | 0.595 |                 | V     |

|                                  |                     | T <sub>A</sub> = -40°C to +85°C                                                        | 0.570           |       | 0.620           | ٧     |

|                                  |                     | T <sub>A</sub> = 0°C to +70°C                                                          | 0.580           |       | 0.610           | V     |

| LCFB Input Leakage Current       | I <sub>LCFB</sub>   | (Note 7)                                                                               |                 | 80    |                 | nA    |

| Error Amplifier Transconductance | gm                  | V <sub>LCFB</sub> = 0.6V, I <sub>LCDR</sub> = 21mA (Note 7)                            |                 | 2     |                 | A/V   |

| PGOOD                            | 1                   |                                                                                        |                 |       |                 | 1     |

| Power-Good Lower Threshold       | PG_low <sub>x</sub> | LCFB = VCC, L <sub>DO</sub> disabled<br>PGOOD for Ch1 and Ch2 only                     | 88              | 93    | 97              | %     |

| Power-Good Higher Threshold      | PG_hi <sub>X</sub>  | LCFB = VCC, L <sub>DO</sub> disabled<br>PGOOD for Ch1 and Ch2 only                     | 105             | 110   | 115             | %     |

| Power-Good Lower Threshold       | PG_low <sub>3</sub> | L <sub>DO</sub> enabled, PGOOD for L <sub>DO</sub> ;<br>Ch1 and Ch2 disabled; (Note 7) |                 | 72    |                 | %     |

| PGOOD Delay                      | t <sub>PGOOD</sub>  | F <sub>SW</sub> = 1.4MHz (Note 7)                                                      |                 | 46    |                 | ms    |

| PGOOD Leakage Current            | I <sub>PGOOD</sub>  | V <sub>PULLUP</sub> = 5.5V                                                             |                 |       | 5               | μA    |

| PGOOD Voltage Low                | V <sub>PG_low</sub> | I <sub>PGOOD</sub> = -4mA                                                              |                 |       | 0.5             | ٧     |

| THERMAL                          | •                   | •                                                                                      | ,               |       |                 |       |

| Shutdown Temperature             |                     | (Note 8)                                                                               |                 | 150   |                 | °C    |

| Shutdown Hysteresis              |                     | (Note 8)                                                                               |                 | 20    |                 | °C    |

#### NOTES:

- 7. Limits established by characterization.

- 8. Design guideline only; not production tested.

- 9. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

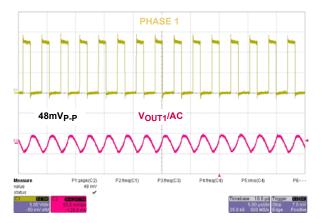

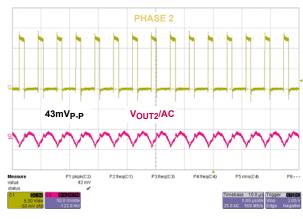

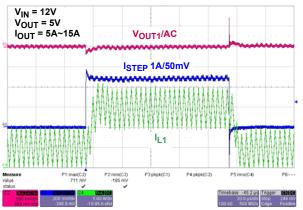

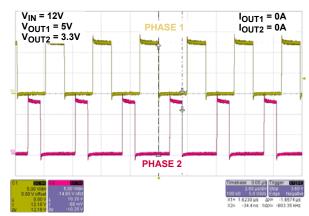

# **Typical Performance Curves**

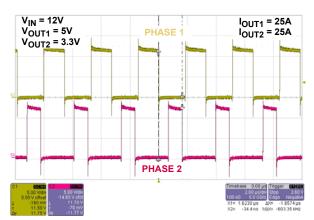

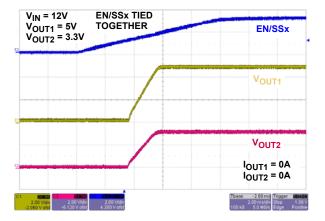

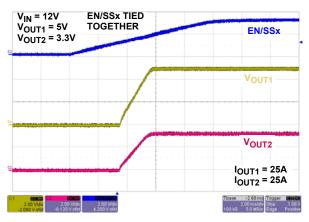

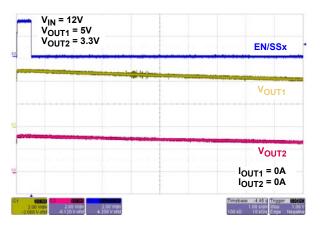

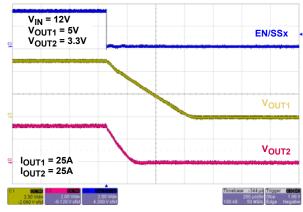

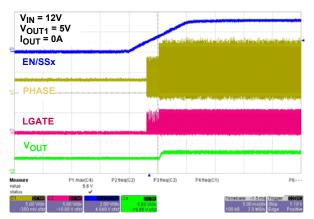

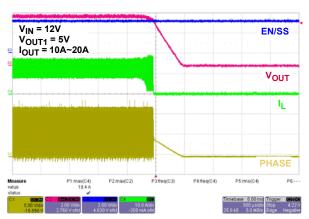

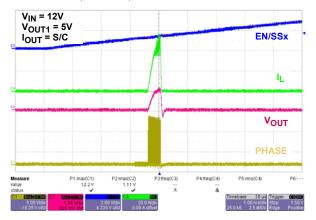

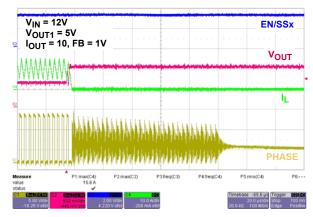

Oscilloscope plots are taken using the ISL6446EVAL1Z evaluation board,  $V_{IN} = 12V$ ,  $V_{OUT1} = 5V$ ,  $V_{OUT2} = 3.3V$ ,  $f_s = 300kHz$ , unless otherwise noted.

FIGURE 5. OUTPUT RIPPLE (PWM1)

FIGURE 6. OUTPUT RIPPLE (PWM2)

FIGURE 7. LOAD TRANSIENT

FIGURE 8. PWM INTERLEAVING

FIGURE 9. PWM INTERLEAVING

# **Typical Performance Curves**

Oscilloscope plots are taken using the ISL6446EVAL1Z evaluation board,  $V_{IN} = 12V$ ,  $V_{OUT1} = 5V$ ,  $V_{OUT2} = 3.3V$ ,  $f_s = 300$ kHz, unless otherwise noted. (Continued)

FIGURE 10. EN/SS START-UP

FIGURE 11. EN/SS START-UP

FIGURE 12. EN/SS SHUT-DOWN

FIGURE 13. EN/SS SHUT-DOWN

FIGURE 14. PRE-BIASED START-UP (V<sub>OUT</sub> PRE-BIASED AT 3.5V)

FIGURE 15. OVERCURRENT PROTECTION

# **Typical Performance Curves**

Oscilloscope plots are taken using the ISL6446EVAL1Z evaluation board,  $V_{IN} = 12V$ ,  $V_{OUT1} = 5V$ ,  $V_{OUT2} = 3.3V$ ,  $f_s = 300$ kHz, unless otherwise noted. (Continued)

FIGURE 16. START-UP WITH OC

# Functional Description Soft-Start and Voltage Tracking

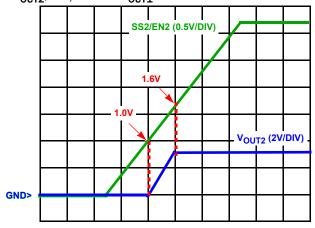

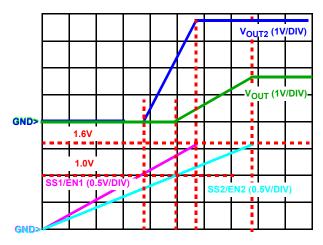

After the VCC pin exceeds its rising POR trip point (nominal 4.4V), the chip operation begins. Both 30 $\mu A$  current sources will start charging up the soft-starting capacitors respectively. The charging continues until the voltage across the soft-start capacitor reaches about 3.2V. From 1.0V to 1.6V, the outputs will ramp individually from zero to full-scale. Now, if V = 0.6V, C = 0.1 $\mu F$ , and I = 30 $\mu A$ , then t = 2ms. Figure 18 shows the typical waveforms for SS2/EN2 and  $V_{OUT2}$ ; SS1/EN1 and  $V_{OUT1}$  are similar.

FIGURE 18. SOFT-START

The soft-start ramps for each output can be selected independently. The basic timing is shown in Equation 2:

$$t = C \bullet \frac{dV}{I}$$

(EQ. 2)

where:

t is the charge time

C is the external capacitance

dV is the voltage charged

I is the charging current (nominal 30µA)

FIGURE 17. OVERVOLTAGE PROTECTION

Finally, there is a delay after 1.6V, until the ramp gets to  $\sim$ 3.2V, which signals that the ramp is done; when both ramps are done, the PGOOD delay begins. To guarantee the soft-start is completed, please make sure the EN/SSx pin voltage is able to reach above 3.2V at normal operation.

FIGURE 19. VOLTAGE TRACKING

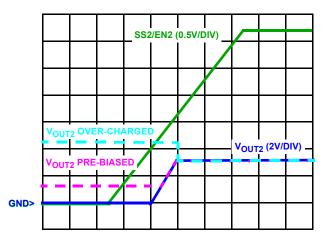

Figure 20 shows pre-biased outputs before soft-start. The solid blue curve shows no pre-bias; the output starts ramping from GND. The magenta dotted line shows the output pre-biased to a voltage less than the final output. The FETs don't turn on until the soft-start ramp voltage exceeds the output voltage; then the output starts ramping seamlessly from there. The cyan dotted line shows the output pre-biased above the final output (but below the OVP (Overvoltage Protection)). The FETs will not turn on until the end of the soft-start ramp; then the output will be quickly pulled down to the final value.

If the output is pre-biased above the OVP level, the ISL6446 will go into OVP at the end of soft-start, which will keep the FETs off. See "Protection Mechanisms" on page 13 for more details.

VOUT1 has the same functionality as previously described for VOUT2. Each output should react independently of the other, unless they are related by the circuit configuration.

FIGURE 20. SOFT-START WITH PRE-BIAS

The linear output does not have a soft-start ramp; however, it may follow the ramp of its input supply, if timed to coincide with its rise, after the VCC rising POR trip. If the input to the linear is from one of the two switcher outputs, then it will share the same ramp rate as the switcher.

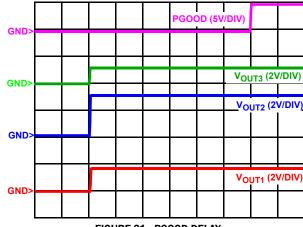

#### **PGOOD**

A group of comparators (separate from the protection comparators) monitor the output voltages (via the FB pins) for PGOOD. Each switcher has a lower and upper boundary (nominally around 90% and 110% of the target value) and the linear has a lower boundary (around 75% of the target). Once both switcher output ramps are done, and all 3 outputs are within their expected ranges, the PGOOD will start an internal timer, with Equation 3:

$$t_{PGOOD} = \frac{0.065}{F_{SW}} \tag{EQ. 3}$$

where:

t<sub>PGOOD</sub> is the delay time (in sec)

$F_{SW}$  is the switching frequency (in MHz)

Once the time-out is complete, the internal pull-down device will shut off, allowing the open-drain PGOOD output to rise through an external pull-up resistor, to a 5V (or lower) supply, which signals that the "Power is GOOD". Figure 21 shows the three outputs turning on, and the delay for PGOOD. If any of the conditions is subsequently violated, then PGOOD goes low. Once the voltage returns to the normal region, a new delay will start, after which the PGOOD will go high again.

The PGOOD delay is inversely proportional to the clock frequency. If the clock is running as slow as 524kHz, the delay will be 125ms long. There is no way to adjust the PGOOD delay independently of the clock.

FIGURE 21. PGOOD DELAY

## **Switching Frequency**

The switching frequency of the ISL6446 is determined by the external resistor placed from the RT pin to SGND. See Figure 22 for a graph of Frequency vs RT Resistance. Use Equation 4 to calculate the approximate RT resistor value for the desired switching frequency. The typical resistance for 100kHz operation is 163k $\Omega$ . Running at both high frequency and high  $V_{IN}$  voltages is not recommended, due to the increased power dissipation on-chip (mostly from the internal VCC regulator, which supplies gate drivers). The user should check the maximum acceptable IC temperature, based on their particular conditions.

$$R_{T} = \left(\frac{F_{SW}}{11290}\right)^{-1.093}$$

(EQ. 4)

FIGURE 22. FREQUENCY vs  $\mathbf{R}_{T}$  RESISTOR

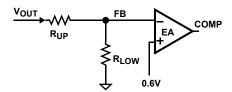

## **Output Regulation**

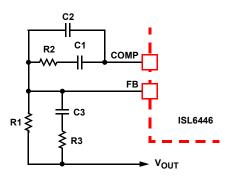

Figure 23 shows the generic feedback resistor circuit for any of the two PWM  $V_{OUT}$ 's; the  $V_{OUT}$  is divided down to equal the reference. All three use a 0.6V internal reference (check the "Electrical Specifications" Table on page 6 for the exact reference value at 24V). The  $R_{UP}$  is connected to the  $V_{OUT}$ ; the  $R_{LOW}$  to GND; the common point goes to the FB pin.

**FIGURE 23. OUTPUT REGULATION**

V<sub>OUT</sub> must be greater than 0.6V and 2 resistors are needed, and their accuracy directly affect the regulator tolerance.

$$FB = V_{OUT} \cdot \frac{R_{LOW}}{R_{UP} + R_{LOW}}$$

(EQ. 5)

Use Equation 6 to choose the resistor values.  $R_{UP}$  is part of the compensation network for the switchers, and should be selected to be compatible;  $1k\Omega$  to  $5k\Omega$  is a good starting value. Find FB from the "Electrical Specifications" Table on page 7 (for the right condition), plug in the desired value for  $V_{OUT}$ , and solve for  $R_{LOW}$ .

$$R_{LOW} = \frac{FB \cdot R_{UP}}{V_{OUT} - FB}$$

(EQ. 6)

The maximum duty cycle of the ISL6446 approaches 100% at low frequency, but falls off at higher frequency; see the "Electrical Specifications" Table on page 7. In addition, there is a minimum UGATE pulse width, in order to properly sense overcurrent. The two switchers are 180° out of phase.

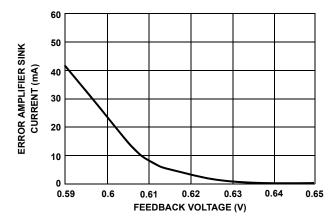

#### **Linear Regulator**

The linear regulator controller is a trans-conductance amplifier with a nominal gain of 2A/V. The N-Channel MOSFET output buffer can sink a minimum of 50mA.

The reference voltage is 0.6V. With 0V differential at its input, the controller sinks 21mA of current. For better load regulation, it is recommended that the resistor from the LDO input to the base of the PNP (or gate of the PFET) is set so that the sink current at G4 pin is within 9mA to 31mA over the entire load and temperature range.

An external PNP transistor or P-Channel MOSFET pass device can be used. The dominant pole for the loop can be placed at the base of the PNP (or gate of the PFET), as a capacitor from emitter-to-base (source to gate of a PFET). Better load transient response is achieved however, if the dominant pole is placed at the output with a capacitor to ground at the output of the regulator.

FIGURE 24. LINEAR CONTROLLER GAIN

#### **Protection Mechanisms**

OCP - (Function independent for both PWM). The overcurrent function protects the PWM Converter from a shorted output by using the upper MOSFET's ON-resistance, r<sub>DS(ON)</sub> to monitor the current. This method enhances the converter's efficiency and reduces cost by eliminating a current sensing resistor. The overcurrent function latches off the outputs to provide fault protection. A resistor connected to the drain of the upper MOSFET and OCSET pin programs the overcurrent trip level. The PHASE node voltage will be compared against the voltage on the OCSET pin, while the upper MOSFET is on. A current (typically 110µA) is pulled from the OCSET pin to establish the OCSET voltage. If PHASE is lower than OCSET while the upper MOSFET is on then an overcurrent condition is detected for that clock cycle. The upper gate pulse is immediately terminated, and a counter is incremented. If an overcurrent condition is detected for 32 consecutive clock cycles, the ISL6446 output is latched off with gate drivers three-stated. The switcher will restart when the SS/EN pin is externally driven below 1V, or if power is recycled to the chip. During soft-start, both pulse termination current limiting and the 32-cycle counter are enabled.

UVP - (Function independent for both PWM). If the voltage on the FB pin falls to 82% (typical) of the reference voltage for 8 consecutive PWM cycles, then the circuit enters into soft-start hiccup mode. During hiccup, the external capacitor on the SS/EN pin is discharged, then released and a soft-start cycle is initiated. The UVP comparator is separate from the one sensing for PGOOD, which should have already detected a problem, before the UVP trips.

OVP - (Function independent for both PWM). OVP function is enabled after the soft start has finished. If voltage on the FB pin rises to 116% (typical) of the reference voltage, the lower gate driver is turned on continuously. If the overvoltage condition continues for 32 consecutive PWM cycles, then that output is latched off with the gate drivers three-stated. The capacitor on the SS/EN pin will not be discharged. The switcher will restart when the SS/EN pin is externally driven below 1V, or if power is recycled to the chip. The OVP comparator is separate from the one sensing for PGOOD, which should have already detected a problem, before the OVP trips.

# **Application Guidelines**

#### **PWM Controller**

#### **DISCUSSION**

The PWM must be compensated such that it achieves the desired transient performance goals, stability, and DC regulation requirements.

The first parameter that needs to be chosen is the switching frequency, F<sub>SW</sub>. This decision is based on the overall size constraints and the frequency plan of the end equipment. Smaller space requires higher frequency. This allows the output inductor, input capacitor bank, and output capacitor bank to be reduced in size and/or value. The power supply must be designed such that the frequency and its distribution over component tolerance, time and temperature causes minimal interference in RF stages, IF stages, PLL loops, mixers, etc.

#### **INDUCTOR SELECTION**

The output inductor is selected to meet the output voltage ripple requirements and minimize the converter's response time to the load transient. The inductor value determines the converter's ripple current, and the ripple voltage is a function of the ripple current. The ripple current and voltage are approximated by the following Equations 7 and 8, where ESR is the output capacitance ESR value.

$$I = \frac{V_{IN} - V_{OUT}}{F_{SW} \cdot L} \cdot \frac{V_{OUT}}{V_{IN}}$$

(EQ. 7)

$$\Delta V_{OUT} = \Delta I \times ESR$$

(Eq. 8)

Increasing the value of inductance reduces the ripple current and voltage. However, the large inductance value reduces the converter's response time to a load transient (and usually increases the DCR of the inductor, which decreases the efficiency). Increasing the switching frequency (F<sub>SW</sub>) for a given inductor also reduces the ripple current and voltage.

One of the parameters limiting the converter's response to a load transient is the time required to change the inductor current. Given a sufficiently fast control loop design, the ISL6446 will provide either 0% or 100% duty cycle in response to a load transient. The response time is the time required to slew the inductor current from an initial current value to the transient current level. During this interval, the difference between the inductor current and the transient current level must be supplied by the output capacitor. Minimizing the response time can minimize the output capacitance required.

The response time to a transient is different for the application of load and the removal of load. The following Equations give the approximate response time interval for application and removal of a transient load:

$$t_{RISE} = \frac{L_{OUT} \times I_{TRAN}}{V_{IN} - V_{OUT}}$$

(EQ. 9)

$$t_{FALL} = \frac{L_{OUT} \times I_{TRAN}}{V_{OUT}}$$

(EQ. 10)

where: I<sub>TRAN</sub> is the transient load current step, t<sub>RISE</sub> is the response time to the application of load, and t<sub>FALL</sub> is the response time to the removal of load. With a +5V input source, the worst case response time can be either at the application or removal of load and dependent upon the output voltage setting. Be sure to check both of these equations at the minimum and maximum output levels for the worst case response time.

Finally, check that the inductor I<sub>sat</sub> rating is sufficiently above the maximum output current (DC load plus ripple current).

#### **OUTPUT CAPACITOR SELECTION**

An output capacitor is required to filter the output and supply the load transient current. The filtering requirements are a function of the switching frequency and the ripple current. The load transient requirements are a function of the slew rate (di/dt) and the magnitude of the transient load current. These requirements are generally met with a mix of capacitors and careful layout.

Modern microprocessors produce transient load rates above 1A/ns. High frequency capacitors initially supply the transient and slow the current load rate seen by the bulk capacitors. The bulk filter capacitor values are generally determined by the ESR (effective series resistance) and voltage rating requirements rather than actual capacitance requirements.

High frequency decoupling capacitors should be placed as close to the power pins of the load as physically possible. Be careful not to add inductance in the circuit board wiring that could cancel the usefulness of these low inductance components. Consult with the manufacturer of the load on specific decoupling requirements. Keep in mind that not all applications have the same requirements; some may need many ceramic capacitors in parallel; others may need only one.

Use only specialized low-ESR capacitors intended for switching-regulator applications for the bulk capacitors. The bulk capacitor's ESR will determine the output ripple voltage and the initial voltage drop after a high slew-rate transient. An aluminum electrolytic capacitor's ESR value is related to the case size with lower ESR available in larger case sizes. However, the equivalent series inductance (ESL) of these capacitors increases with case size and can reduce the usefulness of the capacitor to high slew-rate transient loading. Unfortunately, ESL is not a specified parameter. Work with your capacitor supplier and measure the capacitor's impedance with frequency to select a suitable component. In most cases, multiple electrolytic capacitors of small case size perform better than a single large case capacitor.

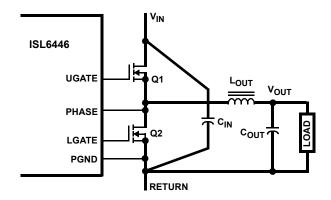

#### INPUT CAPACITOR SELECTION

Use a mix of input bypass capacitors to control the voltage overshoot across the MOSFETs. Use small ceramic capacitors for high frequency decoupling and bulk capacitors to supply the current needed each time Q1 (upper FET) turns on. Place the small ceramic capacitors physically close to the MOSFETs and between the drain of Q1 and the source of Q2 (lower FET).

The important parameters for the bulk input capacitor are the voltage rating and the RMS current rating. For reliable operation, select the bulk capacitor with voltage and current ratings above the maximum input voltage and largest RMS current required by the circuit. The capacitor voltage rating should be at least 1.25 times greater than the maximum input voltage and a voltage rating of 1.5 times is a conservative guideline. The RMS current rating requirement for the input capacitor of a buck regulator is approximately 1/2 the DC load current.

#### **SWITCHER MOSFET SELECTION**

$\rm V_{IN}$  for the ISL6446 has a wide operating voltage range allowed, so both FETs should have a source-drain breakdown voltage ( $\rm V_{DS}$ ) above the maximum supply voltage expected; 20V or 30V are typical values available.

The ISL6446 gate drivers (UGATE $_{x}$  and LGATE $_{x}$ ) were designed to drive single FETs (for up to ~10A of load current) or smaller dual FETs (up to 4A). Both sets of drivers are sourced by the internal VCC regulator (unless  $V_{IN} = V_{CC} = 5V$ , in which case the gate driver current comes from the external 5V supply). The maximum current of the regulator ( $I_{CC\_max}$ ) is listed in the "Electrical Specifications" Table on page 6; this may limit how big the FETs can be. In addition, the power dissipation of the regulator is a major contributor to the overall IC power dissipation (especially as  $C_{in}$  of the FET or  $V_{IN}$  or  $F_{SW}$  increases).

Since  $V_{CC}$  is around 5V, that affects the FET selection in two ways. First, the FET gate-source voltage rating ( $V_{GS}$ ) can be as low as 12V (this rating is usually consistent with the 20V or 30V breakdown chosen above). Second, the FETs must have a low threshold voltage (around 1V), in order to have its  $r_{DS(ON)}$  rating at  $V_{GS}$  = 4.5V in the  $10m\Omega$  to  $40m\Omega$  range that is typically used for these applications. While some FETs are also rated with gate voltages as low as 2.7V, with typical thresholds under 1V, these can cause application problems. As LGATE shuts off the lower FET, it does not take much ringing in the LGATE signal to turn the lower FET back on, while the Upper FET is starting to turn on, causing some shoot-through current. Therefore, avoid FETs with thresholds below 1V.

If the power efficiency of the system is important, then other FET parameters are also considered. Efficiency is a measure of power losses from input to output, and it contains two major components: losses in the IC (mostly in the gate drivers) and losses in the FETs. For low duty cycle applications (such as 12V in to 1.5V out), the upper FET is usually chosen for low gate charge, since switching losses are key, while the lower FET is chosen for low  $r_{DS(ON)}$ , since it is on most of the time. For high duty cycles (such as 5.0V in to 3.3V out), the opposite may be true.

#### **Feedback Compensation Equations**

This section highlights the design consideration for a voltage mode controller requiring external compensation. To address a broad range of applications, a type-3 feedback network is recommended (see Figure 25).

FIGURE 25. COMPENSATION CONFIGURATION FOR ISL6446 CIRCUIT

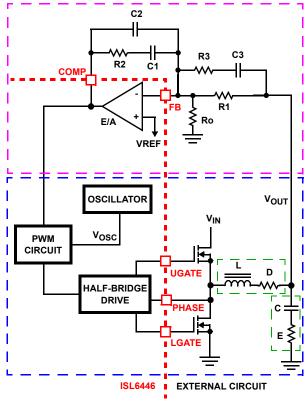

Figure 26 highlights the voltage-mode control loop for a synchronous-rectified buck converter, applicable to the ISL6446 circuit. The output voltage ( $V_{OUT}$ ) is regulated to the reference voltage,  $V_{REF}$ . The error amplifier output (COMP pin voltage) is compared with the oscillator (OSC) modified sawtooth wave to provide a pulse-width modulated wave with an amplitude of  $V_{IN}$  at the PHASE node. The PWM wave is smoothed by the output filter (L and C). The output filter capacitor bank's equivalent series resistance is represented by the series resistor E.

The modulator transfer function is the small-signal transfer function of  $V_{OUT}/V_{COMP}$ . This function is dominated by a DC gain, given by  $d_{MAX}V_{IN}/V_{OSC}$ , and shaped by the output filter, with a double pole break frequency at  $F_{LC}$  and a zero at  $F_{CE}$ . For the purpose of this analysis, L and D represent the channel inductance and its DCR, while C and E represent the total output capacitance and its equivalent series resistance.

FIGURE 26. VOLTAGE-MODE BUCK CONVERTER COMPENSATION **DESIGN**

$$F_{LC} = \frac{1}{2\pi \cdot \sqrt{L \cdot C}}$$

(EQ. 11)

$$F_{CE} = \frac{1}{2\pi \cdot C \cdot E}$$

(EQ. 12)

The compensation network consists of the error amplifier (internal to the ISL6446) and the external R1-R3, C1-C3 components. The goal of the compensation network is to provide a closed loop transfer function with high OdB crossing frequency (F<sub>0</sub>; typically 0.1 to 0.3 of F<sub>SW</sub>) and adequate phase margin (better than 45°). Phase margin is the difference between the closed loop phase at  $F_{\mbox{\scriptsize OdB}}$  and 180°. The equations that follow relate the compensation network's poles, zeros and gain to the components (R1, R2, R3, C1, C2, and C3) in Figure 26. Use the following guidelines for locating the poles and zeros of the compensation network:

1. Select a value for R1 (1k $\Omega$  to 5k $\Omega$ , typically). Calculate the value for R2 for desired converter bandwidth (F<sub>0</sub>). If setting the output voltage via an offset resistor connected to the FB pin, Ro in Figure 26, the design procedure can be followed as presented in Equation 13.

$$R2 = \frac{V_{OSC} \cdot R1 \cdot F_0}{d_{MAX} \cdot V_{IN} \cdot F_{LC}} \tag{EQ. 13}$$

16

2. Calculate C1 such that  $F_{Z1}$  is placed at a fraction of the  $F_{LC}$ , at 0.1 to 0.75 of F<sub>LC</sub> (to adjust, change the 0.5 factor to desired number). The higher the quality factor of the output filter and/or the higher the ratio  $F_{CE}/F_{LC}$ , the lower the  $F_{Z1}$  frequency (to maximize phase boost at F<sub>LC</sub>).

$$C1 = \frac{1}{2\pi \cdot R2 \cdot 0.5 \cdot F_{LC}}$$

(EQ. 14)

3. Calculate C2 such that FP1 is placed at FCE.

$$C2 = \frac{C1}{2\pi \cdot R2 \cdot C1 \cdot F_{CF} - 1}$$

(EQ. 15)

4. Calculate R3 such that F<sub>Z2</sub> is placed at F<sub>LC</sub>. Calculate C3 such that  $F_{\mbox{\footnotesize{P2}}}$  is placed below  $F_{\mbox{\footnotesize{SW}}}$  (typically, 0.5 to 1.0 times  $F_{\mbox{\footnotesize{SW}}}).$ F<sub>SW</sub> represents the switching frequency. Change the numerical factor to reflect desired placement of this pole. Placement of F<sub>P2</sub> lower in frequency helps reduce the gain of the compensation network at high frequency, in turn reducing the HF ripple component at the COMP pin and minimizing resultant duty cycle jitter.

It is recommended a mathematical model is used to plot the loop response. Check the loop gain against the error amplifier's open-loop gain. Verify phase margin results and adjust as necessary. The following equations describe the frequency response of the modulator (G<sub>MOD</sub>), feedback compensation (GFB) and closed-loop response (GCL):

$$G_{MOD}(f) = \frac{d_{MAX} \cdot V_{IN}}{V_{OSC}} \cdot \frac{1 + s(f) \cdot E \cdot C}{1 + s(f) \cdot (E + D) \cdot C + s^2(f) \cdot L \cdot C}$$

(Eq. 17)

$$\begin{split} G_{FB}(f) &= \frac{1+s(f)\cdot R2\cdot C1}{s(f)\cdot R1\cdot (C1+C2)}\cdot \\ &\cdot \frac{1+s(f)\cdot (R1+R3)\cdot C3}{(1+s(f)\cdot R3\cdot C3)\cdot \left(1+s(f)\cdot R2\cdot \left(\frac{C1\cdot C2}{C1+C2}\right)\right)} \end{split} \tag{EQ. 18}$$

$$G_{CL}(f) = G_{MOD}(f) \cdot G_{FB}(f)$$

(EQ. 19)

where:

$s(f) = 2\pi \cdot f \cdot i$

#### **COMPENSATION BREAK FREQUENCY EQUATIONS**

$$F_{Z1} = \frac{1}{2\pi \cdot R2 \cdot C1}$$

(EQ. 20)

$$F_{Z2} = \frac{1}{2\pi \cdot (R1 + R3) \cdot C3}$$

(EQ. 21)

$$F_{P1} = \frac{1}{2\pi \cdot R2 \cdot \frac{C1 \cdot C2}{C1 + C2}}$$

(EQ. 22)

$$F_{P2} = \frac{1}{2\pi \cdot R3 \cdot C3}$$

(EQ. 23)

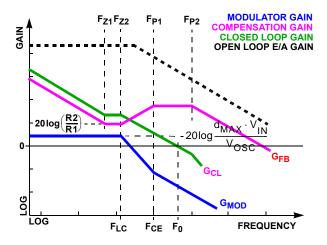

Figure 27 shows an asymptotic plot of the DC/DC converter's gain vs frequency. The actual Modulator Gain has a high gain peak dependent on the quality factor (Q) of the output filter, which is not shown. Using the previously mentioned guidelines should yield a compensation gain similar to the curve plotted. The open loop error amplifier gain bounds the compensation gain. Check the compensation gain at  $F_{P2}$  against the capabilities of the error amplifier. The closed loop gain,  $G_{CL}$ , is constructed on the log-log graph of Figure 27 by adding the modulator gain,  $G_{MOD}$  (in dB), to the feedback compensation gain,  $G_{FB}$  (in dB). This is equivalent to multiplying the modulator transfer function and the compensation transfer function and then plotting the resulting gain.

FIGURE 27. ASYMPTOTIC BODE PLOT OF CONVERTER GAIN

A stable control loop has a gain crossing with close to a  $-20 \, \text{dB/decade}$  slope and a phase margin greater than  $45\,^\circ$ . Include worst case component variations when determining phase margin. The mathematical model presented makes a number of approximations and is generally not accurate at frequencies approaching or exceeding half the switching frequency. When designing compensation networks, select target crossover frequencies in the range of 10% to 30% of the switching frequency,  $F_{SW}$ .

#### **Layout Considerations**

As in any high frequency switching converter, layout is very important. Switching current from one power device to another can generate voltage transients across the impedances of the interconnecting bond wires and circuit traces. These interconnecting impedances should be minimized by using wide, short printed circuit traces. The critical components should be located as close together as possible using ground plane construction or single point grounding.

Figure 28 shows the critical power components of the converter. To minimize the voltage overshoot, the interconnecting wires indicated by heavy lines should be part of ground or power plane in a printed circuit board. The components shown in Figure 28 should be located as close together as possible. Please note that the capacitors  $C_{IN}$  and  $C_{OUT}$  each represent numerous physical capacitors. Locate the ISL6446 within 1 inch of the MOSFETs, Q1 and Q2. The circuit traces for the MOSFETs' gate and source connections from the ISL6446 must be sized to handle up to 2A peak current.

FIGURE 28. PRINTED CIRCUIT BOARD POWER AND GROUND PLANES OR ISLANDS

FIGURE 29. PRINTED CIRCUIT BOARD POWER AND GROUND PLANES OR ISLANDS