Data Sheet No. PD60194 revD IR21592(S) & (PbF) IR21593(S) & (PbF)

### **DIMMING BALLAST CONTROL IC**

#### **Features**

- Ballast control and half-bridge driver in one IC

- Transformer-less lamp power sensing

- Closed-loop lamp power control

- Closed-loop preheat current control

- Programmable preheat time

- Programmable preheat current

- Lamp ignition detection

- Programmable ignition-to-dim time

- 0.5 to 5VDC dimming control input

- Min and max lamp power adjustments

- Programmable minimum frequency

- Internal current sense blanking

- Full lamp fault protection

- Brown-out protection

- Automatic restart

- Micro-power startup

- Zener clamped Vcc

- Over-temperature protection

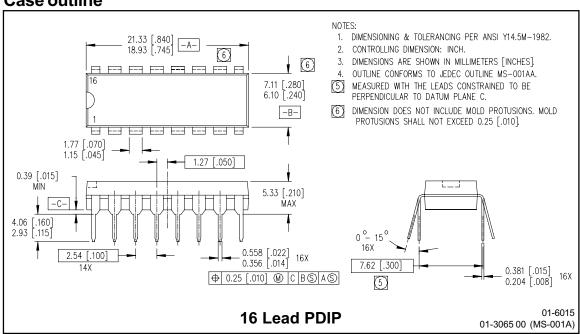

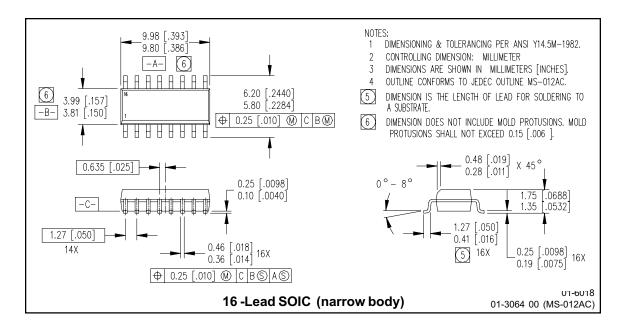

- 16-pin DIP and SOIC package types

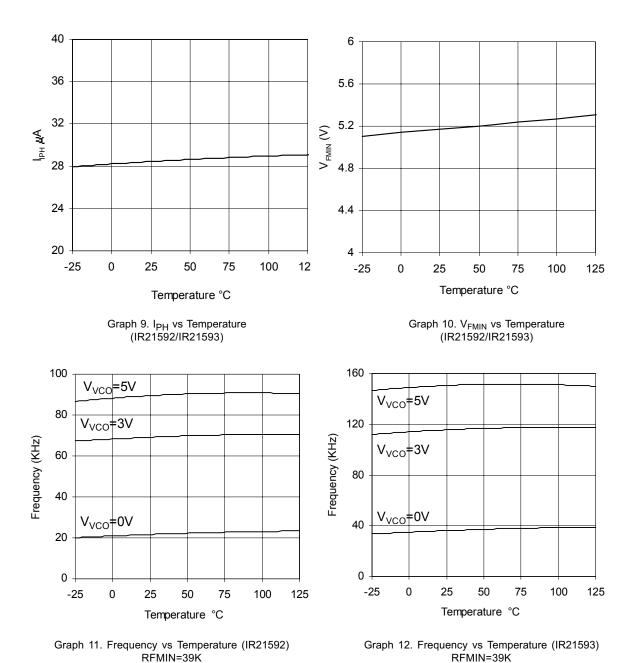

| Parameter | IR21592  | IR21593  |

|-----------|----------|----------|

| Deadtime  | 1.8us    | 1.0us    |

| Frequency | See      | See      |

| Range     | Graph 11 | Graph 12 |

### **Description**

Description: The IR21592/IR21593 are complete dimming ballast controllers and 600V Packages half-bridge drivers all in one IC. The architecture includes phase control for transformer-less lamp power sensing and regulation which minimizes changes needed to adapt non-dimming ballasts for dimming. Externally programmable features such as preheat time and current, ignition-to-dim time, and a complete dimming interface with minimum and maximum settings provide a high degree of flexibility for the ballast design engineer. Protection from failure of a lamp to strike, filament failures, thermal overload, or lamp failure during normal operation, as well as an automatic restart function, have been included in the design. The heart of this control IC is a voltagecontrolled oscillator with externally programmable minimum frequency. The IR21592/ IR21593 are available in both 16 pin DIP and 16 pin narrow body SOIC packages.

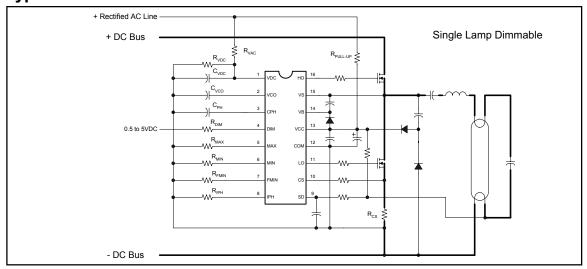

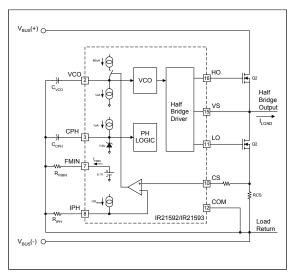

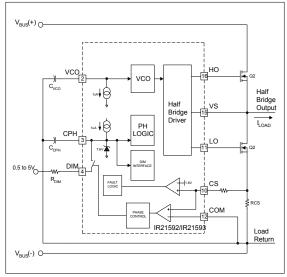

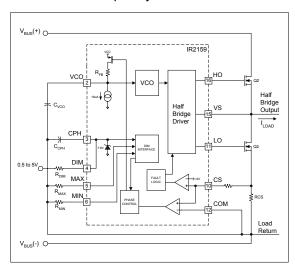

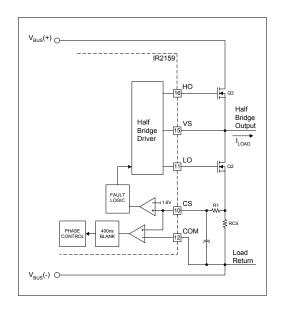

### Typical Connection

International

IOR Rectifier

### **Absolute Maximum Ratings**

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to COM, all currents are defined positive into any lead. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.

| Symbol            | Definition                                         | Min.          | Max.                  | Units                |        |

|-------------------|----------------------------------------------------|---------------|-----------------------|----------------------|--------|

| V <sub>B</sub>    | High side floating supply voltage                  | -0.3          | 625                   |                      |        |

| Vs                | High side floating supply offset voltage           |               | V <sub>B</sub> - 25   | V <sub>B</sub> + 25  | V      |

| V <sub>HO</sub>   | High side floating output voltage                  |               | V <sub>S</sub> - 0.3  | V <sub>B</sub> + 0.3 | T      |

| V <sub>LO</sub>   | Low side output voltage                            | -0.3          | V <sub>CC</sub> + 0.3 | Ī                    |        |

| I <sub>OMAX</sub> | Maximum allowable output current (either of        | output)       | -500                  | 500                  | mA     |

|                   | due to external power transistor miller effect     | ct            |                       |                      | IIIA   |

| V <sub>VCO</sub>  | Voltage controlled oscillator input voltage        |               | -0.3                  | 6.0                  | V      |

| I <sub>CPH</sub>  | CPH current                                        |               | -5                    | 5                    | mA     |

| V <sub>IPH</sub>  | IPH voltage                                        |               | -0.3                  | 5.5                  |        |

| $V_{DIM}$         | Dimming control pin input voltage                  |               | -0.3                  | 5.5                  |        |

| V <sub>MAX</sub>  | Maximum lamp power setting pin input volt          | -0.3          | 5.5                   | V                    |        |

| V <sub>MIN</sub>  | Minimum lamp power setting pin input volta         | -0.3          | 5.5                   | ]                    |        |

| V <sub>CS</sub>   | Current sense input voltage                        | -0.3          | 5.5                   |                      |        |

| I <sub>SD</sub>   | Shutdown pin current                               |               | -5                    | 5                    |        |

| Icc               | Supply current (note 1)                            |               | _                     | 25                   | mA     |

| dV/dt             | Allowable offset voltage slew rate                 |               | -50                   | 50                   | V/ns   |

| PD                | Package power dissipation @ T <sub>A</sub> ≤ +25°C | (16 pin DIP)  | _                     | 1.60                 | W      |

|                   | $P_D = (T_{JMAX} - T_A)/Rth_{JA}$                  | (16 pin SOIC) | _                     | 1.25                 |        |

| Rth <sub>JA</sub> | Thermal resistance, junction to ambient            | (16 pin DIP)  | _                     | 75                   | °C/W   |

|                   |                                                    | (16 pin SOIC) | _                     | 115                  | - C/VV |

| TJ                | Junction temperature                               |               | -55                   | 150                  |        |

| TS                | Storage temperature                                | -55           | 150                   | °C                   |        |

| TL                | Lead temperature (soldering, 10 seconds)           | _             | 300                   |                      |        |

Note 1: This IC contains a zener clamp structure between the chip  $V_{CC}$  and COM which has a nominal breakdown voltage of 15.6V ( $V_{CLAMP}$ ). Please note that this supply pin should not be driven by a DC, low impedance power source greater than the diode clamp voltage ( $V_{CLAMP}$ ) as specified in the Electrical Characteristics section.

### **Recommended Operating Conditions**

For proper operation the device should be used within the recommended conditions.

| Symbol             | Definition                                               | Min.                  | Max.          | Units |

|--------------------|----------------------------------------------------------|-----------------------|---------------|-------|

| V <sub>BS</sub>    | High side floating supply voltage                        | V <sub>CC</sub> - 0.7 | VCLAMP        |       |

| Vs                 | Steady state high side floating supply offset voltage    | -1                    | 600           | V     |

| Vcc                | Supply voltage                                           | V <sub>CCUV+</sub>    | VCLAMP (15.6) |       |

| Icc                | Supply current                                           | note 2                | 10            | mA    |

| V <sub>VCO</sub>   | VCO pin voltage                                          | 0                     | 5             |       |

| V <sub>DIM</sub>   | DIM pin voltage                                          | 0.5                   | 5.0           | V     |

| V <sub>MAX</sub>   | MAX pin current (note 3)                                 | -750                  | 0             | μΑ    |

| V <sub>MIN</sub>   | MIN pin voltage                                          | 1                     | 3             | V     |

| V <sub>BSMIN</sub> | Minimum required VBS voltage for proper HO functionality | _                     | 5             | V     |

| R <sub>FMIN</sub>  | Minimum frequency setting resistance                     | 10                    | 100           | kΩ    |

| I <sub>SD</sub>    | Shutdown pin current                                     | -1                    | 1             | mA    |

| ICS                | Current sensing pin current                              | -1                    | 1             | 111/4 |

| TJ                 | Junction temperature                                     | -40                   | 125           | °C    |

Note 2: Enough current should be supplied into the VCC lead to keep the internal 15.6V zener clamp diode on this lead regulating its voltage, V<sub>CLAMP</sub>.

Note 3: The MAX lead is a voltage-controlled current source. For optimum dim interface current mirror performance, this current should be kept between 0 and 750µA.

#### **Electrical Characteristics**

$V_{CC} = V_{BS} = V_{BIAS} = 14V + /-0.25V, \ V_{CS} = 0.5V, \ V_{SD} = 0.0V, \ R_{FMIN} = 40k, \ C_{VCO} = 10 \ nF, \ V_{DIM} = 0.0V, \ R_{MAX} = 33k, \ R_{MIN} = 56k, \ V_{CPH} = 0.0V, \ C_{LO,HO} = 1000pF, \ T_A = 25^{\circ}C \ unless \ otherwise \ specified.$

| Symbol             | Definition                                                             |         | Тур. | Max. | Units                 | Test Conditions        |

|--------------------|------------------------------------------------------------------------|---------|------|------|-----------------------|------------------------|

| Supply (           | Characteristics                                                        |         |      |      |                       |                        |

| V <sub>CCUV+</sub> | V <sub>CC</sub> supply undervoltage positive going 12.0 12.0 threshold |         | 12.5 | 13.0 | V                     |                        |

| Vcchys             | V <sub>CC</sub> supply undervoltage lockout hysteresis                 | 1.5     | 1.6  | 1.7  |                       |                        |

| IQCCUV             | UVLO mode quiescent current                                            | 70      | 200  | 330  |                       | V <sub>CC</sub> = 10V  |

| IQCCFLT            | Fault-mode quiescent current                                           | _       | 240  | _    | μΑ                    | SD=5V, CS=2V, or       |

|                    |                                                                        |         |      |      |                       | Tj > Tsb               |

| ICCFMIN            | V <sub>CC</sub> supply current @ FMIN (IR21592)                        | _       | 5.6  | _    |                       | V <sub>VCO</sub> = 0V  |

| ICCFMAX            |                                                                        |         | 6.0  | _    | mA                    | V <sub>VCO</sub> = 5V  |

| ICCFMIN            | V <sub>CC</sub> supply current @ FMIN (IR21593)                        | — 5.4 — |      |      | V <sub>VCO</sub> = 0V |                        |

| ICCFMAX            | V <sub>CC</sub> supply current @ FMAX (IR21593)                        | _       | 6.8  | _    |                       | V <sub>VCO</sub> = 5V  |

| V <sub>CLAMP</sub> | V <sub>CC</sub> zener shunt clamp voltage                              | 14.5    | 15.6 | 16.5 | V                     | I <sub>CC</sub> = 10mA |

International IOR Rectifier

| Symbol              | Definition                                  | Min.  | Тур. | Max. | Units | Test Conditions                                |

|---------------------|---------------------------------------------|-------|------|------|-------|------------------------------------------------|

| Floatin             | g Supply Characteristics                    |       |      |      |       |                                                |

| I <sub>BSFMIN</sub> | V <sub>BS</sub> supply current (low freq.)  | _     | 0    | _    |       | V <sub>VCO</sub> = 0V                          |

| IBSFMAX             | V <sub>BS</sub> supply current (high freq.) | _     | 30   | _    | μΑ    | V <sub>VCO</sub> = 5V                          |

| I <sub>LK</sub>     | Offset supply leakage current               | _     | _    | 50   |       | $V_B = V_S = 600V$                             |

| Oscilla             | tor I/O Characteristics                     |       |      |      |       |                                                |

| f <sub>VCO</sub>    | VCO frequency range (IR21592)               | 16.5  | 18   | 26   | ,     | VCO=0V, RFMIN=40KΩ                             |

|                     | (See graph 11)                              | 73    | 95   | 108  | l     | V <sub>VCO</sub> =5V, RFMIN=40KΩ               |

| f <sub>vco</sub>    | VCO frequency range (IR21593)               | _     | 30   | _    | kHz   | V <sub>VCO</sub> =0V, RFMIN=40KΩ               |

|                     | (See graph 12)                              | _     | 230  | _    | 1     | V <sub>VCO</sub> =5V, RFMIN=40KΩ               |

| d                   | Gate drive outputs duty cycle               | _     | 50   | _    | %     | V <sub>VCO</sub> = 2.5V                        |

| VVCOFLT             | Fault-mode VCO pin voltage (UVLO,           | _     | 5    | _    | V     |                                                |

|                     | shutdown, over-current/temp.)               |       |      |      |       |                                                |

| IVCOPH              | Preheat mode VCO pin discharge current      | _     | 1.0  | _    |       | VCPH=2.5V, VIPH=0.5V                           |

| IVCODIM             | Dim mode VCO pin discharge current          | _     | 16.0 | _    |       | V <sub>VCO</sub> =2.5V, VCPH=5.5V,             |

|                     |                                             |       |      |      | μΑ    | VIPH=0.5V, 1V Pulse at                         |

|                     |                                             |       |      |      |       | CS                                             |

| IVCOPK              | Amplitude control VCO pin charging current  | _     | 60   | _    | μΑ    | V <sub>CPH</sub> =0V, V <sub>CS</sub> =1V,     |

|                     |                                             |       |      |      |       | V <sub>IPH</sub> =0.5V, V <sub>VCO</sub> =2.5V |

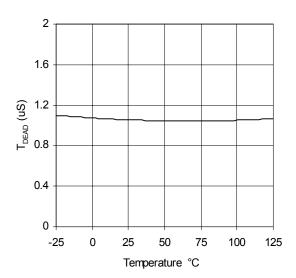

| tDTLO               | LO output deadtime (IR21592)                | _     | 1.8  |      |       |                                                |

| tDTHO               | HO output deadtime (IR21592)                | _     | 1.8  | _    | μs    | V <sub>VCO</sub> =0V, V <sub>MIN</sub> =1.5V,  |

| tDTLO               | LO output deadtime (IR21593)                | _     | 1.0  | _    |       | V <sub>IPH</sub> =0.5V                         |

| tDTH0               | HO output deadtime (IR21593)                | _     | 1.0  | -    |       |                                                |

| Gate D              | river Output Characteristics                |       |      |      |       |                                                |

| tr                  | Turn-on rise time                           | 48.5  | 120  | 180  | ne    |                                                |

| tf                  | Turn-off fall time                          | 24.25 | 65   | 145  | ns    |                                                |

**Electrical Characteristics (cont.)**  $V_{CC} = V_{BS} = V_{BIAS} = 14V + V_{CO} = 0.5V, V_{CS} = 0.5V, V_{SD} = 0.0V, R_{FMIN} = 40k, C_{VCO} = 10 nF, V_{DIM} = 0.0V, R_{MAX} = 33k, R_{MIN} = 56k, V_{TPH} = 0.0V, C_{LO,HO} = 1000pF, T_A = 25^{\circ}C unless otherwise specified.$

| Symbol                | Definition                                        | Min. | Тур. | Max.                | Units | Test Conditions                                           |

|-----------------------|---------------------------------------------------|------|------|---------------------|-------|-----------------------------------------------------------|

| Preheat               | Characteristics                                   |      |      |                     |       |                                                           |

|                       |                                                   |      |      |                     |       | 1 1 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2                   |

| ICPH                  | CPH pin charging current                          | 8.0  | 1.3  | 2.1                 | μΑ    | VCPH=VDIM=4.7V,                                           |

|                       |                                                   |      |      |                     |       | VCS=1.0V                                                  |

| VCPHIGN               | CPH pin ignition mode threshold voltage           | 4.3  | 5.0  | 5.7                 | V     | VCS=2.0V                                                  |

| VCPHCLMP              | CPH pin clamp voltage IPH pin DC source current   | _    | 10   | _                   |       | VCS=VDIM=VIPH=0V                                          |

| IIPH                  | IPH pin DC source current                         | _    | 25   | _                   | μΑ    | VCPH=VDIM=4.7V,<br>IIPH=1/RFMIN                           |

| VCSTHPH               | Peak preheat current regulation threshold         | _    | 0.7  | _                   | V     | RIPH=27K, VMIN=0V,<br>VCPH=0V, VCSTH =<br>(IIPH) x (RIPH) |

| VCPHFLT               | CPH pin voltage during UVLO or fault              | _    | 0.0  | _                   | V     | SD = 5V, or CS = 2V,<br>or Tj > TSD                       |

| Ignition              | Detection                                         |      |      |                     |       |                                                           |

| I <sub>IPHIGN+</sub>  | IPH source current (Vcs rising)                   | _    | 30   | _                   | μА    | VCS=0V, RIPH=18K,<br>VCPH>5.1V                            |

| I <sub>IPHIGN</sub> - | GN- IPH source current (Vcs falling)              |      | 27.5 | _                   |       | VCS =1.0V,<br>VCPH>5.1V                                   |

| Protect               | ion Characteristics                               |      |      |                     |       |                                                           |

| V <sub>SDTH+</sub>    | Rising shutdown pin threshold voltage             | 1.6  | 2.0  | 2.6                 |       | VCPH =VIPH=0V                                             |

| V <sub>CSTH</sub>     | Peak over current threshold                       | 1.2  | 1.6  | 1.9                 | \ \ \ | VCPH < 5V                                                 |

| V <sub>VDCTH+</sub>   | Rising VDC pin threshold voltage                  | _    | 5.1  |                     | 1     | VCPH=VCS=VSD=0V                                           |

| V <sub>SDHYS</sub>    | SD threshold hysteresis                           | _    | 150  |                     | mV    | VCPH=VIPH=0V                                              |

| V <sub>VDCHYS</sub>   | VDC threshold hysteresis                          | _    | 2.1  | _                   | V     | VCPH=VCS=VSD=0V                                           |

| V <sub>SDCLMP</sub>   | SD pin clamp voltage                              | _    | 7.6  | _                   | ]     | ISD = 100mA                                               |

| T <sub>SD</sub>       | Thermal shutdown junction temperature             | _    | 165  | _                   | °C    |                                                           |

| Phase C               | ontrol                                            |      |      |                     |       |                                                           |

| VCSTHZX               | Zero-crossing threshold voltage                   | _    | 0.0  | _                   | V     | VCPH =5.5V,VIPH=0.5V                                      |

| t <sub>Blank</sub>    | Zero-crossing internal blank time                 | 291  | 400  | 1030                | ns    | VCPH =5.5V,VIPH=0.5V                                      |

| `                     | g Interface                                       |      |      |                     |       |                                                           |

| VDIMOFF               | DIM pin offset voltage                            | _    | 0.5  | _                   |       |                                                           |

| $V_{MINMIN}$          | DIM minimum reference voltage (MIN pin) — 1.0 — V |      | V    | VCPH=5.5V,VIPH=0.5V |       |                                                           |

| V <sub>MINMAX</sub>   | DIM maximum reference voltage (MIN pin)           |      | 3.0  | _                   |       | VCPH =0.5V,VIPH=0.5V                                      |

|                       | n Frequency Setting                               |      |      |                     |       |                                                           |

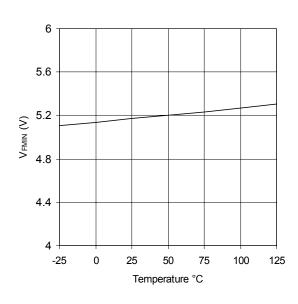

| V <sub>FMIN</sub>     | FMIN pin voltage during normal operation          | 4.6  | 5.1  | 6.25                | V     | VMIN=1.5V,VIPH=0.5V                                       |

| VFMINFLT              | FMIN pin voltage during fault mode                | _    | 0.0  | _                   | V     | SD = 5V, or CS = 2V,<br>or Tj > TSD                       |

International **ICR** Rectifier

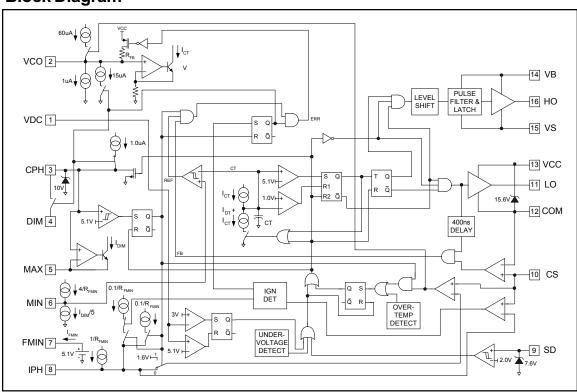

### **Block Diagram**

# **Lead Assignments & Definitions**

| Pin As   | ssignments | Pin # | Symbol | Description                           |

|----------|------------|-------|--------|---------------------------------------|

|          |            | 1     | VDC    | Line input voltage detection          |

|          |            | 2     | VCO    | Voltage controlled oscillator Input   |

| VDC 1 0  | 16 HO      | 3     | CPH    | Preheat timing input                  |

| VCO 2    | 15 VS      | 4     | DIM    | 0.5 to 5VDC dimming control input     |

|          |            | 5     | MAX    | Maximum lamp power setting            |

| CPH 3    | 14 VB      | 6     | MIN    | Minimum lamp power setting            |

| DIM 4    | 13 VCC     | 7     | FMIN   | Minimum frequency setting             |

| DIIVI [4 | 13 VCC     | 8     | IPH    | Peak preheat current reference        |

| MAX 5    | 12 COM     | 9     | SD     | Shutdown input                        |

| l 🗐      |            | 10    | CS     | Current sensing input                 |

| MIN 6    | 11 LO      | 11    | LO     | Low-side gate driver output           |

| FMIN 7   | 10 CS      | 12    | COM    | IC power & signal ground              |

|          |            | 13    | VCC    | Logic & low-side gate driver supply   |

| IPH 8    | 9 SD       | 14    | VB     | High-side gate driver floating supply |

|          |            | 15    | VS     | High voltage floating return          |

|          |            | 16    | НО     | High-side gate driver output          |

International

TOR Rectifier

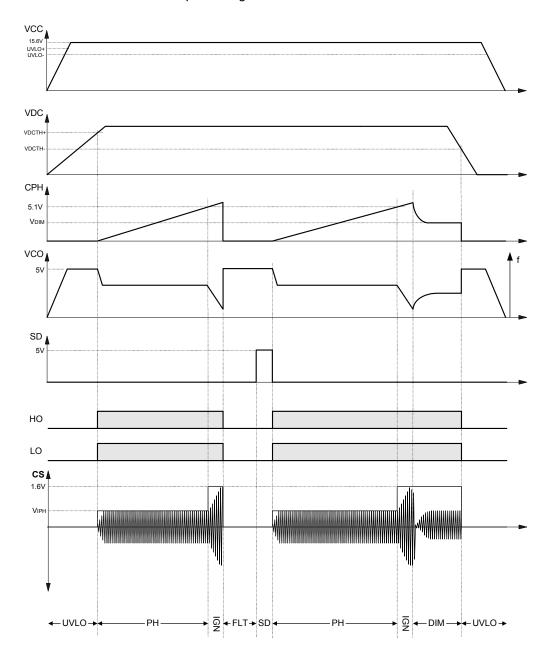

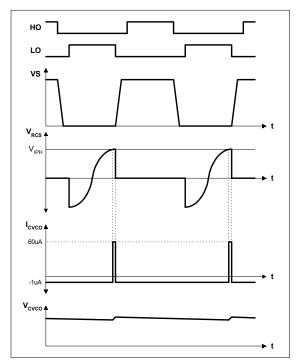

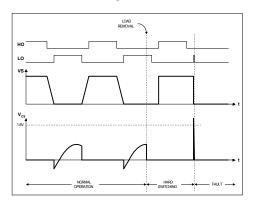

# **Timing Diagram**

Non-strike fault condition with lamp exchange

# International TOR Rectifier

# IR21592/IR21593(S)&(PbF)

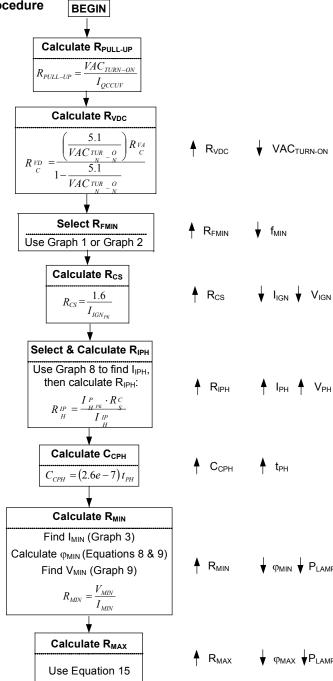

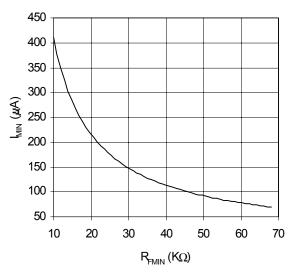

**External Components Selection Procedure**

(Note:

Please refer to

"Typical Connection"

diagram, page 1)

Set  $R_{VAC}$  and  $R_{VDC}$  such that the voltage on pin VDC will exceed 5.1 volts at the desired line turn-on voltage.

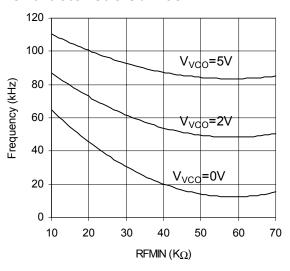

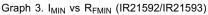

The minimum operating frequency must be lower than  $f_{100\%}$  of  $f_{IGN}$  (whichever is lower).  $R_{FMIN}$  also programs  $I_{MIN}$  and  $I_{IPH}$ , so  $R_{FMIN}$  must be set first.

$R_{\text{CS}}$  sets the maximum ignition current which corresponds to the maximum ignition voltage across the lamp.

The voltage at pin IPH is the reference for amplitude current control during preheat mode.  $R_{\text{IPH}}$  must be set after  $R_{\text{FMIN}}$ .

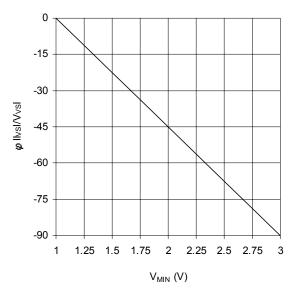

During preheat, an internal 1.3  $\mu$ A current source at pin CPH charges external capacitor CCPH. Preheat mode ends when VCPH exceeds 5.1 volts

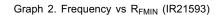

$R_{\text{MIN}}$  sets the lower phase boundary corresponding to minimum lamp power when  $V_{\text{DIM}}=0$  volts.  $R_{\text{MIN}}$  must be set after  $R_{\text{FMIN}}.$

$R_{\text{MAX}}$  sets the upper phase boundary corresponding to maximum lamp power when  $V_{\text{DIM}} = 5$  volts.  $R_{\text{MAX}}$  must be set after  $R_{\text{FMIN}}$  and  $R_{\text{MIN}}$ .

International

TOR Rectifier

### **Characteristic Curves**

200 160 V<sub>VCO</sub>=5∀ Frequency (kHz) 120 V<sub>VCO</sub>=2V 80 V<sub>VCO</sub>=0V 40 0 10 20 30 40 50 60 70 RFMIN ( $K_{\Omega}$ )

Graph 1. Frequency vs R<sub>FMIN</sub> (IR21592)

Graph 4. I<sub>IPH</sub> vs R<sub>FMIN</sub> (IR21592/IR21593)

30

25

RFMIN=39K

RFMIN=33K

RFMIN=27K

RFMIN=27K

RFMIN=16K

RFMIN=10K

SSTREET

SSTREET

RFMIN=10K

RFMIN=10K

SSTREET

SSTREET

RFMIN=20K

RFMIN=10K

RFMIN=10K

RFMIN=10K

SSTREET

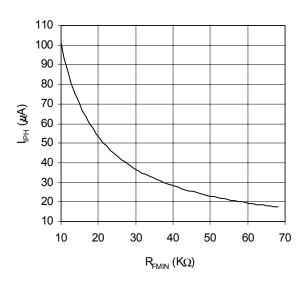

Graph 5.  $\phi$  IIVS/VVSI vs VMIN (IR21592/IR21593)

Graph 7. I<sub>CPH</sub> vs Temperature (IR21592/IR21593)

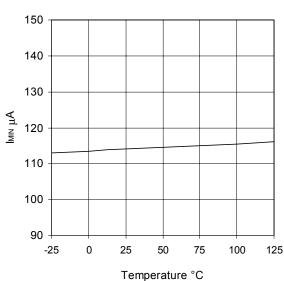

Graph 8. I<sub>MIN</sub> vs Temperature (IR21592/IR21593)

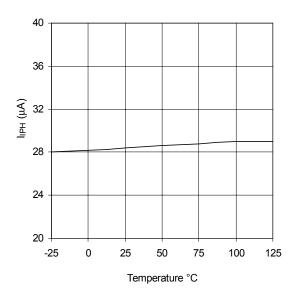

Graph 13. I<sub>IPH</sub> vs Temperature (IR21592/IR21593)

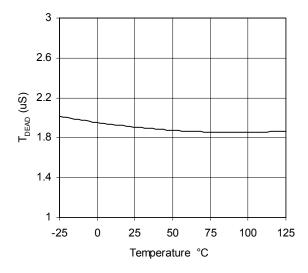

Graph 15. TDEAD vs Temperature (IR21592)

Graph 14. V<sub>FMIN</sub> vs Temperature (IR21592/IR21593)

Graph 16. TDEAD vs Temperature (IR21593)

International

TOR Rectifier

#### **Functional Description**

#### **Phase Control**

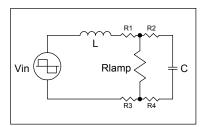

To understand phase control, a simplified model for the ballast output stage is used (Figure 1). The lamp and filaments are replaced with resistors, with the lamp inserted between the filament resistors (R1, R2, R3 and R4).

Figure 1, Dimming ballast output stage.

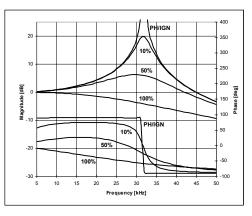

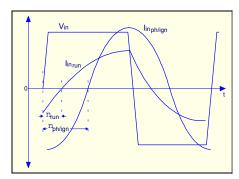

During preheat and ignition (Figure 2), the circuit is a high-Q series LC with a strong input current to input voltage phase inversion from +90 to -90 degrees at the resonance frequency. For operating frequencies slightly above resonance and higher, the phase is fixed at -90 degrees for the duration of preheat and ignition. During dimming, the circuit is an L in series with a parallel R and C, with a weak phase inversion at high lamp power and a strong phase inversion at low lamp power.

Figure 2, Typical output stage transfer function for different lamp power levels.

In the time domain (Figure 3), the input current is shifted -90 degrees from the input half-bridge voltage during preheat and ignition, and somewhere between 0 and -90 degrees after ignition during running. Zero phase-shift corresponds to maximum power.

Figure 3, Typical ballast output stage waveforms.

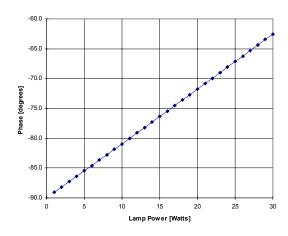

When the phase is calculated and plotted versus lamp power (Figure 4), the result is a linear dimming curve, even down to ultra-low light levels where the resistance of the lamp can change by orders of magnitude.

# International TOR Rectifier

# IR21592/IR21593(S)&(PbF)

Figure 4, Lamp power vs. phase of output stage.

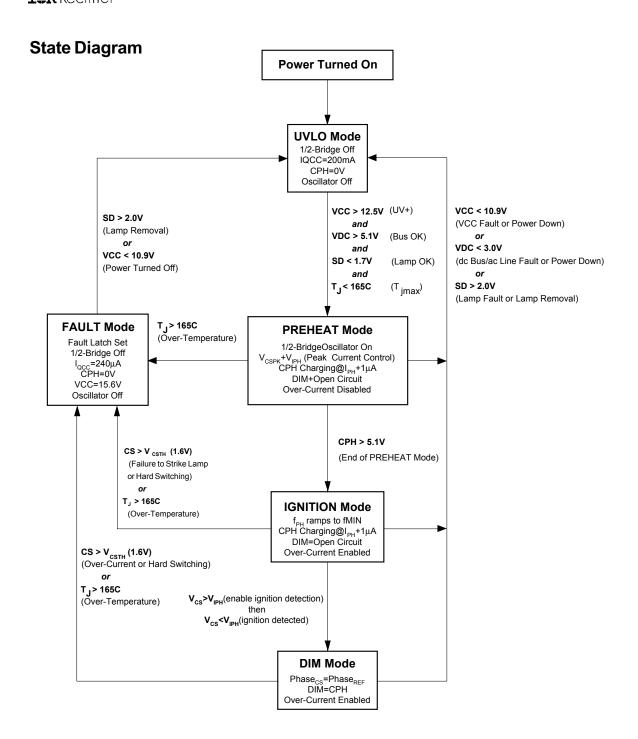

#### Under-voltage Lock-Out (UVLO)

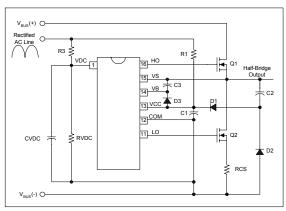

The IR21592/IR21593 undervoltage lock-out is designed to maintain an ultra low quiescent current of less than 200uA, while guaranteeing the IC is fully functional before the high and low side output drivers are activated. Figure 5 shows an efficient supply voltage using the start-up current of the IR21592/IR21593 together with a charge pump from the ballast output stage (R1, C1, C2, D1 and D2).

Figure 5, Typical application of start-up circuitry.

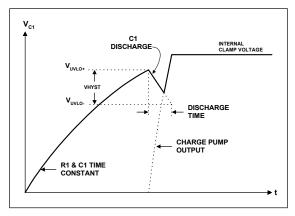

The start-up capacitor (C1) is charged by current through resistor (R1) minus the start-up current drawn by the IC. This resistor is typically chosen to provide 2X the maximum start-up current at low line to guarantee start-up under the worst case condition. Once the capacitor voltage reaches the start-up threshold, and, the voltage on pin VDC is above 5.1V (see Brown-out Protection), the IC turns on and HO and LO begin to oscillate. The capacitor begins to discharge due to the increase in IC operating current (Figure 6).

Figure 6, Start-up capacitor (C1) voltage.

During the discharge cycle, the rectified current from the charge pump charges the capacitor above the minimum operating voltage of the device and the charge pump and internal 15.6V zener clamp of the IC take over as the supply voltage. The start-up capacitor and snubber capacitor must be selected such that worst case IC conditions are satisfied. A bootstrap diode (D3) and supply capacitor (C3) comprise the supply voltage for the high side driver circuitry. To guarantee that the high-side supply is charged up before the first pulse on pin HO, the first pulse from the output drivers comes from the LO pin. During UVLO, the high and low side driver outputs are low, pin VCO is pulled-up internally to 5V resetting the starting frequency to the maximum, and pin CPH is short-circuited internally to COM resetting the preheat time.

#### **Brown-out Protection**

In addition to the voltage on VCC being above the start-up threshold, pin VDC must also be above 5.1V for HO and LO to begin oscillating. A voltage divider (R3,RVDC) from the rectified AC line connected to pin VDC measures the rectified AC line input voltage to the ballast and programs the turn-on and turn-off line voltages. A filter capacitor (CVDC) is also connected to pin VDC that must be chosen such that the ripple is low enough and the lower turn-off threshold of 3V is not crossed during normal line conditions. This detection is necessary due to the possibility of the lamp extinguishing during low-line conditions before the IC is properly reset. Should a brownout occur, the DC bus can drop to a level below the minimum required for the tank circuit to maintain the necessary lamp voltage. This detection will insure a clean turn-off before the DC bus drops too low and properly resets the IC to the preheat mode when the line returns.

#### Preheat (PH)

The IR21592/IR21593 enters preheat mode when VCC exceeds the UVLO+ threshold and VDC exceeds 5.1V. HO and LO begin to oscillate at the maximum operating frequency with 50% duty cycle and at the internally set dead-time of 2us (IR21592) or 1µs (IR21593). Pin CPH is disconnected from COM and an internal 1uA current source (Figure 7) charges the external timing capacitor on CPH linearly.

Figure 7, IR21592/IR21593 preheat circuitry.

An internal 1uA current source slowly discharges the external capacitor on pin VCO and the voltage on pin VCO begins to decrease. This decreases the frequency, which, for operating frequencies above resonance, increases the load current. When the peak voltage measured on pin CS. produced by a portion of the load current flowing through an external sense resistor (RCS), exceeds the voltage level on pin IPH, a 60uA internal current source is connected to pin VCO and the capacitor charges (Figure 8). This forces the frequency to increase and the load current to decrease. When the voltage on pin CS decreases below the voltge on pin IPH, the 60uA current source is disconnected and the frequency decreases again.

Figure 8, Peak load current regulation timing diagram.

This feedback keeps the peak preheat current regulated to the user-programmable setting on pin IPH for the duration of the preheat time. An internal current source connected to an external resistor on pin IPH sets a voltage reference for the peak pre-heat current. The pre-heat time continues until the voltage on pin CPH exceeds 5V.

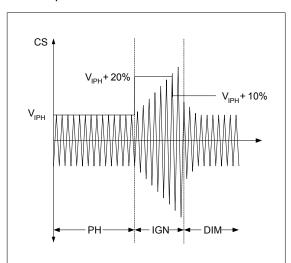

#### Ignition (IGN)

The IR21592/IR21593 enters ignition mode when the voltage on pin CPH exceeds 5V. The peak current regulation reference voltage is disconnected from the user-programmable setting on pin IPH and is connected to a higher internal threshold of 1.6V (Figure 9).

Figure 9, IR21592/IR21593 ignition circuitry.

The ignition ramp is then initiated as the capacitor on pin VCO discharges linearly through an internal 1uA current source. The frequency decreases linearly towards the resonance frequency of the high-Q ballast output stage, causing the lamp voltage and load current to increase (Figure 10). The frequency continues to decrease until the lamp ignites or the current limit of the IR21592/IR21593 is reached. If the current limit is reached, the IR21592/IR21593 enters FAULT mode. The 1.6V threshold together with the external current sensing resistor on pin CS determine the maximum allowable peak ignition current (and therefore peak ignition voltage) of the ballast output stage. The peak ignition current must not exceed the maximum allowable current ratings of the output stage MOSFETs or IGBTs, and, the resonant inductor must not saturate at

To prevent a "flash" across the lamp during ignition at low dim settings, an ignition detection

International

TOR Rectifier

circuit measures the voltage at the CS pin and compares it against the voltage at the IPH pin. During the rising ignition ramp, the voltage at the IPH pin is increased to 20% above its value

Figure 10, IR21592/IR21593 ignition detection.

during preheat mode. When the voltage on the CS pin exceeds this voltage, the voltage on the IPH pin is decreased to VIPH Pre-Heat +10% and the ignition detection circuit is then active (See Figure 10). When the lamp ignites, the voltage on the CS pin will then fall below the voltage on the IPH pin and the IC enters DIM Mode and the phase control loop is closed. In order for the ignition detection circuit to function properly and for the IC to enter DIM mode, the voltage on the CS pin must first rise above VIPH Pre-Heat + 20% during the ignition ramp to activate the circuit, and then decrease below VIPH Pre-Heat +10% when the lamp ignites.

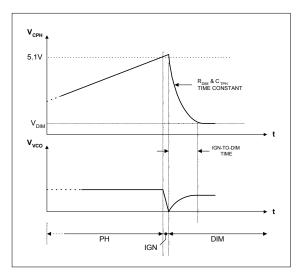

#### Ignition-to-Dim (IGN-to-DIM)

When the IR21592/IR21593 enters dim mode, the phase control loop is closed and the phase of the

load current is regulated against the user control input on pin DIM. To control the rate at which the dim setting changes from maximum brightness to the user setting (IGN-TO-DIM time, Figure 11).

Figure 11, IR21592/IR21593 ignition timing diagram.

pin DIM is connected internally to pin CPH when the IR21592/IR21593 enters DIM mode. The resistor on pin DIM (RDIM) discharges the capacitor on pin CPH down to the user dim setting. The resistor can be selected for a fast time constant to minimize the amount of flash visible over the lamp just after ignition, or, a long time constant such that the brightness ramps down smoothly to the user setting. Should the ignition-to-dim time be too fast, however, the loop can respond faster than the ionization constant of the lamp (milliseconds) causing the VCO to over-shoot. This can result in a frequency that is higher than the minimum brightness frequency and can extinguish the lamp. The capacitor on pin CPH serves multiple functions by setting the preheat time, the travel rate just after ignition (together with resistor RDIM), and, serving as a filter capacitor on pin

DIM during dimming to increase high-frequency noise immunity and minimize component count.

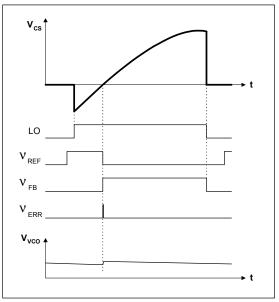

#### Dimming (DIM)

To regulate lamp power, the error between the reference phase and the phase of the output stage current forces the VCO to steer the frequency in the proper direction, as determined by the transfer function of the output stage, such that the error is forced to zero. An internal 15uA current source is connected to pin VCO during dimming mode (Figure 12) to discharge the VCO capacitor and decrease the frequency towards lock.

Figure 12, IR21592/IR21593 dimming circuitry.

Once lock is achieved, the phase detector (PDET) outputs short pulses to an open-drain PMOS that charges the VCO capacitor through an internal resistor (RFB) each time an error pulse occurs (Figure 13). This action "nudges" the integrator at the input of the VCO to keep the phase of the output stage current exactly locked in phase with the reference.

Figure 13, Phase control timing diagram.

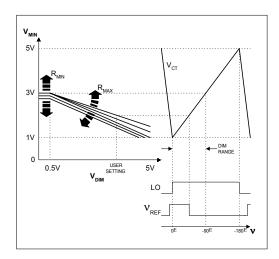

The IR21592/IR21593 includes a dimming interface for analog lamp power control. The DIM pin input requires a voltage in the range of 0.5 to 5VDC, with 5V corresponding to minimum phase shift (maximum lamp power). The output of the dim interface is the voltage on pin MIN, which is compared with the internal timing capacitor (CT) voltage to produce a frequency-independent digital reference phase (Figure 14).

Figure 14, Dimming interface

The charging time of CT from 1V to 5.1V determines the on-time of output gate drivers HO and LO and corresponds to -180 degrees of possible phase shift in load current (minus deadtime). For the 0 to -90 degree dim range, the voltage on pin MIN is bounded between 1V and 3V using pins MIN and MAX. An external resistor on pin MAX programs the minimum phase shift reference (maximum lamp power) corresponding to 5V on pin DIM, and an external resistor on pin MIN sets the maximum phase shift (minimum lamp power) corresponding to 0.5V on pin DIM.

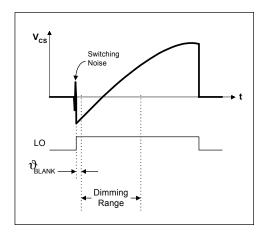

#### **Current Sensing**

During dimming, the current sensing circuitry (Figure 15) detects over-current which can occur during hard-switching (see Fault section), and zero-crossing to measure the phase of the total load current. To reject any switching noise which can occur at the turn-on of the low-side MOSFET or IGBT, a digital current sense blanking circuit blanks out the signal from the zero-crossing

detection comparator for 400ns after LO goes 'high' (Figure 16).

Figure 15, Current sensing circuitry.

The internal blank time reduces the dimming range slightly (Figure 16) when operating at minimum phase shift (maximum lamp power). The external programming resistor on pin MAX must be selected such that the minimum phase shift is set a safe margin away from the blank time. A series resistor (R1) is required to limit the amount of current flowing out of pin CS when the voltage across RCS goes below -0.7V. A filter capacitor at pin CS may be required due to other possible asynchronous noise sources present in the ballast system.

Figure 16, Current sense timing diagram.

#### Fault Mode (FAULT)

During dimming, the peak current regulation circuit active during preheat and ignition is disabled. Should non-zero voltage switching at the output of the half-bridge occur (Figure 17), high current spikes will result. A lamp filament failure, lamp end-of-life, lamp removal, or a deadtime shorter than what is required for commutation, can all cause hard-switching.

Figure 17, hard-switching with latch off

Should the peak voltage on pin CS exceed 1.6V at any time during dimming, the IR21592/IR21593 enters FAULT mode and the high and low-side driver outputs, HO and LO, are both turned off. Cycling the supply voltage on VCC below UVLO-or the voltage on pin SD above and below SD+ and SD- will reset the IR21592/IR21593 to preheat (PH) mode (see STATE DIAGRAM).

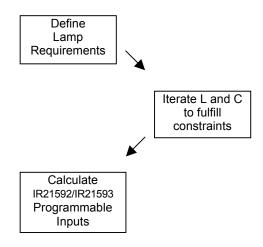

#### **Ballast Design**

#### **Lamp Requirements**

Before selecting component values for the ballast output stage and the programmable inputs of the IR21592/IR21593, the following lamp requirements must first be defined:

| Variable             | Description                     | Units |

|----------------------|---------------------------------|-------|

| $I_{ph}$             | Filament pre-heat current       | Arms  |

| $t_{ph}$             | Filament pre-heat time          | S     |

| $V_{ph_{\max}}$      | Maximum lamp pre-heat voltage   | Vpp   |

| $V_{ign}$            | Lamp ignition voltage           | Vpp   |

| $P_{100\%}$          | Lamp power at 100% brightness   | W     |

| $V_{100\%}$          | Lamp voltage at 100% brightness | Vpp   |

| $P_{1\%}$            | Lamp power at 1% brightness     | W     |

| V <sub>1%</sub>      | Lamp voltage at 1% brightness   | Vpp   |

| $I_{\it Cath_{min}}$ | Minimum cathode heating current | Arms  |

Table I, Typical lamp requirements

#### **Ballast Output Stage**

The components comprising the output stage are selected using a set of equations. Different ballast operating frequencies and their respective voltages and currents are calculated.

The inductor and capacitor values are obtained using equations (2) through (7). The results of these equations reveal the location of each operating frequency and the corresponding voltages and currents. For a given L, C, DC bus voltage, and pre-heat current, the resulting voltage over the lamp during pre-heat is given as:

$$V_{ph} = \left[ \left( \frac{2V_{DC}}{\pi} \right)^2 + \frac{8L}{C} I_{ph}^2 \right]^{\frac{1}{2}} - \frac{2V_{DC}}{\pi}$$

(2)

The resulting operating frequency during pre-heat is given as:

$$f_{ph} = \frac{\sqrt{2}I_{ph}}{\pi C V_{ph}}$$

[Hz] (3)

The resulting operating frequency during ignition is given as:

$$f_{ign} = \frac{1}{2\pi} \sqrt{\frac{1 + \frac{\frac{4}{\pi}V_{DC}}{V_{ign}}}{LC}}$$

[Hz] (4)

The total load current during ignition is given as:

$$I_{ign} = f_{ign}CV_{ign}2\pi$$

[App] (5)

The operating frequency [Hz] at maximum lamp power is given as:

$$f_{100\%} = \frac{1}{2\pi} \sqrt{\frac{1}{LC} - \frac{32P_{100\%}^2}{C^2V_{100\%}^4} + \sqrt{\left[\frac{1}{LC} - \frac{32P_{100\%}^2}{C^2V_{100\%}^4}\right]^2 - \frac{1 - \left(\frac{4V_{DC}}{V_{100\%}\pi}\right)^2}{L^2C^2}}}$$

**(6)**

The cathode heating current at minimum lamp power is given as:

$$I_{Cath_{1\%}} = \frac{V_{1\%} f_{1\%} \pi C}{\sqrt{2}} \tag{7}$$

#### **Design Constraints**

The inductor and capacitor values should be iterated until the following design constraints have been fulfilled (Table II).

| Design Constraint                    | Reason                            |

|--------------------------------------|-----------------------------------|

| $V_{ph} < V_{ph_{\max}}$             | Ignition during pre-<br>heat      |

| $f_{ph} - f_{ign} > 5kHz$            | Production tolerances             |

| $I_{ign} < I_{ign_{\max}}$           | Inductor saturation               |

| $I_{Cath_{1\%}} \ge I_{Cath_{\min}}$ | Lamp extinguishing during dimming |

Table II, Ballast design constraints

### IR21592/IR21593 Programmable Inputs

In order to program the MIN and MAX settings of the dimming interface, the phase of the output stage current at minimum and maximum lamp power must be calculated. This is obtained using the following equations:

# International ICR Rectifier

# IR21592/IR21593(S)&(PbF)

$$f_{\%} = \frac{1}{2\pi} \sqrt{\frac{1}{LC} - \frac{32P_{\%}^2}{C^2V_{\%}^4} + \sqrt{\left[\frac{1}{LC} - \frac{32P_{\%}^2}{C^2V_{\%}^4}\right]^2 - \frac{1 - \left(\frac{4V_{DC}}{V_{\%}\pi}\right)^2}{L^2C^2}}$$

(8)

$$\varphi_{\%} = \frac{180}{\pi} \tan^{-1} \left[ \left( \frac{V_{\%}^2}{2P_{\%}} C - \frac{2P_{\%}}{V_{\%}^2} L \right) 2\pi f_{\%} - 4 \frac{V_{\%}^2}{P_{\%}} L C^2 \pi^3 f_{\%}^3 \right]$$

(9)

With the lamp requirements defined, the L and C of the ballast output stage selected, and the minimum and maximum phase calculated, the component values for setting the programmable inputs of the IR21592/IR21593 are obtained with the following equations:

$$R_{FMIN} = \frac{(25e - 6) - (f_{MIN} - 10000) \cdot (1e - 10)}{(f_{MIN} - 10000) \cdot (2e - 14)}$$

[Ohms] (10)

$$R_{CS} = \frac{2 \cdot (1.6)}{I_{ion}}$$

[Ohms] (11)

$$R_{IPH} = R_{FMIN} R_{CS} I_{ph} \sqrt{2} \qquad [Ohms] \qquad (12)$$

$$C_{CPH} = (2.6E - 7)(t_{PH})$$

[Farads] (13)

$$R_{MIN} = \frac{R_{FMIN}}{4} \left( 1 - \frac{\varphi_{1\%}}{45} \right)$$

[Ohms] (14)

$$R_{MAX} = \frac{0.86 \cdot R_{FMIN} \cdot R_{MIN}}{4 \cdot R_{MIN} - R_{FMIN} \cdot \left(1 - \frac{\varphi_{100\%}}{45}\right)}$$

[Ohms] (15)

This ballast design procedure has been summarized into the following 3 steps:

Figure 19, Simplified Ballast Design Procedure

#### Case outline

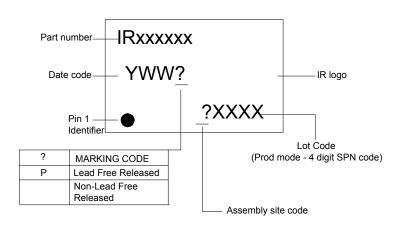

#### LEADFREE PART MARKING INFORMATION

#### **ORDER INFORMATION**

#### **Basic Part (Non-Lead Free)**

16-Lead PDIP IR21592 order IR21592 16-Lead SOIC IR21592S order IR21592S 16-Lead PDIP IR21593 order IR21593 16-Lead SOIC IR21593S order IR21593S

#### Leadfree Part

16-Lead PDIP IR21592 order IR21592PbF 16-Lead SOIC IR21592S order IR21592SPbF 16-Lead PDIP IR21593 order IR21593PbF 16-Lead SOIC IR21593S order IR21593SPbF

International

TOR Rectifier

IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245 Tel: (310) 252-7105

Data and specifications subject to change without notice.

This product has been designed and qualfied for the industrial market. 9/7/2005