# International Rectifier

## IRS2301S HIGH AND LOW SIDE DRIVER

#### **Features**

- Floating channel designed for bootstrap operation

- Fully operational to +600V

- Tolerant to negative transient voltage dV/dt immune

- Gate drive supply range from 5V to 20V

- Undervoltage lockout for both channels

- 3.3V, 5V and 15V input logic compatible

- · Matched propagation delay for both channels

- Outputs in phase with inputs

- Lower di/dt gate driver for better noise immunity

- Leadfree, RoHS compliant

#### **Typical Applications**

- Appliance motor drives

- Servo drives

- Micro inverter drives

- o General purpose three phase inverters

#### **Product Summary**

| V <sub>OFFSET</sub>                          | 600V Max      |

|----------------------------------------------|---------------|

| V <sub>OUT</sub>                             | 5V – 20V      |

| I <sub>0+</sub> & I <sub>0-</sub> (min)      | 120mA / 250mA |

| t <sub>ON</sub> & t <sub>OFF</sub> (typical) | 220ns / 200ns |

| Delay Matching                               | 50ns          |

**Package Options**

# **IRS2301S**

# International TOR Rectifier

| Table of Contents                              | Page |

|------------------------------------------------|------|

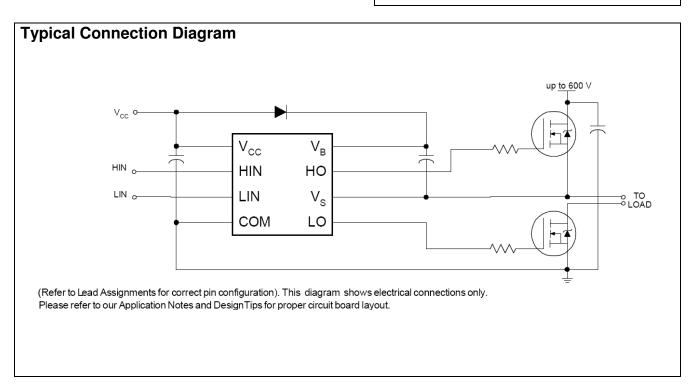

| Typical Connection Diagram                     | 1    |

| Description                                    | 3    |

| Feature Comparison                             | 3    |

| Qualification Information                      | 4    |

| Absolute Maximum Ratings                       | 5    |

| Recommended Operating Conditions               | 5    |

| Dynamic Electrical Characteristics             | 6    |

| Static Electrical Characteristics              | 6    |

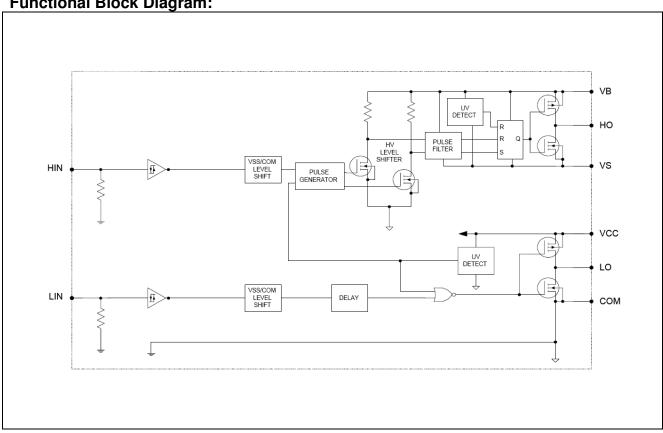

| Functional Block Diagram                       | 7    |

| Input/output Timing Diagram                    | 8    |

| Lead Definitions                               | 9    |

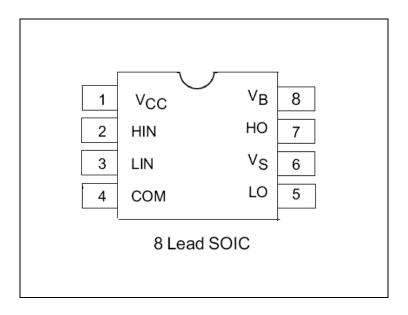

| Lead Assignments                               | 9    |

| Application Information and Additional Details | 10   |

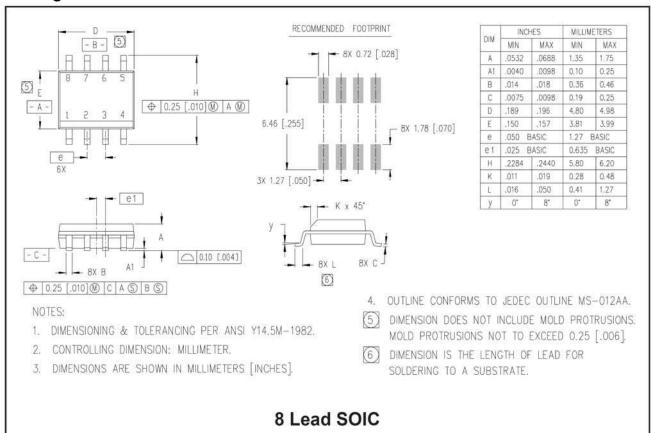

| Package Details                                | 11   |

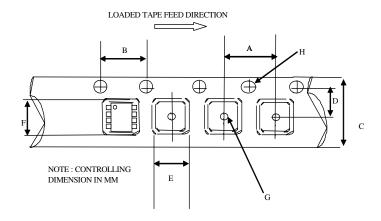

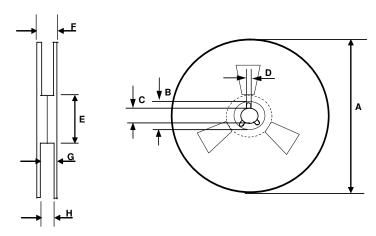

| Tape and Reel Details                          | 12   |

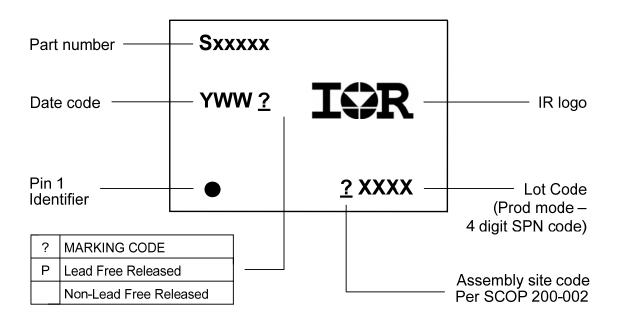

| Part Marking Information                       | 13   |

| Ordering Information                           | 14   |

**IRS2301S**

International IOR Rectifier

#### **Description**

The IRS2301S is a high voltage, high speed power MOSFET and IGBT driver with independent high- and low-side referenced output channels. Proprietary HVIC and latch immune CMOS technologies enable ruggedized monolithic construction. The logic input is compatible with standard CMOS or LSTTL output, down to 3.3V logic. The output drivers feature a high pulse current buffer stage. The floating channel can be used to drive an N-channel power MOSFET or IGBT in the high-side configuration which operates up to 600V.

#### Qualification Information<sup>†</sup>

| -,                         | nation           |                                                             |  |  |

|----------------------------|------------------|-------------------------------------------------------------|--|--|

| Qualification Level        |                  | Industrial <sup>††</sup>                                    |  |  |

|                            |                  | Comments: This family of ICs has passed JEDEC's             |  |  |

|                            |                  | Industrial qualification. IR's Consumer qualification level |  |  |

|                            |                  | is granted by extension of the higher Industrial level.     |  |  |

| Moisture Sensitivity Level |                  | MSL2 <sup>†††</sup> 260°C                                   |  |  |

|                            |                  | (per IPC/JEDEC J-STD-020)                                   |  |  |

|                            | Machine Model    | Class B                                                     |  |  |

| ESD                        | Macrille Model   | (per JEDEC standard JESD22-A115)                            |  |  |

| E3D                        | Human Body Model | Class 2                                                     |  |  |

|                            | Human Body Wodel | (per EIA/JEDEC standard EIA/JESD22-A114)                    |  |  |

| IC Letch Un Teet           |                  | Class I, Level A                                            |  |  |

| IC Latch-Up Test           |                  | (per JESD78)                                                |  |  |

| RoHS Compliant             |                  | Yes                                                         |  |  |

- † Qualification standards can be found at International Rectifier's web site <a href="http://www.irf.com/">http://www.irf.com/</a>

- †† Higher qualification ratings may be available should the user have such requirements. Please contact your International Rectifier sales representative for further information.

- ††† Higher MSL ratings may be available for the specific package types listed here. Please contact your International Rectifier sales representative for further information.

#### **Absolute Maximum Ratings**

Absolute Maximum Ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to COM. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.

| Symbol              | Definition                                | Min.                 | Max.                  | Units                 |  |  |

|---------------------|-------------------------------------------|----------------------|-----------------------|-----------------------|--|--|

| $V_B$               | High-side floating absolute voltage       | -0.3                 | 625                   |                       |  |  |

| Vs                  | High-side floating supply offset voltage  | V <sub>B</sub> - 25  | V <sub>B</sub> + 0.3  |                       |  |  |

| $V_{HO}$            | High-side floating output voltage         | V <sub>S</sub> - 0.3 | V <sub>B</sub> + 0.3  |                       |  |  |

| V <sub>CC</sub>     | Low-side and logic fixed supply voltage   | -0.3                 | 25 V                  |                       |  |  |

| $V_{LO}$            | Low-side output voltage                   | -0.3                 | V <sub>CC</sub> + 0.3 |                       |  |  |

| $V_{IN}$            | Logic input voltage (HIN & LIN)           | COM -0.3             | $V_{CC} + 0.3$        | V <sub>CC</sub> + 0.3 |  |  |

| dV <sub>S</sub> /dt | Allowable offset supply voltage transient | _                    | 50                    | V/ns                  |  |  |

| $P_{D}$             | Package power dissipation @ TA ≤ 25°C     | _                    | 0.625                 | 0.625 W               |  |  |

| Rth <sub>JA</sub>   | Thermal resistance, junction to ambient   | _                    | 200                   | °C/W                  |  |  |

| TJ                  | Junction temperature                      | _                    | 150                   |                       |  |  |

| Ts                  | Storage temperature                       | -50                  | 150                   | 150 °C                |  |  |

| T <sub>L</sub>      | Lead temperature (soldering, 10 seconds)  | _                    | 300                   |                       |  |  |

#### **Recommended Operating Conditions**

The input/output logic timing diagram is shown in Fig. 1. For proper operation the device should be used within the recommended conditions. The  $V_S$  offset rating is tested with all supplies biased at 15V differential.

| Symbol          | Definition                                          | Min.               | Max.                | Units |  |  |  |

|-----------------|-----------------------------------------------------|--------------------|---------------------|-------|--|--|--|

| $V_{B}$         | High-side floating supply absolute voltage          | V <sub>S</sub> + 5 | V <sub>S</sub> + 20 |       |  |  |  |

| Vs              | High-side floating supply offset voltage            | † 1                | 600                 |       |  |  |  |

| $V_{HO}$        | High-side floating output voltage                   | Vs                 | V <sub>B</sub> V    |       |  |  |  |

| V <sub>CC</sub> | Low-side and logic fixed supply voltage             | 5                  | 20 V                |       |  |  |  |

| $V_{LO}$        | Low-side output voltage 0 V <sub>CC</sub>           |                    |                     |       |  |  |  |

| V <sub>IN</sub> | Logic input voltage (HIN & LIN) COM V <sub>CC</sub> |                    |                     |       |  |  |  |

| T <sub>A</sub>  | Ambient temperature                                 | -40                | 125                 | °C    |  |  |  |

<sup>†:</sup> Logic operational for V<sub>S</sub> of -5 V to +600 V. Logic state held for V<sub>S</sub> of -5 V to – V<sub>BS</sub>. (Please refer to the Design Tip DT97 -3 for more details).

www.irf.com © 2009 International Rectifier

#### **Static Electrical Characteristics**

$V_{BIAS}$  ( $V_{CC}$ ,  $V_{BS}$ ) = 15V and  $T_A$  = 25°C unless otherwise specified. The  $V_{IL}$ ,  $V_{IH}$  and  $I_{IN}$  parameters are referenced to COM and are applicable to the respective input leads: HIN and LIN. The  $V_{O_i}$   $I_{O_i}$  and  $I_{O_i}$  parameters are referenced to COM and are applicable to the respective output leads: HO and LO.

| Symbol                                | Definition                                                                       | Min | Тур | Max | Units | Test conditions                    |

|---------------------------------------|----------------------------------------------------------------------------------|-----|-----|-----|-------|------------------------------------|

| $V_{IH}$                              | Logic "1" input voltage                                                          | 2.5 | _   | _   | V     | V <sub>CC</sub> = 10V to 20V       |

| $V_{IL}$                              | Logic "0" input voltage                                                          | _   |     | 8.0 | V     |                                    |

| $V_{OH}$                              | High level output voltage, V <sub>BIAS</sub> - V <sub>O</sub>                    | _   |     | 0.2 | V     | I <sub>O</sub> = 2mA               |

| $V_{OL}$                              | Low level output voltage, V <sub>O</sub>                                         | _   | _   | 0.1 | V     | 1 <sub>0</sub> – 2111A             |

| I <sub>LK</sub>                       | Offset supply leakage current                                                    | _   | _   | 50  |       | $V_{B} = V_{S} = 600V$             |

| $I_{QBS}$                             | Quiescent V <sub>BS</sub> supply current                                         | 60  | 160 | 260 |       | V <sub>IN</sub> = 0V or 5V         |

| I <sub>QCC</sub>                      | Quiescent V <sub>CC</sub> supply current                                         | 60  | 160 | 260 | μA    | V <sub>IN</sub> = 0 V 01 5 V       |

| I <sub>IN+</sub>                      | Logic "1" input bias current                                                     | _   | 5   | 20  |       | V <sub>IN</sub> = 5V               |

| $I_{IN-}$                             | Logic "0" input bias current                                                     | _   |     | 5   |       | $V_{IN} = 0V$                      |

| $V_{\text{CCUV+}}$ $V_{\text{BSUV+}}$ | V <sub>CC</sub> and V <sub>BS</sub> supply undervoltage positive going threshold | 3.3 | 4.1 | 5   |       |                                    |

| $V_{CCUV-} V_{BSUV-}$                 | $V_{\text{CC}}$ and $V_{\text{BS}}$ supply undervoltage negative going threshold | 3   | 3.8 | 4.7 | V     |                                    |

| $V_{\text{CCUVH}}$ $V_{\text{BSUVH}}$ | Hysteresis                                                                       | 0.1 | 0.3 | —   |       |                                    |

| I <sub>O+</sub>                       | Output high short circuit pulsed current                                         |     | 200 |     | mA    | V <sub>O</sub> = 0V,<br>PW ≤ 10µs  |

| I <sub>O-</sub>                       | Output low short circuit pulsed current                                          | _   | 350 | _   | ША    | V <sub>O</sub> = 15V,<br>PW ≤ 10µs |

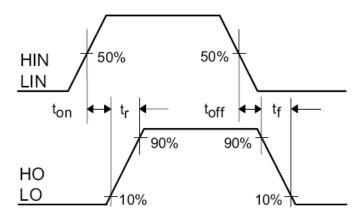

#### **Dynamic Electrical Characteristics**

$V_{BIAS}$  ( $V_{CC}$ ,  $V_{BS}$ ) = 15V,  $C_L$  = 1000pF,  $T_A$  = 25°C unless otherwise specified.

| Symbol           | Definition                          | Min | Тур | Max | Units | Test conditions             |

|------------------|-------------------------------------|-----|-----|-----|-------|-----------------------------|

| t <sub>on</sub>  | Turn-on propagation delay           | _   | 220 | 300 |       | $V_S = 0V$                  |

| t <sub>off</sub> | Turn-off propagation delay          | _   | 200 | 280 |       | V <sub>S</sub> = 0V or 600V |

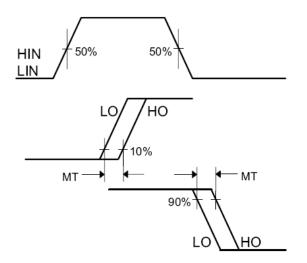

| MT               | Delay matching, HS & LS turn-on/off | _   | 0   | 50  | ns    |                             |

| t <sub>r</sub>   | Turn-on rise time                   | _   | 130 | 220 |       | \/ - 0\/                    |

| t <sub>f</sub>   | Turn-off fall time                  | _   | 50  | 80  |       | $V_S = 0V$                  |

**Functional Block Diagram:**

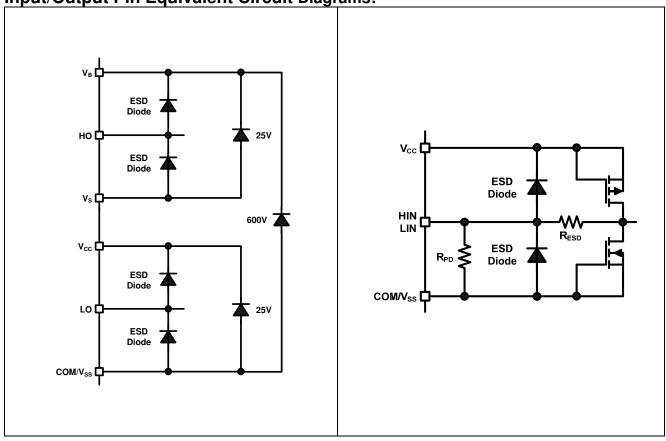

**Input/Output Pin Equivalent Circuit Diagrams:**

#### **Lead Definitions:**

| PIN# | Symbol   | Description                                                         |  |  |  |  |

|------|----------|---------------------------------------------------------------------|--|--|--|--|

| 1    | $V_{CC}$ | _ow-side and logic fixed supply                                     |  |  |  |  |

| 2    | HIN      | ogic input for high-side gate driver outputs (HO), in phase with HO |  |  |  |  |

| 3    | LIN      | Logic input for low-side gate driver outputs (LO), in phase with LO |  |  |  |  |

| 4    | COM      | Low-side return                                                     |  |  |  |  |

| 5    | LO       | Low-side gate drive output                                          |  |  |  |  |

| 6    | $V_S$    | High-side floating supply return                                    |  |  |  |  |

| 7    | НО       | High-side gate drive output                                         |  |  |  |  |

| 8    | $V_B$    | High-side floating supply                                           |  |  |  |  |

## **Lead Assignments**

#### **Application Information and Additional Details**

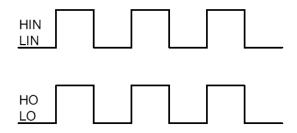

Figure 1: Input/Output Timing Diagram

**Figure 2: Switching Time Waveform Definitions**

**Figure 3: Delay Matching Waveform Definitions**

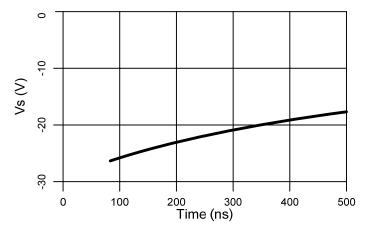

#### **Tolerability to Negative VS Transients**

The IRS2301S has been seen to withstand negative  $V_S$  transient conditions on the order of -25V for a period of 100 ns ( $V_{BIAS}$  ( $V_{CC}$ ,  $V_{BS}$ ) = 15V and  $T_A$  = 25°C).

An illustration of the IRS2301S performance can be seen in Figure 4.

Even though the IRS2301S has been shown able to handle these negative Vs transient conditions, it is highly recommended that the circuit designer always limit the negative Vs transients as much as possible by careful PCB layout and component use.

Figure 4: -Vs Transient results

www.irf.com © 2009 International Rectifier

#### **IRS2301S**

#### **Package Details**

www.irf.com © 2009 International Rectifier

# **Tape and Reel Details**

CARRIER TAPE DIMENSION FOR 8SOICN

|      | Metric |       | Imperial |       |  |

|------|--------|-------|----------|-------|--|

| Code | Min    | Max   | Min      | Max   |  |

| Α    | 7.90   | 8.10  | 0.311    | 0.318 |  |

| В    | 3.90   | 4.10  | 0.153    | 0.161 |  |

| С    | 11.70  | 12.30 | 0.46     | 0.484 |  |

| D    | 5.45   | 5.55  | 0.214    | 0.218 |  |

| E    | 6.30   | 6.50  | 0.248    | 0.255 |  |

| F    | 5.10   | 5.30  | 0.200    | 0.208 |  |

| G    | 1.50   | n/a   | 0.059    | n/a   |  |

| Н    | 1.50   | 1.60  | 0.059    | 0.062 |  |

REEL DIMENSIONS FOR 8SOICN

| RELE DIMENSIONS FOR 830ICN |        |        |          |        |  |  |

|----------------------------|--------|--------|----------|--------|--|--|

|                            | Metric |        | Imperial |        |  |  |

| Code                       | Min    | Max    | Min      | Max    |  |  |

| Α                          | 329.60 | 330.25 | 12.976   | 13.001 |  |  |

| В                          | 20.95  | 21.45  | 0.824    | 0.844  |  |  |

| С                          | 12.80  | 13.20  | 0.503    | 0.519  |  |  |

| D                          | 1.95   | 2.45   | 0.767    | 0.096  |  |  |

| E<br>F                     | 98.00  | 102.00 | 3.858    | 4.015  |  |  |

|                            | n/a    | 18.40  | n/a      | 0.724  |  |  |

| G                          | 14.50  | 17.10  | 0.570    | 0.673  |  |  |

| Н                          | 12.40  | 14.40  | 0.488    | 0.566  |  |  |

#### **Part Marking Information**

#### **Ordering Information**

| Barra Barri Marrahan | Basisana Tama | Standard Pack |          | O a marel a la David Name la m |  |

|----------------------|---------------|---------------|----------|--------------------------------|--|

| Base Part Number     | Package Type  | Form          | Quantity | Complete Part Number           |  |

| ID0004               | SOIC8N        | Tube/Bulk     | 95       | IRS2301SPBF                    |  |

| IRS2301              | SOICON        | Tape and Reel | 2500     | IRS2301STRPBF                  |  |

The information provided in this document is believed to be accurate and reliable. However, International Rectifier assumes no responsibility for the consequences of the use of this information. International Rectifier assumes no responsibility for any infringement of patents or of other rights of third parties which may result from the use of this information. No license is granted by implication or otherwise under any patent or patent rights of International Rectifier. The specifications mentioned in this document are subject to change without notice. This document supersedes and replaces all information previously supplied.

For technical support, please contact IR's Technical Assistance Center <a href="http://www.irf.com/technical-info/">http://www.irf.com/technical-info/</a>

#### **WORLD HEADQUARTERS:**

233 Kansas St., El Segundo, California 90245 Tel: (310) 252-7105