## 2n2322 to 2n2326

# SILICON THYRISTORS

All-diffused PNPN thyristors designed for grating operation in mA/ $\mu$ A signal or detection circuits Compliance to RoHS.

### MAXIMUM RATINGS (\*)

$T_{J}{=}125 \ensuremath{\mathbb{C}}$  unless otherwise noted, R  $_{GK}{=}1000 \Omega$

| Symbol                | Ratings                                                                                                 | 2N2322 | 2N2323 | 2N2324     | 2N2325 | 2N2326 | Unit |

|-----------------------|---------------------------------------------------------------------------------------------------------|--------|--------|------------|--------|--------|------|

| V <sub>RRM(REP)</sub> | Peak reverse blocking voltage (*)                                                                       | 25     | 50     | 100        | 150    | 200    | V    |

| V <sub>RSM(NON-</sub> | Non-repetitive peak blocking reverse voltage (t<5.0 ms)                                                 | 40     | 75     | 150        | 225    | 300    | V    |

| I <sub>T(RMS)</sub>   | Forward Current RMS (all conduction angles)                                                             |        |        | 1.6        |        |        | А    |

| I <sub>TSM</sub>      | Peak Surge Current<br>(One-Half Cycle, 60Hz)<br>No Repetition Until Thermal<br>Equilibrium is Restored. |        |        | 15         |        |        | A    |

| P <sub>GM</sub>       | Peak Gate Power – Forward                                                                               |        |        | 0.1        |        |        | W    |

| P <sub>G(AV)</sub>    | Average Gate Power -<br>Forward                                                                         |        |        | 0.01       |        |        | W    |

| I <sub>GM</sub>       | Peak Gate Current – Forward                                                                             |        |        | 0.1        |        |        | А    |

| V <sub>GFM</sub>      | Peak Gate Voltage - Forward                                                                             |        |        | 6.0        |        |        | V    |

| V <sub>GRM</sub>      | Peak Gate Voltage - Reverse                                                                             |        |        | 6.0        |        |        | V    |

| TJ                    | Operating Junction<br>Temperature Range                                                                 |        | -      | 65 to +12  | 5      |        | C    |

| T <sub>STG</sub>      | Storage Temperature Range                                                                               |        | -      | 65 to +150 | C      |        | -    |

## 2n2322 to 2n2326

## **ELECTRICAL CHARACTERISTICS** (\*)

$T_{J}{=}25^{\circ}{\!\!\!\mathrm{C}}$  unless otherwise noted, R  $_{GK}{=}1000\Omega$

| Symbol           | Ratings                                                                                  | 2N2322 | 2N2323 | 2N2324     | 2N2325 | 2N2326 | Unit |

|------------------|------------------------------------------------------------------------------------------|--------|--------|------------|--------|--------|------|

| V <sub>DRM</sub> | Peak Forward Blocking Voltage (1)                                                        | 25     | 50     | 100        | 150    | 200    | V    |

| I <sub>RRM</sub> | Peak Reverse Blocking<br>Current<br>(Rated V <sub>DRM,</sub> T <sub>J</sub> =125℃)       |        |        | Max : 100  |        |        | μA   |

| I <sub>DRM</sub> | Peak Forward Blocking<br>Current<br>(Rated V <sub>DRM,</sub> T <sub>J</sub> =125℃)       |        |        | Max : 100  |        |        | μA   |

| V <sub>TM</sub>  | Forward « on » Voltage<br>I <sub>TM</sub> =1.0 A Peak                                    |        |        | Max : 1.5  |        |        | V    |

|                  | I <sub>™</sub> =3.14 A Peak<br>T <sub>c</sub> =85℃                                       |        |        | Max : 2.0  |        |        | ,    |

| I <sub>GT</sub>  | Gate Trigger Current (2)<br>Anode Voltage=6.0 Vdc<br>$R_L=100\Omega$                     |        |        | Max : 200  | I      |        | μA   |

| -01              | Anode Voltage=6.0 Vdc<br>R <sub>L</sub> =100 $\Omega$ , T <sub>c</sub> =-65 $^{\circ}$ C |        |        | Max : 350  |        |        |      |

|                  | Gate Trigger Voltage<br>Anode Voltage=6.0 V<br>$R_L$ =100 $\Omega$                       |        |        | Max : 0.8  |        |        |      |

| V <sub>GT</sub>  | Anode Voltage=6.0 V<br>R <sub>L</sub> =100 $\Omega$ , T <sub>C</sub> =-65 $\degree$      |        |        | Max : 1.0  |        |        | V    |

|                  | V <sub>DRM</sub> = Rated<br>R <sub>L</sub> =100Ω, T <sub>J</sub> =125℃                   |        |        | Min : 0.1  |        |        |      |

|                  | Holding Current<br>Anode Voltage=6.0 V                                                   |        |        | Max : 2.0  |        |        |      |

| I <sub>H</sub>   | Anode Voltage=6.0 V<br>T <sub>c</sub> =-65℃                                              |        |        | Max : 3.0  |        |        | mA   |

|                  | Anode Voltage=6.0 V<br>T <sub>c</sub> =125℃                                              |        |        | Min : 0.15 |        |        |      |

(\*) JEDEC Registered Values

(1)  $V_{RSM}$  and  $V_{DRM}$  can be applied for all types on a continuous dc basis without incurring damage.

(2)  $R_{GK}$  current is not included in measurement.

## 2n2322 to 2n2326

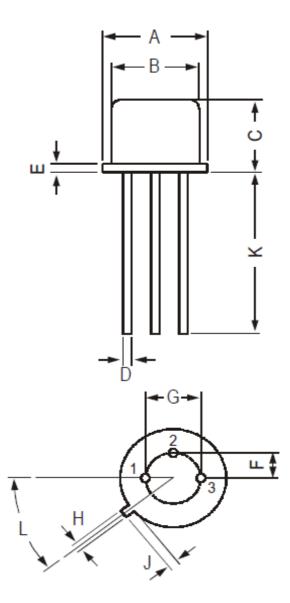

### **MECHANICAL DATA CASE TO-39**

| DIMENSIONS (mm) |       |      |

|-----------------|-------|------|

|                 | min   | max  |

| А               | 8.50  | 9.39 |

| В               | 7.74  | 8.50 |

| С               | 6.09  | 6.60 |

| D               | 0.40  | 0.53 |

| E               | -     | 0.88 |

| F               | 2.41  | 2.66 |

| G               | 4.82  | 5.33 |

| н               | 0.71  | 0.86 |

| J               | 0.73  | 1.02 |

| К               | 12.70 | -    |

| L               | 42°   | 48°  |

| 1 : kathode | Pin 1 : |

|-------------|---------|

| 2 : Gate    | Pin 2 : |

| 3 : Anode   | Pin 3 : |

| se : anode  | Case :  |

#### **Revised October 2012**

Information furnished is believed to be accurate and reliable. However, Comset Semiconductors assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may results from its use. Data are subject to change without notice. Comset Semiconductors makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Comset Semiconductors assume any liability arising out of the application or use of any product and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Comset Semiconductors' products are not authorized for use as critical components in life support devices or systems.

#### www.comsetsemi.com

#### info@comsetsemi.com