# PIM200X Series; ATCA Board Power Input Modules

-38 to -75 Vdc; 200W Input

## **RoHS Compliant**

## **Applications**

- ATCA Front Board / Blade

- Central Office Telecom equipment

- High availability server and storage applications

## **Options**

- Choice of System Management Power:

- 3.3Vdc (PIM200F)

- 5.0Vdc (PIM200A)

- Choice of short pin lengths

- Basic Insulation (-B)

#### **Features**

- 200W / -48V telecom input power distribution

- 8W (3.3Vdc or 5.0Vdc) of isolated Management Power for IPM or other housekeeping functions

- OR'ing functionality for the A/B & RTN power feeds as well as Enable A/B signals

- Inrush protection / hot swap capability

- Integral EMI filter designed for the ATCA board to meet CISPR Class B

- Independent 72Vdc output for charging the external holdup capacitors resulting in significant board real estate savings and bleed resistor power dissipation

- A/B Feed Loss or open fuse alarm (opto-isolated)

- Protection: Reverse Polarity, under voltage, input transient over voltage, over current & over temperature

- High efficiency: 97% @ -48V / 200W (@ 25C)

- -5 to 70°C ambient temperature operation

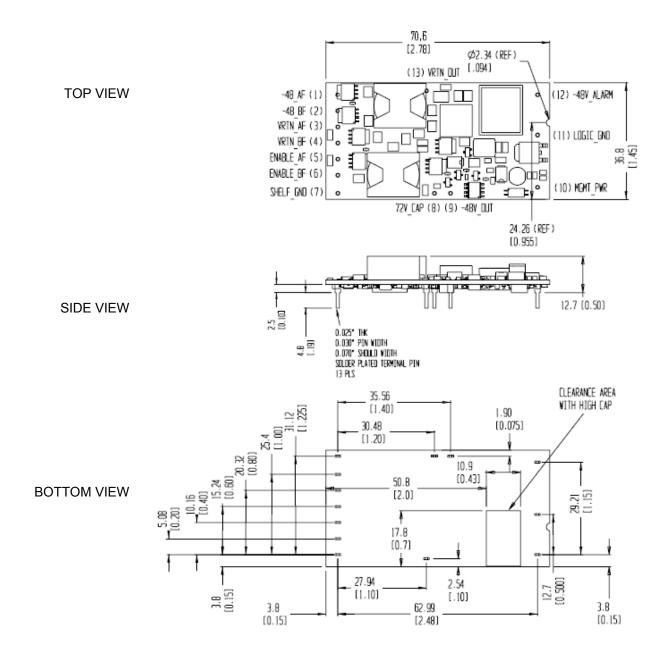

- Compact design: 70.6 mm x 36.8 mm x 12.7 mm

(2.78 in x 1.45 in x 0.5 in)

- MTBF: 1,565,825 hours per TELCORDIA

- ISO\*\* 9001 & ISO 14001 certified manufacturing facilities

- Compliant to RoHS EU Directive 2002/95/EC

- *UL*\* 60950-1 Recognized, *CSA*<sup>†</sup> C22.2 No. 60950-1-03 Certified, EN 60950-1 (VDE<sup>‡</sup> 0805: 2001-12) Licensed

## **Description**

The PIM200X-series is a new class of power modules designed to greatly simplify the task of implementing dual redundant, hot swap -48Vdc power distribution with EMI filtering on an ATCA or other telecom boards. The PIM200X, when used with a variety of Lineage Power's dc-dc converters/POLs provides for a quick, simple and elegant power architecture solution to a wide variety of complex power requirements. While providing high reliability, innovative features and compact design at a low cost, the module significantly reduces the valuable telecom board real estate compared to conventional discrete designs. Besides processing the main -48V bus, the module greatly simplifies the task of powering the IPM (for ATCA applications), system management or other housekeeping functions by providing a completely isolated auxiliary 3.3V or 5.0V power bus.

Document No: DS05-101 ver. 1.1 PDF name: pim200\_series\_ds.pdf

UL is a registered trademark of Underwriters Laboratories. Inc.

CSA is a registered trademark of Canadian Standards Association.

VDE is a trademark of Verband Deutscher Elektrotechniker e.V.

<sup>\*\*</sup> ISO is a registered trademark of the International Organization of Standards

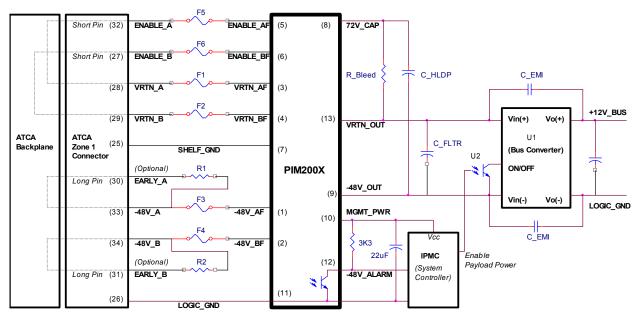

## 200W ATCA Board Typical Application

$$C_{HLDP}(\mu F) \ge [P_{out}(W) * \{T_{holdup}(ms) + 1.7\}]/1.9$$

$$R\_Bleed(\Omega) \le 5.485/C\_HLDP(F)$$

## **Suggested Bill of Materials**

(Note: Customer is ultimately responsible for the selection and verification of the suggested parts).

| Qty     | Ref Des | Description                                     | MFR / PN<br>(or equivalent)                                                      | Comments                                                         |

|---------|---------|-------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------|

| 2       | F1, F2  | Fuse, SMT, 10 Amp                               | Bel Fuse: SSQ Series                                                             | VRTN_A, VRTN_B                                                   |

| 2       | F3, F4  | Fuse, SMT, 8 Amp                                | Littelfuse 451/ 453 Series                                                       | -48V_A, -48V_B                                                   |

| 2       | F5, F6  | Fuse, SMT, 1/16th Amp                           | (Voltage rating >/=75V)                                                          | ENABLE_A, ENABLE_B                                               |

| 1       | C_FLTR  | Capacitors, Al Electrolytic<br>150uF/100V       | Nippon/Chemicon; KZE Series<br>Panasonic: FK Series (SMT)<br>Nichicon: UJ Series | C_FLTR (Max) = 220uF                                             |

| 3       | C HLDP  | Capacitors, Al Electrolytic<br>470uF/80V        | Nippon/Chemicon; KZE Series<br>Panasonic: FK Series (SMT)                        | =1400 uF (1200uF + 20% Tol)<br>(for 200W &<br>Tholdup=9.3 msecs) |

| OR<br>1 | סבורו   | OR<br>Capacitors, Al Electrolytic<br>1800uF/80V | OR<br>Panasonic / ECEC1KP182DL<br>30mm(OD) X 20mm(L)                             | OR<br>Snap-In Radial                                             |

| 1       | R_Bleed | SM, 3.9Kohms, 1W                                |                                                                                  | For C_HLDP=1400uF                                                |

| 2       | C_EMI   | SM, 4700pF, >/=1500V                            | Novacap, Murata or Syfer                                                         | Size: >/= 1210                                                   |

| 1       | U1      | 200W/12V Bus Converter                          | Lineage Power: QBW018A0B1                                                        |                                                                  |

| 1       | U2      | Opto-coupler (1500V)                            | Fairchild : HMHA2801                                                             | Safety approved                                                  |

| 2       | R1, R2  | High Surge Power,<br>15 Ohms                    | KOA: SG73 (Size >/=1206)                                                         | Optional; See "Design<br>Consideration" section                  |

## **Absolute Maximum Ratings:**

Stresses in excess of the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only, functional operation of the device is not implied at these or any other conditions in excess of those given in the operations sections of the data sheet. Exposure to absolute maximum ratings for extended periods can adversely affect the device reliability.

| Parameter                                                                       | Device | Symbol                | Min | Тур | Max  | Unit  |

|---------------------------------------------------------------------------------|--------|-----------------------|-----|-----|------|-------|

| Input Voltage (Absolute values)                                                 |        |                       |     |     |      |       |

| Continuous                                                                      | All    | VI                    | 0   | -48 | -75  | Vdc   |

| Transient (Pulse duration above –75V = 1ms)                                     | All    | $V_{tr}$              | -75 |     | -100 | Vdc   |

| Temperature                                                                     |        |                       |     |     |      |       |

| Normal Operating Ambient Temperature (See Thermal Considerations section)       | All    | T <sub>A</sub>        | -5  |     | 70   | °C    |

| Storage Temperature                                                             | All    | $T_{stg}$             | -55 |     | 125  | °C    |

| Power                                                                           |        |                       |     |     |      |       |

| Input Power, Maximum Allowable                                                  | All    | $P_{in,max}$          |     |     | 200  | W     |

| Power Dissipation (Internal Module Dissipation @ Pin, max) (with MGMT_PWR = 8W) | All    | P <sub>diss</sub>     |     | 6   |      | W     |

| Output Power, Maximum Deliverable<br>(Management Power + Payload Power)         | All    | P <sub>out</sub>      |     | 194 |      | W     |

| Management Power, Maximum Deliverable (MGMT_PWR)                                | All    | P <sub>MGMT_PWR</sub> |     |     | 8    | W     |

| Module Standby Power<br>(@-48Vin & MGMT_PWR=0W, Pout=0W)                        | All    | P <sub>Stdby</sub>    |     | 2.0 |      | W     |

| Isolation                                                                       |        |                       |     |     |      |       |

| Input to MGMT_PWR Output Voltage                                                | All    |                       |     |     | 1500 | Vdc   |

| Input to SHELF_GND Voltage                                                      | All    |                       |     |     | 1500 | Vdc   |

| Input to LOGIC_GND Voltage                                                      | All    |                       |     |     | 1500 | Vdc   |

| LOGIC_GND to SHELF_GND Insulation Resistance with 100Vdc Test Voltage           | All    |                       | 9   |     |      | MOhms |

# CAUTION: This power module is not internally fused. Both A & B feeds and their corresponding returns must be individually fused.

To preserve maximum flexibility, internal fusing is not included. However, to achieve maximum safety and system protection, the safety agencies require a fast-acting fuse with a maximum rating of 10 Amps and voltage rating of >/=75Vdc for the -48AF, -48BF VRTN\_AF & VRTN\_BF feeds. Consult Fusing and fault protection (Section 4.1.4) of PICMG 3.0 ATCA specifications for additional information. Based on the information provided in this data sheet on inrush current and maximum dc input current, the same type of fuse with a lower rating can be used. Refer to the fuse manufacturer's data sheet for further information.

## **Electrical Specifications:**

Unless otherwise indicated, specifications apply over all operating input voltage, resistive load, and temperature conditions.

| Parameter                                                                                                                                                                                                                     | Device  | Symbol               | Min     | Тур   | Max      | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------|---------|-------|----------|------|

| Main Input (-48_AF,-48_BF,VRTN_AF,V                                                                                                                                                                                           | RTN_BF) | ; (Absolute v        | /alues) |       | ı        |      |

| Operating Input Voltage (Module will operate down to –36V depending on the output power and thermal environment but may not support holdup time requirements)                                                                 | All     | Vı                   | -38     | -48   | -75      | Vdc  |

| Input Voltage Turn-on Threshold (Module On)                                                                                                                                                                                   | All     | V <sub>UVHI</sub>    | -34.3   | -35.3 | -36.0    | Vdc  |

| Under Voltage Lockout Threshold (Module Off)                                                                                                                                                                                  | All     | V <sub>UVLO</sub>    | -32.4   | -33.7 | -34.1    | Vdc  |

| Maximum current drain if input voltage falls below $\ensuremath{V_{\text{UVLO}}}$ for $>$ 2 seconds.                                                                                                                          | All     | l <sub>stdby</sub>   |         |       | 10       | mA   |

| Maximum Input Current (V <sub>I</sub> =0V to -75Vdc, P <sub>in</sub> =P <sub>in, max</sub> )                                                                                                                                  | All     | I <sub>I, max</sub>  |         |       | 6        | Adc  |

| Inrush Transient (with C_FLTR,max = $220\mu F$ )                                                                                                                                                                              | All     |                      |         |       |          |      |

| Duration: 0.1 to 0.9 ms                                                                                                                                                                                                       |         | lpk                  |         |       | 30       | Adc  |

| Duration: 0.9 to 3 ms<br>(Logarithmically declining)                                                                                                                                                                          |         | lpk                  |         |       | 30 to 12 | Adc  |

| Duration: 3 to 100 ms                                                                                                                                                                                                         |         | lpk                  |         |       | 6        | Adc  |

| ENABLE A/B Signal Inputs (ENABLE_A                                                                                                                                                                                            | , ENABL | E_B)                 |         |       | •        |      |

| Enable A / B Signals current drain (Vin = -75Vdc)                                                                                                                                                                             | All     |                      |         |       | 700      | μAdc |

| Main Output (-48V_OUT, VRTN_OUT)                                                                                                                                                                                              |         |                      |         |       |          |      |

| External Output Filter Capacitance (C_FLTR)                                                                                                                                                                                   | All     | C_FLTR               | 100*    |       | 220      | μF   |

| 72V Holdup Capacitor Output (72V_CA                                                                                                                                                                                           | P)      |                      |         |       |          |      |

| 72V_CAP Output Voltage Tolerance                                                                                                                                                                                              | All     |                      | 68.4    | 72.0  | 74.2     | Vdc  |

| 72V_CAP ON (OR'd) Input Voltage Threshold                                                                                                                                                                                     |         |                      | -36.2   | -37.7 | -39.2    | Vdc  |

| A/B Feed Loss / Fuse Alarm Output (-48                                                                                                                                                                                        | BV_ALAF | RM)                  |         |       |          |      |

| -48V_ALARM is an Opto-isolated open collector output with the emitter internally referenced to LOGIC_GND. Alarm Characteristics: Power Good / Fuse Good = LO (Opto conducting) A or B Feed Loss / Fuse (open) = HI (Opto off) |         |                      |         |       |          |      |

| Alarm ON Input Voltage Threshold                                                                                                                                                                                              | All     |                      | -36.1   | -37.2 | -38.2    | Vdc  |

| Opto Transistor Collector to Emitter Voltage                                                                                                                                                                                  |         | Vceo                 |         |       | 40       | Vdc  |

| Opto Transistor Collector to Emitter Dark Current (Opto Diode current, Id = 0A)                                                                                                                                               |         | Iceo                 |         |       | 100      | nA   |

| Opto Transistor Collector Current                                                                                                                                                                                             |         | Ic                   |         |       | 5        | mA   |

| Opto Transistor Collector Saturation Voltage                                                                                                                                                                                  |         | $V_{\text{CE(sat)}}$ |         |       | 0.3      | Vdc  |

Note: \* See "Design Considerations" section for further information.

# **Electrical Specifications (continued):**

| Parameter                                                                                                                                                                                                                            | Output<br>Voltage | Symbol                         | Min        | Тур      | Max        | Unit                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------|------------|----------|------------|------------------------------|

| Management Power Output (MGMT_F                                                                                                                                                                                                      | PWR)              |                                |            |          |            |                              |

| Operating Input Voltage                                                                                                                                                                                                              | 3.3V/5.0V         | Vı                             | -36        | -48      | -75        | Vdc                          |

| Output Voltage Set-point                                                                                                                                                                                                             | 3.3V/5.0V         | V <sub>O, set</sub>            | -2.0       | _        | +2.0       | % V <sub>O, set</sub>        |

| $(V_1 = -48Vdc, I_0 = I_{O, max}, T_A = 25^{\circ}C)$                                                                                                                                                                                |                   |                                |            |          |            |                              |

| Output Voltage                                                                                                                                                                                                                       | 3.3V/5.0V         | Vo                             | -3.0       | _        | +3.0       | % V <sub>O, set</sub>        |

| (Over all operating input voltage, resistive                                                                                                                                                                                         |                   |                                |            |          |            |                              |

| Load and temperature conditions                                                                                                                                                                                                      |                   |                                |            |          |            |                              |

| until end of life)                                                                                                                                                                                                                   |                   |                                |            |          |            |                              |

| Output Regulation                                                                                                                                                                                                                    | 3.3V/5.0V         |                                |            |          |            |                              |

| Line (V <sub>I</sub> = VI,min to VI,max)                                                                                                                                                                                             |                   |                                | _          | 0.05     | 0.2        | %, $V_{O, set}$              |

| Load ( $I_O = I_{O, min}$ to $I_{O, max}$ )                                                                                                                                                                                          |                   |                                | _          | 0.05     | 0.2        | %, $V_{O, set}$              |

| Temperature $(T_A = T_{A, min} \text{ to } T_{A, max})$                                                                                                                                                                              |                   |                                | _          | _        | 1.00       | %, $V_{O, set}$              |

| Output Ripple and Noise                                                                                                                                                                                                              | 3.3V/5.0V         |                                |            |          |            |                              |

| Measured across 22μF Tantalum capacitor                                                                                                                                                                                              |                   |                                |            |          |            |                              |

| $VI = VI, nom T_A = 25^{\circ}C, lo = lo, max$                                                                                                                                                                                       |                   |                                |            |          |            |                              |

| RMS (5Hz to 20 MHz bandwidth)                                                                                                                                                                                                        |                   |                                | _          | _        | 25         | $mV_{rms}$                   |

| Peak-to-peak (5Hz to 20MHz bandwidth)                                                                                                                                                                                                |                   |                                | _          | _        | 75         | $mV_{p-p}$                   |

| External Load Capacitance                                                                                                                                                                                                            | 3.3V/5.0V         | $C_{O,max}$                    | 0          | _        | 1000       | μF                           |

| Output Current                                                                                                                                                                                                                       | 3.3V<br>5.0V      | lo<br>lo                       | 0          |          | 2.4<br>1.6 | Adc<br>Adc                   |

| Output Current-Limit Inception                                                                                                                                                                                                       | 3.3V<br>5.0V      | lo,lim<br>lo,lim               |            | 3<br>2.5 | _          | Adc<br>Adc                   |

| Output Short-circuit Current (RMS)                                                                                                                                                                                                   | 3.3V              | lo,sc                          | _          | 8        | _          | $A_{rms}$                    |

| , ,                                                                                                                                                                                                                                  | 5.0V              | lo,sc                          | -          | 6        | _          | $A_{rms}$                    |

| Dynamic Response (di/dt =0.1A/ $\mu$ s, V <sub>i</sub> in= VIn,nom, T <sub>A</sub> =25°C) Load change from I <sub>O</sub> = 50% to 75% of I <sub>O, max</sub> , Peak Deviation Settling Time (V <sub>O</sub> <10% of peak deviation) | 3.3V/5.0V         | V <sub>pk</sub> t <sub>s</sub> |            | 3<br>800 | 5          | %, V <sub>O, set</sub><br>μs |

| Turn-On Delay and Rise Times (Io = 80% of Io,max, T <sub>A</sub> =25°C)                                                                                                                                                              | 3.3V/5.0V         | Tdelay                         |            | 20       | 50         | msec                         |

| Output voltage overshoot<br>(Io = 80% of Io,max, VI = 48Vdc T <sub>A</sub> =25°C)                                                                                                                                                    | 3.3V/5.0V         |                                |            |          | 3%         | %, V <sub>O, set</sub>       |

| Output Over Voltage Protection                                                                                                                                                                                                       | 3.3V<br>5.0V      | Vo, limit                      | 3.7<br>5.6 |          | 5.4<br>7.0 | V                            |

# **General Specifications**

| Parameter                                                                                                                         | Min       | Тур       | Max | Unit    |

|-----------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|-----|---------|

| Calculated MTBF ( $P_{in}$ =80% of $P_{in, max}$ , $T_A$ =40°C, $V_{in}$ = -48Vdc) (Per Telcordia SR-332 Issue 1:Method 1 Case 3) | 1,565,825 |           |     | Hours   |

| Weight                                                                                                                            | _         | 29 (1.02) | _   | g (oz.) |

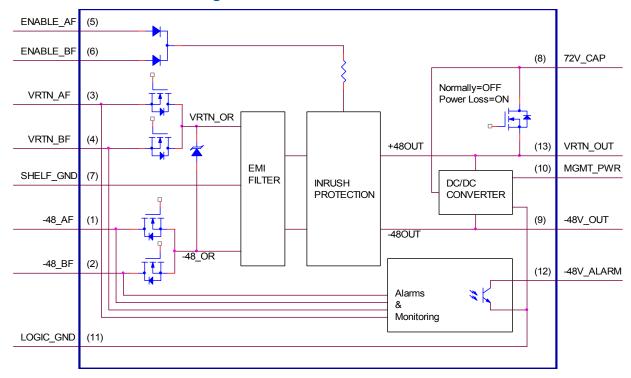

## PIM200X Internal Block Diagram

## **PIN FUNCTIONS**

| PIN NO. | PIN NAME                   | I/O | DESCRIPTION                                                     |

|---------|----------------------------|-----|-----------------------------------------------------------------|

| 1       | -48_AF                     | I   | -48V_A Feed (Externally Fused)                                  |

| 2       | -48_BF                     | I   | -48V_B Feed (Externally Fused)                                  |

| 3       | VRTN_AF                    | I   | VRTN_A Feed (Externally Fused)                                  |

| 4       | VRTN_BF                    | I   | VRTN_B Feed (Externally Fused)                                  |

| 5       | ENABLE AF                  | 1   | ENABLE_A Feed (Externally Fused)                                |

| 3       | LIVADEL_AI                 | '   | (Short Pin, connected to VRTN_A on the back plane)              |

| 6       | ENABLE BF                  | 1   | ENABLE_B Feed (Externally Fused)                                |

|         | LIVADEL_DI                 | '   | (Short Pin, connected to VRTN_B on the back plane)              |

| 7       | SHELF_GND                  | I/O | Shelf / Chassis / Safety Ground                                 |

| 8       | 72V_CAP                    | 0   | Holdup/Bulk capacitor output voltage                            |

| 9       | -48V_OUT                   | 0   | OR'd and Inrush Protected –48V Output Bus                       |

| 10      | MGMT_PWR                   | 0   | 3.3V / 5.0V Isolated Management Power Output ( w.r.t LOGIC_GND) |

| 11      | LOGIC_GND                  | I/O | Logic / Secondary / Isolated Ground                             |

| 12      | -48V ALARM                 | 0   | Opto-isolated -48V A/B Feed Loss or Open Fuse Alarm             |

| 12      | - <del>-1</del> 01/2/1/1/1 |     | (w.r.t LOGIC_GND)                                               |

| 13      | VRTN_OUT                   | 0   | OR'd and Inrush Protected VRTN Output Bus                       |

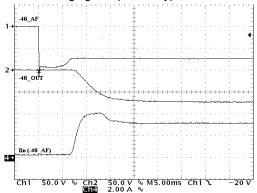

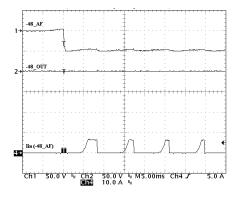

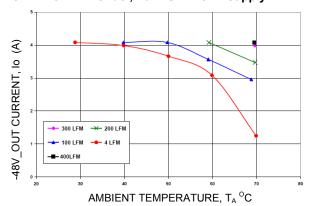

### **Characteristic Curves**

The following figures provide typical characteristics for the PIM200X modules at 25°C.

2-48\_AF

2-48\_OUT

-48\_OUT

-4

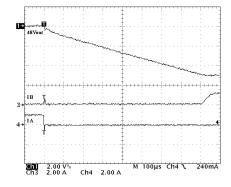

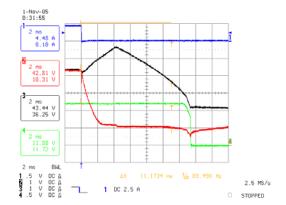

Figure 1. Inrush Current @ -75Vin & 3A Out CH1: -48\_AF, CH2: -48V\_OUT, CH4: lin(-48\_AF)

Figure 2. Inrush Current @ --48Vin & 0A Out CH1: -48\_AF, CH2: -48V\_OUT, CH4: lin(-48\_AF)

**Test Conditions:**

-48\_AF=-75Vdc, -48V\_BF=0Vdc I(-48V\_OUT)=3A, I(MGMT\_PWR)=0A C\_FLTR=220µF

Test Conditions:

-48\_AF=-48Vdc, -48V\_BF=0Vdc

I(-48V\_OUT)=0A, I(MGMT\_PWR)=0A

C\_FLTR=220µF

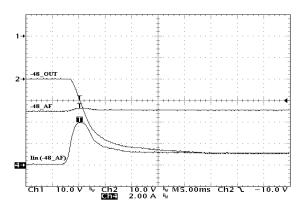

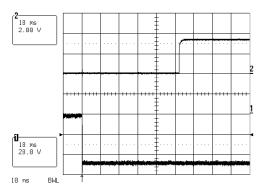

Figure 3. Power Up into Shorted Output CH1: -48\_AF, CH2: -48V\_OUT, CH4: lin(-48\_AF)

Figure 4. OR'ing Functionality when Feed A is shorted

CH1: -48V\_OUT, CH3: lin(-48\_BF)

CH4: lin(-48\_AF)

**Test Conditions:**

-48\_AF=-48Vdc, -48V\_BF=0Vdc I(-48V\_OUT)=0A, I(MGMT\_PWR)=0A C\_FLTR=220µF Test Conditions:

-48\_AF=-50Vdc, -48V\_BF=-45Vdc

$I(-48V_OUT) = 1A$

$C_FLTR=220\mu F$ ,  $C_HLDP=1000\mu F$

## Characteristic Curves (continued)

The following figures provide typical characteristics for the PIM200X modules at 25°C.

Figure 5. Input Voltage Turn-On Threshold

CH1: -48\_AF, CH2: -48V\_OUT,

CH4: lin(-48 AF)

#### **Test Conditions:**

-48\_AF=-48Vdc, -48V\_BF=0Vdc I(-48V\_OUT)=1A, I(MGMT\_PWR)=0A C\_FLTR=220µF

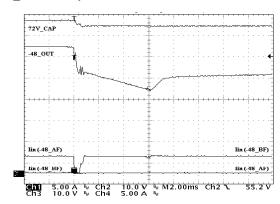

Figure 7. Loss of Feed A; Switchover to Feed B

CH1: lin(-48\_AF), CH2: -48V\_OUT, CH3: lin(-48\_BF), CH4: 72V\_CAP

#### **Test Conditions:**

- 1. Feed A (-48V\_AF=60V) > Feed B (-48V\_BF=48V)

- 2. Fast Loss of Feed A; Switchover to FeedB

- 3. I(-48V\_OUT)=4A, I(MGMT\_PWR)=2A

- 4. C\_FLTR=220μF, C\_HLDP=1,000μF

Figure 6. Input Voltage Turn-Off Threshold CH1: -48\_AF, CH2: -48V\_OUT,

CH4: lin(-48 AF)

#### **Test Conditions:**

-48\_AF=-48Vdc, -48V\_BF=0Vdc I(-48V\_OUT)=1A, I(MGMT\_PWR)=0A C FLTR=220µF

Figure 8. Holdup Performance; Loss of Feed A (with Feed B=0Vdc); Load=QBW CH1(Blue): lin(-48V\_AF), CH2(Red): 48\_AF, CH3(Black): 48V\_OUT, CH4(Green): 12Vout

#### **Test Conditions:**

- 1. 48\_AF= 43Vdc; 48V\_BF=0 Vdc

- 2. Pin=200W; 12Vout=14.3A; 3.3V=2.42A

- 3. C\_FLTR=100µF, C\_HLDP=Qty3 X 470µF

## Characteristic Curves (continued)

The following figures provide typical characteristics for the PIM200X modules at 25°C (unless specified otherwise).

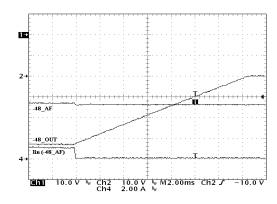

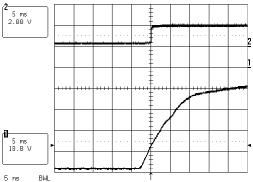

Figure 9. Typical Start-Up of MGMT\_PWR(3.3Vdc) with application of –48Vin.

CH1: -48\_AF, CH2: MGMT\_PWR (3.3Vdc) Output Test Conditions:

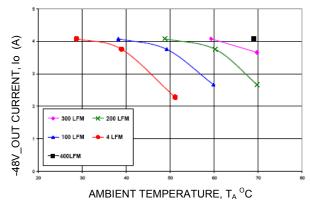

-48AF=-48Vdc; I(MGMT\_PWR)=2.4A

Figure 11. PIM 200F Output Current Derating versus Local Ambient Temperature and Airflow Test Conditions:

Vin = -48Vdc; 3.3V @ 2.46A; Longitudinal Orientation

Figure 10. -48V\_ALARM with Loss of Feed

CH1: -48V\_AF, CH2: -48\_ALARM Test Conditions:

-48AF=-48VB= -48Vdc; Turn Off -48VA supply

Figure 12. PIM 200 A Output Current Derating versus Local Ambient Temperature and Airflow Test Conditions:

Vin = -48Vdc; 5.0V @ 1.6A; Longitudinal Orientation

-38 to -75Vdc; 200W Input

## **Design Considerations**

#### Introduction

The PIM200X module is designed to support the Advanced Telecommunications Computing Architecture (ATCA) power entry distribution requirements for the Front Board / Blade per the PICMG 3.0 specifications.

The PICMG 3.0 specification defines the Mechanical, Shelf Management Interface, Power Distribution, Thermal, Data I/O and Regulatory requirements for the next generation of modular telecom architecture platform for use in Central Office telecom environments.

### **Input Pin Connections**

The ATCA board is specified to accept up to a maximum of 200W of input power via dual, redundant -48Vdc Feeds through the Zone 1 (Power and Management) Positronic connector, designated P10.

The power connector provides board to backplane engagement via pins of varying lengths. Please consult the PICMG 3.0 specifications for details.

The following are the design considerations of the input pin connections of the PIM200X to the ATCA power connector.

| From<br>ATCA<br>(P10 Connector) |             | Connection<br>Requirement |     | To<br>PIM200X |

|---------------------------------|-------------|---------------------------|-----|---------------|

| Pin                             | Pin         | Requirement               | Pin | Pin           |

| #                               | Designation |                           | #   | Designation   |

| 33                              | -48V_A      | Via Fuse(F3)              | 1   | -48V_AF       |

| 34                              | -48V_B      | Via Fuse(F4)              | 2   | -48V_BF       |

| 28                              | VRTN_A      | Via Fuse(F1)              | 3   | VRTN_AF       |

| 29                              | VRTN_B      | Via Fuse(F2)              | 4   | VRTN_BF       |

| 30                              | EARLY_A*    | Via<br>Resistor(R1)       | 1   | -48V_AF       |

| 31                              | EARLY_B*    | Via<br>Resistor(R2)       | 2   | -48V_BF       |

| 32                              | ENABLE_A    | Via Fuse(F5)              | 5   | ENABLE_AF     |

| 27                              | ENABLE_B    | Via Fuse(F6)              | 6   | ENABLE_BF     |

| 26                              | LOGIC_GND   | Direct                    | 11  | LOGIC_GND     |

| 25                              | SHELF_GND   | Direct                    | 7   | SHELF_GND     |

<sup>\*</sup> Optional

The first pins to mate in the ATCA power connector are the EARLY\_A, EARLY\_B, the two grounds (LOGIC\_GND, SHELF\_GND) and the two returns (VRTN\_A, VRTN\_B); followed by staggered connections of -48V\_A and -48V\_B power Feeds. The last pins to engage are the two short pins, ENABLE\_A

& ENABLE\_B. The ATCA backplane connects the ENABLE\_A to VRTN\_A, ENABLE\_B to VRTN\_B, EARLY A to -48V A and EARLY B to -48V B.

Optional EARLY\_A & EARLY\_B Connections:

During hot insertion of the ATCA board, the Inrush

Control circuit limits the surge current to the C\_FLTR

capacitor. However, due to the presence of a small

amount of EMI filter capacitance (located before the

Inrush Control circuit), there is a possibility of a surge

current that results in a voltage sag for 5 to 10

microseconds. In most cases this should not be of

concern because all the ATCA Boards and FRU's on

the -48V bus should be able to ride thru a

5msec/0Volt transient event per the PICMG 3.0

specifications. In case this is undesirable, it is

recommended that Precharge resistors, R1 & R2 (15

Ohms) should be connected as described in the

Typical Application circuit.

#### **Output Pin Connections**

The out pin connections of the PIM200X to the system board is described below:

|          | From<br>PIM200X    |          | To<br>Board        | Notes |

|----------|--------------------|----------|--------------------|-------|

| Pin<br># | Pin<br>Designation | Terminal | Component          | Notes |

| 9        | -48V_OUT           | Vin(-)   | DC/DC<br>Converter | (1)   |

| 13       | VRTN_OUT           | Vin(+)   | DC/DC<br>Converter | (1)   |

| 8        | 72V_CAP            | +ve      | C_HLDP             | (2)   |

| 10       | MGMT_PWR           | Vcc      | IPM/               | (3)   |

| 12       | -48V_ALARM         |          | System Controller  | (4)   |

#### Notes:

### (1) -48V Main Output Bus:

(Signal Names: -48V\_OUT & VRTN\_OUT)

This is the main -48V output bus that provides the payload power to the downstream (one or more) DC/DC converters. The PIM200X module does not regulate or provide isolation from the input -48V A/B feeds.

The main functionality of the module is to provide - 48V A/B Feeds OR'ing, inrush protection for hot swap capability and EMI filtering to attenuate the noise generated by the downstream DC/DC converters.

The -48V\_OUT pin connects to the Vin(-) pin and the VRTN\_OUT pin connects to the Vin(+) pin of the DC/DC converter(s).

- The -48V\_OUT bus may require a fuse depending on the power and fusing requirements of the DC/DC converter(s).

- Input filtering of the DC/DC converter is provided by C\_FLTR close to the input pins of the DC/DC converter(s); additional high frequency decoupling ceramic capacitors (0.01 to 0.1µF are strongly recommended for improved EMI performance.

- The maximum C\_FLTR capacitance across all the downstream DC/DC converters should not exceed 220µF. The recommended capacitor voltage rating should be >/= 100Vdc.

- The minimum C\_FLTR capacitance (200μF) recommendation is based on meeting the EMI requirements. Based on end systems test, the capacitance may be lowered if real estate is an issue. As a minimum, 50 μF to 100 μF is strongly recommended to stabilize the line impedance for proper startup of the DC/DC converter. Refer to the DC/DC converter's data sheet for the recommended capacitor.

## (2) Holdup / Bulk Capacitor Output (72V\_CAP)

This output provides the high voltage (nominal 72Vdc) to charge the C\_BULK capacitor(s) to allow the ATCA board to meet the 5ms. 0Volts transient requirements.

- The 72V\_CAP connects to the +ve terminals of the C\_HLDP capacitors while the –ve terminals of the C\_HLDP connects to the -48V OUT bus.

- Since the 72V\_CAP output is regulated to 72Vdc (+3%/-5%) and the capacitors are off line during normal operation, the capacitors may be selected with voltage rating of >/= 80V to minimize the real estate on the board.

- The C\_HLDP capacitance is dependent on the system power and the holdup time requirements based on the following formula

$$C \quad HLDP(\mu F) \ge [P_{out}(W) * \{T_{holdup}(ms) + 1.7\}]/1.9$$

The capacitance tolerance (normally +20%) should be added to the calculated value.

Bleed Resistor ( R\_Bleed): The PICMG 3.0 specifications requires a discharge mechanism (e.g. bleed resistor) to discharge the holdup/bulk capacitance to less than - 60Vdc and less than 20 joules within one second of disconnection from the backplane. This requirement is fulfilled by installing R\_Bleed resistor that is selected based on the C\_HLDP selected in the previous step. The formula for selecting the resistor is:

$R\_Bleed(\Omega) \le 5.485/C\_HLDP(F)$

For 200W and 9.3 ms holdup requirements, this results in a 3.9 Kohm resistor with 1W rating.

Worst case power dissipation of R\_Bleed (=3.9Kohms) @ -36V is 0.33W.

The R\_Bleed is connected across the 72V\_CAP and VRTN\_OUT pins of the PIM200X.

# (3) Management Power (MGMT\_PWR)

The MGMT\_PWR output is an isolated secondary voltage ( 3.3V for PIM200F or 5.0V for PIM200A) referenced to LOGIC\_GND that provides 8W(maximum) power to the IPM Controller for the ATCA board or to the power up system controller for other applications.

- Per PICMG 3.0 Specs, the ATCA board shall not consume more than 10W of input power; this includes the standby power of PIM200X (typically 1.7W) as well as all the on board DC/DC power converters. It is the responsibility of the board designer to insure that this requirement is met prior to power-up rights have been negotiated with the Shelf Manager.

- The management power is available even when the input voltage is down to -36Vdc.

- No additional output capacitors are required, but a 22µF tantalum and a 0.01 to 0.1µF ceramic capacitors are highly recommended to contain the switching ripple and noise.

- Higher output capacitance may be required in case of large input line or output load transient conditions.

# (4) -48V Feed Loss or Open Fuse Alarm (-48V\_ALARM)

The -48V\_ALARM output is an opto-isolated signal internally referenced to the LOGIC\_GND. The signal is an open collector output that requires an external pull up resistor. A 3.3K pull up resistor to 3.3V, MGMT\_PWR ( for PIM200F) should suffice. During normal operation, the signal is LO (opto conducting). During fault condition, the opto shall stop conducting and the alarm signal shall assume a HI state.

## **Safety Considerations**

For the system safety agency approval the power module must be installed in compliance with the spacing and separation requirements of the end-use safety agency standards, i.e., UL 60950-1, CSA

-38 to -75Vdc; 200W Input

C22.2 No. 60950-1-03, and VDE 0850:2001-12 (EN60950-1) Licensed.

The power input to these units is to be provided with a maximum of 10 Amps fuses with a voltage rating of at least 75Vdc.

Refer to "Thermal Considerations" section for additional safety considerations.

## **Feature Description**

## A/B Feed OR'ing

The module provides dedicated OR'ing functionality to both Feeds A & B and their corresponding returns. The following pairs of signals are OR'd within the module:

-48V\_AF / -48\_BF, VRTN\_AF / VRTN\_BF, and ENABLE AF/ENABLE B.

The -48V A/B feeds and their corresponding returns are OR'd via N-channel MOSFET power devices resulting in a highly efficient system compared to conventional diode OR'ing scheme.

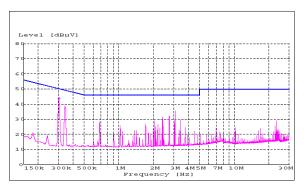

## **EMC Filtering**

The module incorporates an EMI filter that is designed for the ATCA board to help meet the conducted emissions requirements of CISPR 22 Class B when used in conjunction with Lineage Power DC/DC converters approved for ATCA applications. The following insertion loss table is provided as filter performance guidelines.

| Parameter                        | Typical | Unit |

|----------------------------------|---------|------|

| Common-Mode Insertion Loss       |         |      |

| 50 Ohms circuit, 200kHz          | 25      | dB   |

| 50 Ohms circuit, 500kHz          | 30      | dB   |

| 50 Ohms circuit, 1MHz            | 40      | dB   |

| Differential-mode Insertion Loss |         |      |

| 50 Ohms circuit, 200kHz          | 80      | dB   |

| 50 Ohms circuit, 500kHz          | 70      | dB   |

| 50 Ohms circuit, 1MHz            | 60      | dB   |

The following Figure 13 depicts the Class B EMI performance of PIM200F when tested with QBW018A0B1 on a stand alone basis (ATCA form factor load board with resistive loads and only power, return and chassis connections to the backplane). The external filtering components are identified in the Typical Application circuit.

Figure 13. Typical Class B EMC signature of PIM200F with QBW018A0B1 module.

For Safety and noise considerations, copper traces must not be routed directly beneath the power module (PWB top layer). C\_EMI capacitors must make direct connections (preferably without vias) to the DC/DC module pins with as much copper width as possible. In case vias are necessary, allow for multiple connections to the inner plane with vias placed outside the footprint of the module. For additional layout guide-lines, refer to Lineage Power's's FLT007A0 Input Filter Module data sheet.

# Inrush Current Control / Hot Plug Functionality

The module provides inrush current control / hot plug capability. The peak value of the inrush current and the duration complies with the PICMG 3.0's Inrush Transient specifications. The specifications shall be met with the external C\_HLDP and C\_FLTR capacitances as specified in the previous sections.

The unique design of the module where the large energy storage capacitors are segregated from the input filter capacitors allows the module to meet the stringent PICMG's inrush transient specifications. In conventional designs where the energy storage capacitors and the filter capacitors are in parallel, it is extremely difficult to meet the inrush transient specifications without over sizing the inrush control power FET.

#### A/B Feed / Fuse Alarm (-48V ALARM)

The module monitors the A & B feeds as well as the status of the A&B feed fuses and provides an optoisolated signal in case of loss of a feed or the opening of any of the fuses. The response time of the fault condition is < 100  $\mu$ sec. The alarm signal indicates normal operation when the optocoupler transistor is conducting and a fault condition by an off state.

# Holdup Capacitor Charging Current (72V\_CAP)

The module employs a unique feature to charge and recharge the external energy storage holdup/bulk capacitors (C\_HLDP) within seconds from the application of power to a nominal voltage of 72Vdc (+3%/-5%) resulting in significant reduction in the real estate on the board in order to comply with the PICMG 3.0's 0 volt/5msec transient requirements. Since the 72V\_CAP is also regulated, there is further reduction in real estate board because now 80V capacitors with higher capacitance can be used instead of the >/= 100Vdc caps required in conventional designs. The maximum rate of input voltage change (dv/dt) shall not exceed 5V/ms when the -72V\_CAP output is switched on the -48V OUT/VRTN OUT bus.

The holdup capacitors are switched on automatically when there is a loss of power on both feeds A & B or both feeds have dropped below –38V (typical).

Upon restoration of normal power on either or both feeds, the holdup capacitors automatically go off line and are recharged for the next power loss event.

Note 1: The holdup capacitors and the bleed resistor are installed external to the module.

Note 2: The PICMG 3.0's requirements for the 0 Vdc transient for 5ms is normally interpreted as the holdup time requirement by many. In actuality, when one considers the additional specification of 50V/ms fall time and 12.5 V/ms rise time to and from the 0Vdc condition, this leads to a 9.3ms of total hold up time requirement when power is interrupted at -43Vdc. The 72V\_CAP output provided by the module to charge the bulk capacitors provides a tremendous advantage over conventional designs in terms of real estate requirements on the board (1,400 $\mu$ F vs 6,000 $\mu$ F) with the added benefit of the usage of 80V capacitor rating vs >/=100V.

The holdup time,  $T_{\text{holdup}}$ , is defined for power loss at -43Vdc input and the C\_HLDP maintaining -48V\_OUT bus to at least -36Vdc (which is the minimum operating voltage of the downstream DC/DC bus converter).

Note 3: Bleed Resistor (R\_Bleed): Normally, the bleed resistor is not required as there is sufficient standby current drain within the module to bleed the holdup capacitors from 75V to 60V in 1 second as specified in the PICMG 3.0. Again, due to the PIM200X's unique design, the placement of the bleed resistor results in significantly less power dissipation compared with conventional designs where the bleed resistor is sized for -75Vdc continuous maximum voltage and -100V transients.

### Over Current Protection (-48V\_OUT Bus)

To provide protection in a fault (output overload or short circuit) condition, the unit is equipped with internal current-limiting circuitry. The unit can endure current overload conditions continuously or shutdown due to thermal protection depending on operating ambient temperature conditions. The unit will restart automatically once the overload condition is removed.

### **Input Under Voltage Lockout**

At input voltages below the input undervoltage lockout threshold limit ( $V_{\text{UVLO}}$ ), the module operation is disabled. The module will begin to operate at an input voltage above the undervoltage lockout turn-on threshold( $V_{\text{UVHI}}$ ). Please see the Electrical Specifications Table for the specified trip points.

## **Transient Over Voltage Protection**

The module incorporates a Transient Voltage Suppressor (TVS). This feature helps protect the module and the downstream DC/DC converters from input voltage transients exceeding -75Vdc. The TVS is rated for 1500W of Peak Pulse Power with the Breakdown Voltage ( $V_{BR}$ ) of 77.8V to 86.0V.

#### Input Reverse polarity protection

The module shall not be damaged from reverse polarity connection in the event of miswiring of either input feeds at the shelf input terminals.

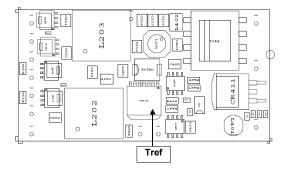

#### **Over Temperature Protection**

To provide over temperature protection in a fault condition, the unit will shutdown if the thermal reference point  $T_{\rm ref}$  (Figure 15), exceeds 115°C (typical). The thermal shutdown is not intended as a guarantee that the unit will survive temperatures beyond its rating. The module will automatically restart after it cools down.

#### Management Power (MGMT PWR)

- The module provides up to 8W of 3.3V (PIM300F) or 5.0V (PIM300A) of isolated output power referred to LOGIC\_GND.

- The management power is available automatically as soon as the input voltage levels are within –36Vdc to –75Vdc.

- The output is short circuit and over voltage protected with low ripple and noise.

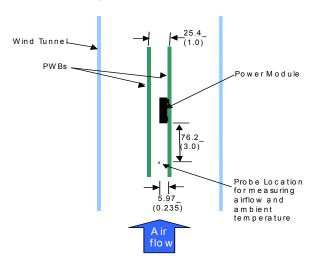

### **Thermal Considerations**

Power modules operate in a variety of thermal environments; however, sufficient cooling should be provided to help ensure reliable operation.

-38 to -75Vdc; 200W Input

Considerations include ambient temperature, airflow, module power dissipation, and the need for increased reliability. A reduction in the operating temperature of the module will result in an increase in reliability. The thermal data presented here is based on physical measurements taken in a wind tunnel. The test setup is shown in Figure 14.

Figure 15. Thermal Test Set-up

Note that the airflow is parallel to the long axis of the module as shown in Figure 15. The derating data applies to airflow in either direction of the module's long axis.

Figure 16. T<sub>ref</sub> Temperature measurement location

The thermal reference point, T<sub>ref</sub> used in the specifications is shown in Figure 16. For reliable operation this temperature should not exceed 115°C.

The output power of the module should not exceed the rated input power of the module i.e. 200W.

Please refer to the Application Note "Thermal Characterization Process For Open-Frame Board-Mounted Power Modules" for a detailed discussion of thermal aspects including maximum device temperatures.

#### **Heat Transfer via Convection**

Increased airflow over the module enhances the heat transfer via convection. Thermal derating curves showing the maximum output current that can be delivered by the module versus local ambient temperature ( $T_A$ ) for natural convection and up to 2m/s (400 ft./min) are shown in the Characteristics Curves (Figs 11 & 12).

# Manufacturing Considerations Lead Free Soldering Information

The RoHS-compliant through-hole products use the SAC (Sn/Ag/Cu) Pb-free solder and RoHS-compliant components. They are designed to be processed through single or dual wave soldering machines. The pins have an RoHS-compliant finish that is compatible with both Pb and Pb-free wave soldering processes. A maximum preheat rate of 3°C/s is suggested. The wave preheat process should be such that the temperature of the power module board is kept below 210°C. For Pb solder, the recommended pot temperature is 260°C, while the Pb-free solder pot is 270°C max. If additional information is needed, please consult with your Lineage Power representative for more details.

# Post Solder Cleaning and Drying Considerations

Post solder cleaning is usually the final circuit-board assembly process prior to electrical board testing. The result of inadequate cleaning and drying can affect both the reliability of a power module and the testability of the finished circuit-board assembly. For guidance on appropriate soldering, cleaning and drying procedures, refer to Lineage Power's *Board Mounted Power Modules: Soldering and Cleaning* Application Note (AP01-056EPS)

## **Mechanical Outline for PIM200X Module**

Dimensions are in millimeters and (inches).

Tolerances: x.x mm  $\pm$  0.5 mm (x.xx in.  $\pm$  0.02 in.) [unless otherwise indicated] x.xx mm  $\pm$  0.25 mm (x.xxx in  $\pm$  0.010 in.)

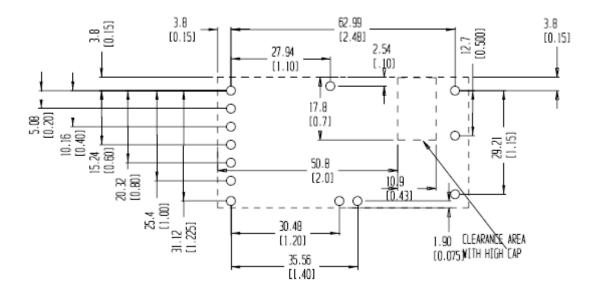

## **Recommended Pad Layout**

Dimensions are in millimeters and (inches).

Tolerances: x.x mm  $\pm$  0.5 mm (x.xx in.  $\pm$  0.02 in.) [unless otherwise indicated]

x.xx mm  $\pm$  0.25 mm (x.xxx in  $\pm$  0.010 in.)

#### NOTES:

1. For the pins, use 1.27(mm) / 0.050(in) diameter Plated Trough Hole

## **Ordering Information**

Please contact your Lineage Power's Sales Representative for pricing, availability and optional features.

Table 1. Device Code

| Input<br>Voltage | Power<br>Rating | Auxiliary<br>Output<br>Voltage | Auxiliary<br>Output<br>Current | Options          | Product codes | Comcodes    |

|------------------|-----------------|--------------------------------|--------------------------------|------------------|---------------|-------------|

| -38 to -75 Vdc   | 200W            | 3.3Vdc                         | 2.4A                           |                  | PIM200F       | 108994471   |

| -38 to -75 Vdc   | 200W            | 3.3Vdc                         | 2.4A                           | RoHS             | PIM200FZ      | CC109101813 |

| -38 to -75 Vdc   | 200W            | 3.3Vdc                         | 2.4A                           | Basic Insulation | PIM200F-B     | CC109101912 |

| -38 to -75 Vdc   | 200W            | 5.0Vdc                         | 1.6A                           |                  | PIM200A       | 108996286   |

| -38 to -75 Vdc   | 200W            | 5.0Vdc                         | 1.6A                           | RoHS             | PIM200AZ      | CC109106762 |

<sup>\*</sup> Consult factory for availability.

**Table 2. Device Options**

| Option                      | Device Code Suffix |

|-----------------------------|--------------------|

| Basic Insulation            | -В                 |

| RoHS Compliant (Lead Free)  | -Z                 |

| Short pins: 3.68mm ± 0.25mm | 6                  |

| (0.145 in. ± 0.010 in.)     | -6                 |

| Short pins: 2.79mm ± 0.25mm | 2                  |

| (0.110 in. ± 0.010 in.)     | -8                 |

**Table 3. Related Products**

| Description                                                      | Product Code  | Comcode     |

|------------------------------------------------------------------|---------------|-------------|

| PIM Evaluation Board                                             | N/A           | 848755868   |

| 200W Bus converter; 36-75Vdc Input,12Vdc / 18A Output            | QBW018A0B1    | 108989356   |

| 200W Bus converter; 36-75Vdc Input,12Vdc / 18A Output            | QBW018A0B1Z*  | TBD         |

| (RoHS compliant)                                                 |               |             |

| 200W Bus converter; 36-75Vdc Input,12Vdc / 18A Output            | QBW018A0B1-TZ | CC109101846 |

| (RoHS compliant & designed for high capacitance loads e.g. VRMs) |               |             |

| 300W Bus converter; 36-75Vdc Input,12Vdc / 25A Output            | QBW025A0B1    | CC109102464 |

| 300W Bus converter; 36-75Vdc Input,12Vdc / 25A Output            | QBW025A0B1Z*  | TBD         |

| (RoHS compliant)                                                 |               |             |

<sup>\*</sup> Consult factory for availability.

World Wide Headquarters

Lineage Power Corporation

601 Shiloh Road, Plano, TX 75074, USA

+1-800-526-7819

(Outside U.S.A.: +1-972-244-9428)

www.lineagepower.com

e-mail: techsupport1@lineagepower.com

Asia-Pacific Headquarters

Tel: +65 6593 7211

Europe, Middle-East and Africa Headquarters Tel: +49 898 780 672 80

India Headquarters Tel: +91 80 28411633

Lineage Power reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application. No rights under any patent accompany the sale of any such product(s) or information.

$Lineage\ Power\ DC-DC\ products\ are\ protected\ under various\ patents.\ Information\ on\ these\ patents\ is\ available\ at\ www.lineagepower.com/patents.$

© 2009 Lineage Power Corporation, (Plano, Texas) All International Rights Reserved.