### **Bus Compatible Digital PWM Controller, IXDP 610**

#### Description

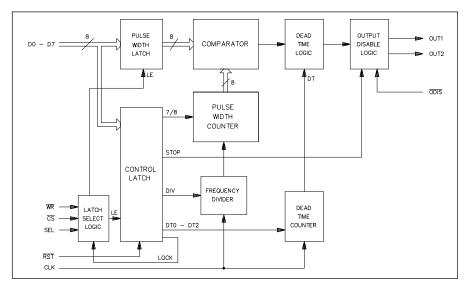

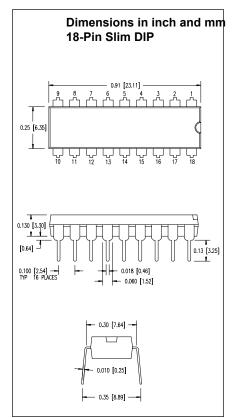

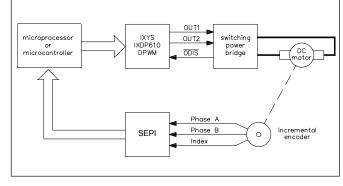

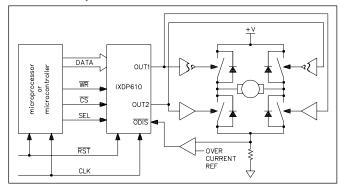

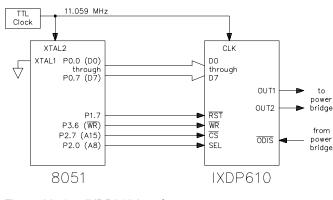

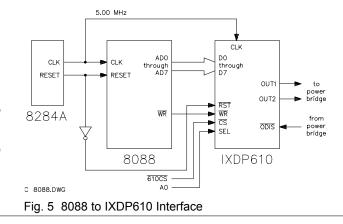

The IXDP610 Digital Pulse Width Modulator (DPWM) is a programmable CMOS LSI device which accepts digital pulse width data from a microprocessor and generates two complementary, non-overlapping, pulse width modulated signals for direct digital control of switching power bridge. The DPWM is designed to be operated under the direct control of a microprocessor and interfaces easily with most standard microprocessor and microcomputer buses. The IXDP610 is packaged in an 18-Pin slim DP.

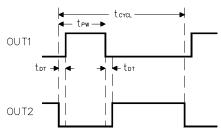

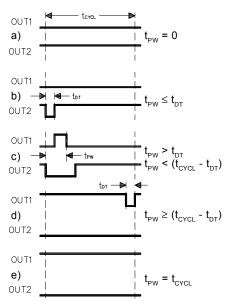

The PWM waveform generated by the IXDP610 results from comparing the output of the Pulse Width counter to the number stored in the Pulse Width Latch (see below). A programmable "dead-time" is incorporated into the PWM waveform. The Dead-Time Logic disables both outputs on each transition of the Comparator output for the required dead-time interval.

The output stage provides complementary PWM output signals capable of sinking and sourcing 20 mA at TTL voltage levels. The Output Disable logic can be activated either by software or hardware. This facilitates cycle-by-cycle current-limit, short-circuit, over-temperature, and desaturation protection schemes.

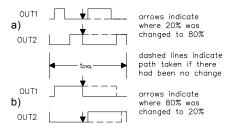

The IXDP610 is capable of operating at PWM frequencies from zero to 390kHz: the dead-time is programmable from zero to 14 clock cycles (0 to 11 % of the PWM cycle), which allows operation with fast power MOSFETs, IGBTs, and bipolar power transistors. A trade-off between PWM frequency and resolution is provided by selecting the counter resolution to be 7-bit or 8-bit. The 20 mA output drive makes the IXDP610 capable of directly driving opto isolators and Smart Power devices. The fast response to pulse width commands is achieved by instantaneous change of the outputs to correspond to the new command. This eliminates the one-cycle delay usually associated with other digital PWM implementations.

#### Features

- Microcomputer bus compatible

- Two complementary outputs for direct control of a switching power bridge

- Dynamically programmable pulse width ranges from 0 to 100 %

- Two modes of operation: 7-bit or 8bit resolution

- Switching frequency range up to 390 kHz

- Programmable Dead-time Counter prevents switching overlap

- Cycle-by-Cycle disable input to protect against over-current, overtemperature, etc.

- Outputs may be disabled under software control

- Special locking bit prevents damage to the stage in the event of a software failure

- 18-pin slim DIP package

| Symbol                             | Definition                | Maximum Ra                 | Maximum Ratings |  |  |

|------------------------------------|---------------------------|----------------------------|-----------------|--|--|

| V <sub>cc</sub>                    | Supply voltage            | -0.3 5.5                   | V               |  |  |

| V <sub>cc</sub><br>V <sub>IN</sub> | Input voltage             | -0.3 V <sub>cc</sub> + 0.3 | V               |  |  |

| V <sub>out</sub>                   | Output voltage            | -0.3 V <sub>cc</sub> + 0.3 | V               |  |  |

| P <sub>D</sub>                     | Maximum power dissipation | 500                        | mW              |  |  |

| T <sub>stg</sub>                   | Storage temperature range | -40 125                    | °C              |  |  |

## LIXYS

| Symbol                                                                                                                                                                                                                                                    | Definition                                                                                                                                                                                                                                    | Definition Maximum Ratings Operating Range                                                                                                 |      |                                                                                            |                                           | tings                                     | Numbers in the Fig. 3 to 6 corres-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                                                                                                                                                                                                           | Operating Mange                                                                                                                                                                                                                               |                                                                                                                                            |      | min.                                                                                       | max.                                      |                                           | ponding to the time values on the bottom left of this page.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| V <sub>cc</sub><br>T <sub>A</sub>                                                                                                                                                                                                                         | Supply voltage<br>Operating free air te                                                                                                                                                                                                       | mperature                                                                                                                                  |      | 4.5<br>-40                                                                                 | 5.5<br>85                                 | ∨<br>°C                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| Symbol                                                                                                                                                                                                                                                    | Definition/Conditio<br>(C                                                                                                                                                                                                                     | <b>n</b><br>)ver operating range, u                                                                                                        |      | therwis<br>typ.                                                                            |                                           | ified)                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| V <sub>IH(CMOS)</sub>                                                                                                                                                                                                                                     | Input High Voltage                                                                                                                                                                                                                            | ODIS                                                                                                                                       | 3.8  |                                                                                            | V <sub>cc</sub> +                         | 0.3 V                                     | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| V <sub>IL(CMOS)</sub>                                                                                                                                                                                                                                     | Input Low Voltage                                                                                                                                                                                                                             | ODIS                                                                                                                                       | -0.3 |                                                                                            | 1.2                                       | V                                         | WR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| V <sub>H</sub>                                                                                                                                                                                                                                            | Input Hysteresis                                                                                                                                                                                                                              | ODIS                                                                                                                                       | 0.3  | 0.5                                                                                        |                                           | V                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| V <sub>OH</sub>                                                                                                                                                                                                                                           | Output High Voltage                                                                                                                                                                                                                           | OUT1 I <sub>OH</sub> = -20 mA<br>OUT2                                                                                                      | 2.4  |                                                                                            |                                           | V                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| $V_{\text{ol}}$                                                                                                                                                                                                                                           | Output Low Voltage                                                                                                                                                                                                                            | OUT1 I <sub>ol</sub> = 20 mA<br>OUT2                                                                                                       |      |                                                                                            | 0.4                                       | V                                         | Fig. 3 Write operation timing diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| $\mathbf{V}_{\text{ih(ttl)}}$                                                                                                                                                                                                                             | Input High Voltage                                                                                                                                                                                                                            | All Inputs<br>Except ODIS                                                                                                                  | 2.0  |                                                                                            | V <sub>cc</sub> +                         | 0.3 V                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| V <sub>IL(TTL)</sub>                                                                                                                                                                                                                                      | Input Low Voltage                                                                                                                                                                                                                             | All Inputs<br>Except ODIS                                                                                                                  | -0.3 |                                                                                            | 0.8                                       | V                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| l <sub>u</sub>                                                                                                                                                                                                                                            | Input Leakage<br>Current                                                                                                                                                                                                                      | All Inputs<br>0 < V <sub>I</sub> < V <sub>cc</sub>                                                                                         | -10  | -0.1                                                                                       | 10                                        | μA                                        | OUTI OR OUT2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| I <sub>cc</sub>                                                                                                                                                                                                                                           | Power Supply<br>Current                                                                                                                                                                                                                       | f <sub>clk</sub> = 5 MHz<br>V <sub>IH</sub> = V <sub>cc</sub> or 0                                                                         |      | 3.5                                                                                        | 10                                        | mA                                        | Fig. 4 Output disable to outputs off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                               |                                                                                                                                            |      |                                                                                            |                                           |                                           | ——) timina                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Symbol                                                                                                                                                                                                                                                    | Definition/Conditio                                                                                                                                                                                                                           | <b>n</b><br>(T <sub>A</sub> = 25°C, V <sub>CC</sub>                                                                                        |      | aracteri<br>10 %,                                                                          |                                           |                                           | —— <sup>J</sup> timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Symbol<br>No. see<br>Fig. 3-6                                                                                                                                                                                                                             | Definition/Conditio                                                                                                                                                                                                                           |                                                                                                                                            |      | : 10 %,<br>  -40                                                                           |                                           |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| No. see<br>Fig. 3-6                                                                                                                                                                                                                                       | Definition/Conditio                                                                                                                                                                                                                           | (T <sub>A</sub> = 25°C, V <sub>CC</sub><br><b>typ</b> .                                                                                    |      | : 10 %,<br>  -40                                                                           | C1 = 5<br>85°C                            |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

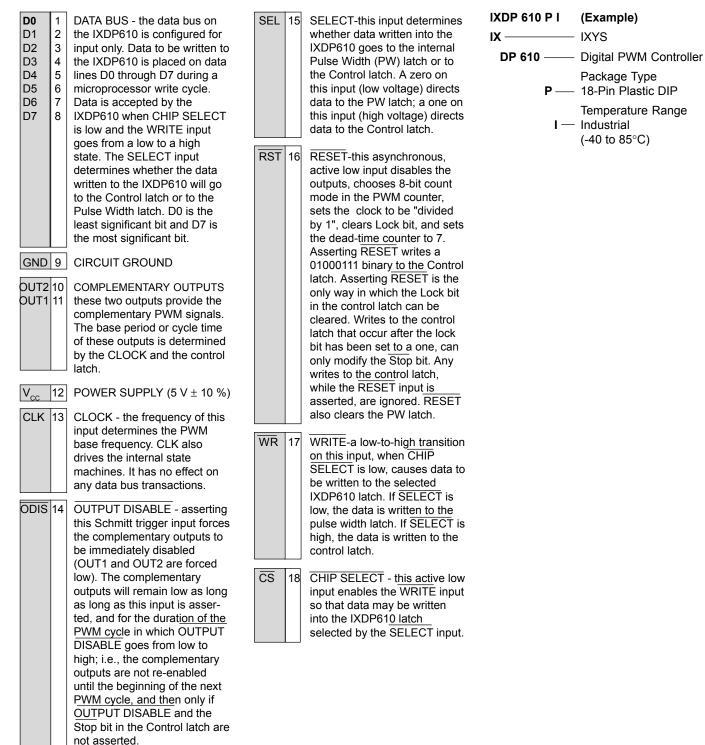

| No. see<br>Fig. 3-6<br>1 $t_{AVWL}$                                                                                                                                                                                                                       |                                                                                                                                                                                                                                               | $(T_A = 25^{\circ}C, V_{CC}$<br>typ.                                                                                                       |      | 10 %,<br>-40<br>min.                                                                       | C1 = 5<br>85°C                            | 0 pF)                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| No. see<br>Fig. 3-6<br>1 t <sub>avwL</sub><br>2 t <sub>wHAX</sub>                                                                                                                                                                                         | SEL Stable to WR Low                                                                                                                                                                                                                          | $(T_A = 25^{\circ}C, V_{CC}$<br>typ.                                                                                                       |      | 10 %,<br>-40<br>min.<br>5                                                                  | C1 = 5<br>85°C                            | 0 pF)                                     | OUT 1 or OUT2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| No. see<br>Fig. 3-6<br>1 t <sub>avwL</sub><br>2 t <sub>wHAX</sub><br>3 t <sub>SLWL</sub>                                                                                                                                                                  | SEL Stable to WR Low                                                                                                                                                                                                                          | (T <sub>A</sub> = 25°C, V <sub>CC</sub><br><b>typ</b> .                                                                                    |      | 10 %,<br>-40<br>min.<br>5<br>10                                                            | C1 = 5<br>85°C                            | 0 pF)<br>ns<br>ns                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| No. see<br>Fig. 3-6<br>1 t <sub>avwL</sub><br>2 t <sub>wHAX</sub><br>3 t <sub>sLWL</sub><br>4 t <sub>wHSH</sub>                                                                                                                                           | SEL Stable to $\overline{WR}$ Low<br>SEL Stable after $\overline{WF}$<br>$\overline{CS}$ Low to $\overline{WR}$ Low                                                                                                                           | (T <sub>A</sub> = 25°C, V <sub>CC</sub><br><b>typ</b> .                                                                                    |      | 10 %,<br>-40<br>min.<br>5<br>10<br>5                                                       | C1 = 5<br>85°C                            | 0 pF)                                     | OUT 1 or OUT2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| No. see<br>Fig. 3-6<br>1 $t_{AVWL}$<br>2 $t_{WHAX}$<br>3 $t_{SLWL}$<br>4 $t_{WHSH}$<br>5 $t_{WLWH}$                                                                                                                                                       | SEL Stable to WR Low<br>SEL Stable after WR<br>CS Low to WR Low<br>CS High after WR H<br>WR Pulse Width                                                                                                                                       | (T <sub>A</sub> = 25°C, V <sub>cc</sub><br>typ.<br>R High<br>igh<br>8                                                                      |      | 10 %,<br>-40<br>min.<br>5<br>10<br>5<br>5<br>5                                             | C1 = 5<br>85°C                            | 0 pF)                                     | OUT 1 or OUT2<br>WR<br>Fig. 5 Stop to outputs off timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| No. see<br>Fig. 3-6<br>1 t <sub>avwL</sub><br>2 t <sub>wHAX</sub><br>3 t <sub>sLwL</sub><br>4 t <sub>wHSH</sub><br>5 t <sub>wLWH</sub><br>6 t <sub>DVWH</sub>                                                                                             | SEL Stable to WR Low<br>SEL Stable after WR<br>CS Low to WR Low<br>CS High after WR H<br>WR Pulse Width<br>Data Valid to WR High                                                                                                              | (T <sub>A</sub> = 25°C, V <sub>cc</sub><br><b>typ</b> .<br>R High<br>igh<br>8<br>gh                                                        |      | 10 %,<br>-40<br>min.<br>5<br>10<br>5<br>5<br>5<br>20                                       | C1 = 5<br>85°C                            | 0 pF)<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns | OUT 1 or OUT2<br>WR<br>Fig. 5 Stop to outputs off timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| No. see<br>Fig. 3-6<br>1 t <sub>avwL</sub><br>2 t <sub>wHAX</sub><br>3 t <sub>sLwL</sub><br>4 t <sub>wHSH</sub><br>5 t <sub>wLWH</sub><br>6 t <sub>DVWH</sub><br>7 t <sub>wHDX</sub>                                                                      | SEL Stable to WR Low<br>SEL Stable after WR<br>CS Low to WR Low<br>CS High after WR H<br>WR Pulse Width<br>Data Valid to WR Hig<br>Data Held after WR                                                                                         | (T <sub>A</sub> = 25°C, V <sub>cc</sub><br><b>typ</b> .<br>R High<br>igh<br>8<br>gh                                                        |      | 10 %,<br>-40<br>min.<br>5<br>10<br>5<br>5<br>20<br>5                                       | C1 = 5<br>85°C                            | 0 pF)                                     | OUT 1 or OUT2<br>WR<br>Fig. 5 Stop to outputs off timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| No. see<br>Fig. 3-6<br>1 t <sub>avwL</sub><br>2 t <sub>wHAX</sub><br>3 t <sub>sLwL</sub><br>4 t <sub>wHSH</sub><br>5 t <sub>wLwH</sub><br>6 t <sub>DVWH</sub><br>7 t <sub>wHDX</sub><br>8 f <sub>cLK</sub><br>9 t <sub>cLCH</sub>                         | SEL Stable to WR Low<br>SEL Stable after WR<br>CS Low to WR Low<br>CS High after WR H<br>WR Pulse Width<br>Data Valid to WR High                                                                                                              | (T <sub>A</sub> = 25°C, V <sub>cc</sub><br><b>typ</b> .<br>A High<br>igh<br>8<br>gh<br>High 10<br>50°                                      |      | 10 %,<br>-40<br>min.<br>5<br>10<br>5<br>20<br>5<br>20<br>5<br>20                           | C1 = 5<br>85°C<br>max.                    | 0 pF)                                     | OUT 1 or OUT2<br>WR<br>Fig. 5 Stop to outputs off timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |