19-5228; Rev 2; 1/11

EVALUATION KIT AVAILABLE

# **3V/5V Low-Power, Low-Noise, CMOS,** Rail-to-Rail I/O Op Amps

# **General Description**

## **Features**

- ♦ Low Input Voltage-Noise Density: 38nV/√Hz

- ◆ Low Input Current-Noise Density: 0.9fA/√Hz

- Ultra-Low 0.1pA Bias Current

- Low 36µA Quiescent Current

- ♦ 1µA Quiescent Current in Shutdown

- Wide 1.5MHz Bandwidth

- ♦ Single-Supply Operation V<sub>DD</sub> = 2.1V to 5.5V

- Available in Tiny 6-Pin SC70, 8-Pin SC70, and 10-Pin UTQFN Packages

- ♦ -40°C to +125°C Operating Temperature Range

# **\_Ordering Information**

| PART        | TEMP RANGE      | PIN-PACKAGE |

|-------------|-----------------|-------------|

| MAX9636AXT+ | -40°C to +125°C | 6 SC70      |

| MAX9637AXA+ | -40°C to +125°C | 8 SC70      |

| MAX9638AVB+ | -40°C to +125°C | 10 UTQFN    |

|             |                 |             |

+Denotes a lead(Pb)-free/RoHS-compliant package. T = Tape and reel.

The MAX9636/MAX9637/MAX9638 are single-supply, CMOS input op amps featuring wide bandwidth at low quiescent current, making them suitable for a broad range of battery-powered applications such as portable medical instruments, portable media players, and smoke detectors. A combination of extremely low input bias currents, low input current noise and low input voltage noise allows interface to high-impedance sources such as photodiode and piezoelectric sensors. These devices are also ideal for general-purpose signal processing functions such as filtering and amplification in a broad range of portable, battery-powered applications.

The ICs feature a maximized ratio of gain bandwidth (GBW) to supply current. The devices operate from a single 2.1V to 5.5V supply at a typical quiescent supply current of 36 $\mu$ A. For additional power conservation, the MAX9636 and MAX9638 offer a low-power shutdown mode that reduces supply current to 1 $\mu$ A and places the amplifiers' outputs into a high-impedance state.

The ICs are specified over the automotive operating temperature range (-40°C to +125°C). The single is offered in a space-saving, 6-pin SC70 package, while the dual is offered in tiny, 8-pin SC70 and 10-pin UTQFN packages.

## Applications

- Portable Medical Instruments Piezoelectric Transducer Amplifiers Smoke Detectors Battery-Powered Devices

- General-Purpose Signal Conditioning

- Notebooks

- Portable Media Players

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

## **ABSOLUTE MAXIMUM RATINGS**

| $\begin{array}{c} V_{DD}, \ \overline{SHDN} \ \text{to} \ V_{SS} \ \dots \ 0.3V \ \text{to} \ +6V \\ \text{IN+, IN-, OUT} \ \dots \ GND \ -0.3V \ \text{to} \ V_{DD} \ + \ 0.3V \\ \text{Continuous Input Current (any pins)} \ \dots \ \pm 20\text{mA} \\ \text{Output Short Circuit to} \ V_{DD} \ \text{or} \ V_{SS} \ Duration \ \dots \ 5s \\ \text{Thermal Limits (Note 1)} \\ \text{Multiple Layer PCB} \\ \text{Continuous Power Dissipation } (T_{A} \ = \ +70^{\circ}\text{C}) \\ \ 6\text{-Pin SC70 (derate 3.1\text{mW}/^{\circ}\text{C above } \ +70^{\circ}\text{C}) \ \dots \ 245\text{mW} \\ \ \theta_{JA} \ \dots \ 326.5^{\circ}\text{C/W} \\ \ \theta_{JC} \ \dots \ 115^{\circ}\text{C}\text{W} \end{array}$ | 8-Pin SC70 (derate 3.1mW/°C above +70°C)245mW    θJA |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| θJC115°C/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Soldering Temperature (reflow)+260°C                 |

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a fourlayer board. For detailed information on package thermal considerations, refer to <u>www.maxim-ic.com/thermal-tutorial</u>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = 3.3V, V_{SS} = 0V, V_{IN+} = V_{IN-} = V_{CM} = V_{DD}/2, R_L = 10k\Omega$  to  $V_{DD}/2, \overline{SHDN} = V_{DD}, T_A = -40^{\circ}C$  to  $+125^{\circ}C$ . Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 2)

| PARAMETER                    | SYMBOL                              | CONDITIONS                                       |                                                  | MIN          | TYP   | MAX          | UNITS |

|------------------------------|-------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------|-------|--------------|-------|

| DC CHARACTERISTICS           |                                     |                                                  |                                                  |              |       |              | •     |

| Input Voltage Range          | V <sub>IN+</sub> , V <sub>IN-</sub> | Guaranteed by CMRR                               |                                                  | Vss -<br>0.1 |       | VDD +<br>0.1 | V     |

|                              | Maa                                 | T <sub>A</sub> = +25°C                           |                                                  |              | 0.01  | 2.2          |       |

| Input Offset Voltage         | Vos                                 | $T_A = -40^{\circ}C \text{ to } + 10^{\circ}C$   | 125°C                                            |              |       | 3.5          | mV    |

| Input Offset Voltage Drift   | TCVos                               | MAX9636 only                                     |                                                  |              |       | 7            | µV/°C |

| (Note 3)                     | TCVOS                               | MAX9637, MAX9                                    | 9638 only                                        |              |       | 10           | μν/ Ο |

|                              |                                     | $T_A = +25^{\circ}C$                             |                                                  |              | ±0.1  | ±0.8         |       |

| Input Bias Current (Note 3)  | ΙB                                  | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$    |                                                  |              |       | ±50          | рА    |

|                              |                                     | $T_{A} = -40^{\circ}C \text{ to } +125^{\circ}C$ |                                                  |              |       | ±800         |       |

|                              | CMRR                                | Vss < Vcm <<br>(V <sub>DD</sub> - 1.4V)          | $T_{A} = +25^{\circ}C$                           | 72           | 86    |              |       |

| Common-Mode Rejection Ratio  |                                     |                                                  | $T_{A} = -40^{\circ}C \text{ to } +125^{\circ}C$ | 68           |       |              | dB    |

|                              |                                     | $(V_{SS} - 0.1V) < V_{CM} < (V_{DD} + 0.1V)$     |                                                  | 58           | 77    |              |       |

| Open-Loop Gain               | A.01                                | Vout = 0.25V from rails                          |                                                  | 104          | 124   |              | dB    |

|                              | AOL                                 | $V_{OUT} = 0.4V$ from rails, $R_L = 600\Omega$   |                                                  | 100          | 120   |              |       |

| Output Short-Circuit Current | 100                                 | Short to VDD                                     |                                                  |              | 55    |              | mA    |

| Output Short-Circuit Current | Isc                                 | Short to V <sub>SS</sub>                         |                                                  |              | 40    |              | IIIA  |

| Output Voltage Low           | Vol                                 | Vour                                             | $R_L = 10k\Omega$                                |              | 0.014 | 0.03         | V     |

| Output voltage Low           | VOL                                 | Vout                                             | $R_{L} = 600\Omega$                              |              | 0.044 | 0.08         | v     |

|                              |                                     |                                                  | $R_L = 10k\Omega$                                |              | 0.019 | 0.04         | V     |

| Output Voltage High          | Voh                                 | $V_{DD} - V_{OUT} \qquad R_{L} = 600\Omega$      |                                                  |              | 0.057 | 0.1          | V     |

| Output Leakage in Shutdown   |                                     | SHDN = $V_{SS}$ , $V_{C}$<br>MAX9638 only)       | $DUT = 0V$ to $V_{DD}$ (MAX9636,                 |              | 0.01  | 1            | μA    |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 3.3V, V_{SS} = 0V, V_{IN+} = V_{IN-} = V_{CM} = V_{DD}/2, R_L = 10k\Omega$  to  $V_{DD}/2, \overline{SHDN} = V_{DD}, T_A = -40^{\circ}C$  to  $+125^{\circ}C$ . Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 2)

| PARAMETER                               | SYMBOL   | CONI                                                       | CONDITIONS                                     |     | TYP  | MAX | UNITS  |  |

|-----------------------------------------|----------|------------------------------------------------------------|------------------------------------------------|-----|------|-----|--------|--|

| AC CHARACTERISTICS                      |          |                                                            |                                                |     |      |     |        |  |

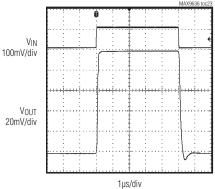

| Input Voltage Noise Density             | eN       | f = 1kHz                                                   |                                                |     | 38   |     | nV/√Hz |  |

| Input Voltage Noise                     |          | $0.1Hz \le f \le 10Hz$                                     |                                                |     | 5    |     | µVp-p  |  |

| Input Current Noise Density             | IN       | f = 1 kHz                                                  |                                                |     | 0.9  |     | fA/√Hz |  |

| Input Capacitance                       | CIN      |                                                            |                                                |     | 2    |     | pF     |  |

| Gain Bandwidth                          | GBW      |                                                            |                                                |     | 1.5  |     | MHz    |  |

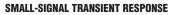

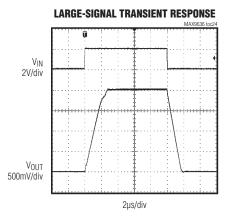

| Slew Rate                               | SR       |                                                            |                                                |     | 0.9  |     | V/µs   |  |

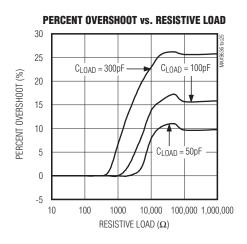

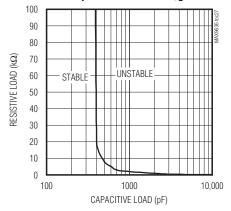

| Capacitive Loading                      | CLOAD    | No sustained oscillat                                      | tions                                          |     | 300  |     | рF     |  |

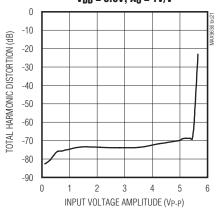

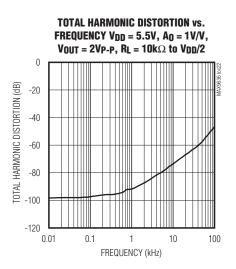

|                                         |          | $f = 10 \text{kHz}, V_0 = 2 \text{V}_P$                    | -P, A <sub>V</sub> = 1V/V                      |     | -68  |     |        |  |

| Distortion                              | THD      | f = 10kHz, VO = 2VP<br>V <sub>DD</sub> = 5.5V              | -P, Av = 1V/V,                                 |     | -74  |     | dB     |  |

| Settling Time                           |          | To 0.1%, V <sub>OUT</sub> = 2V step, A <sub>V</sub> = 1V/V |                                                |     | 11.5 |     | μs     |  |

|                                         |          | f = 1kHz (MAX9637, MAX9638)                                |                                                |     | 100  |     |        |  |

| Crosstalk                               |          | f = 10kHz (MAX9637, MAX9638)                               |                                                | 80  |      |     | - dB   |  |

| POWER-SUPPLY CHARACTER                  | RISTICS  |                                                            | · · · · ·                                      |     |      |     |        |  |

| Power-Supply Range                      | VDD      | Guaranteed by PSRR                                         |                                                | 2.1 |      | 5.5 | V      |  |

|                                         |          | $V_{IN+} = V_{IN-} = V_{SS},$                              | $T_A = +25^{\circ}C$                           | 72  | 100  |     |        |  |

| Power-Supply Rejection Ratio            | PSRR     | $V_{DD} - V_{SS} = 2.1V$<br>to 5.5V                        | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$ | 69  |      |     | dB     |  |

|                                         | 1        | Dan ana lifian                                             | $T_A = +25^{\circ}C$                           |     | 36   | 55  |        |  |

| Quiescent Current                       | IDD      | Per amplifier                                              | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$ |     |      | 60  | μA     |  |

| Shutdown Supply Current                 | IDD_SHDN | VSHDN ≤ VIL (MAX96                                         | 36, MAX9638 only)                              |     |      | 1   | μA     |  |

| Shutdown Input                          | VIL      | Over the power-supp<br>MAX9638 only)                       | bly range (MAX9636,                            |     |      | 0.5 | V      |  |

| Shutdown Input                          | VIH      | Over the power-supply range (MAX9636, MAX9638 only)        |                                                | 1.4 |      |     | V      |  |

| Shutdown Input Bias Current<br>(Note 3) | ISHDN    | MAX9636, MAX9638 only                                      |                                                |     | 1    | 100 | nA     |  |

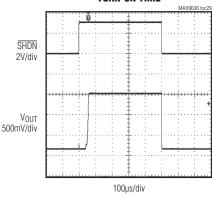

| Turn-On Time                            | ton      | V <sub>SHDN</sub> = 0V to 3V (MAX9636, MAX9638<br>only)    |                                                |     | 60   |     | μs     |  |

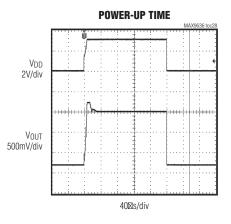

| Power-Up Time                           | tup      | $V_{DD} = 0V \text{ to } 3.3V$                             |                                                |     | 18   |     | μs     |  |

**Note 2:** All devices are 100% production tested at  $T_A = +25^{\circ}C$ . Temperature limits are guaranteed by design. **Note 3:** Parameter is guaranteed by design.

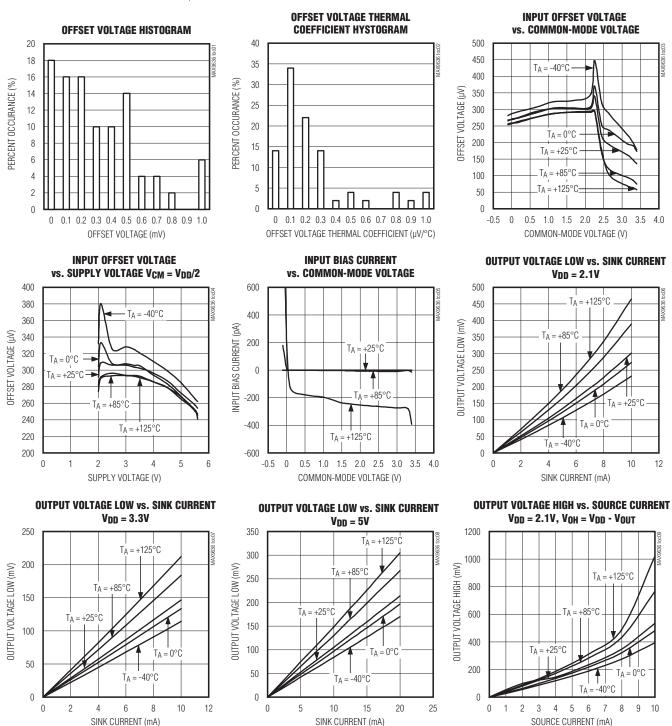

## **Typical Operating Characteristics**

///XI//

$(V_{DD} = 3.3V, V_{SS} = 0V, V_{IN+} = V_{IN-} = V_{CM} = V_{DD}/2, R_L = 10k\Omega$  to  $V_{DD}/2$ ,  $\overline{SHDN} = V_{DD}$ ,  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ . Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

MAX9636/MAX9637/MAX9638

$(V_{DD} = 3.3V, V_{SS} = 0V, V_{IN+} = V_{IN-} = V_{CM} = V_{DD}/2, R_L = 10k\Omega$  to  $V_{DD}/2, \overline{SHDN} = V_{DD}, T_A = -40^{\circ}C$  to  $+125^{\circ}C$ . Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

MAX9636/MAX9637/MAX9638

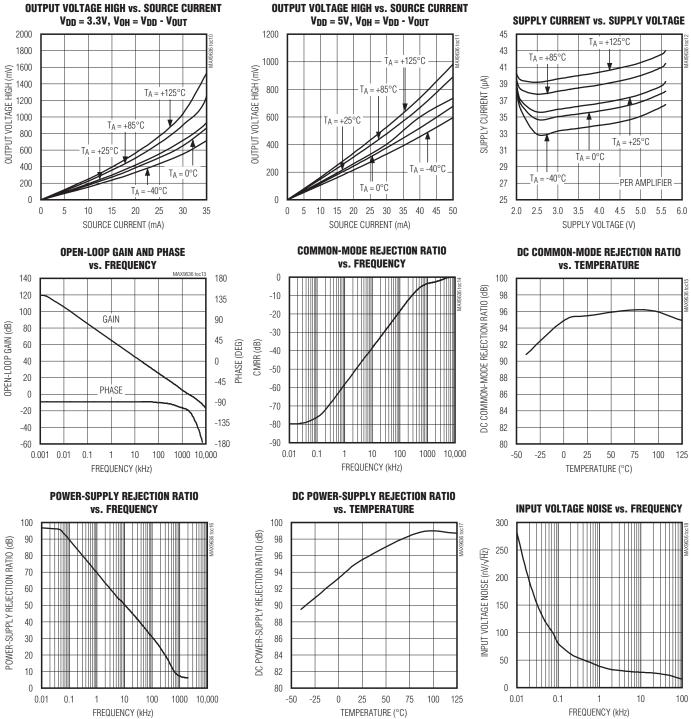

# **Typical Operating Characteristics (continued)**

$(V_{DD} = 3.3V, V_{SS} = 0V, V_{IN+} = V_{IN-} = V_{CM} = V_{DD}/2, R_L = 10k\Omega$  to  $V_{DD}/2, \overline{SHDN} = V_{DD}, T_A = -40^{\circ}C$  to  $+125^{\circ}C$ . Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

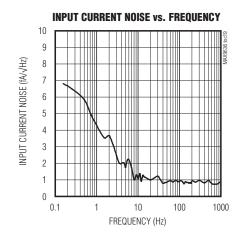

# **Typical Operating Characteristics (continued)**

$(V_{DD} = 3.3V, V_{SS} = 0V, V_{IN+} = V_{IN-} = V_{CM} = V_{DD}/2, R_L = 10k\Omega$  to  $V_{DD}/2$ ,  $\overline{SHDN} = V_{DD}$ ,  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ . Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

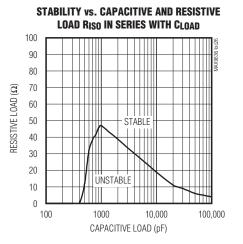

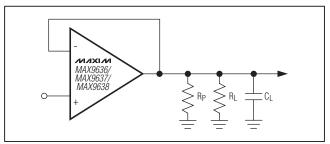

STABILITY vs. CAPACITIVE AND RESISTIVE LOAD RP IN PARALLEL WITH CL

**TURN-ON TIME**

**Pin Configurations** TOP VIEW IN+ 1 6 V<sub>DD</sub> <u>\_\_\_\_\_\_</u> OUTA 1 8 V<sub>DD</sub> MAX9636 7 OUTB INA- 2 5 SHDN V<sub>SS</sub> 2 INA+ 3 6 INB-MAX9637 5 INB+ IN- 3 4 OUT V<sub>SS</sub> 4 **SC70 SC70** SHDNB SHDNA 7 6 OUTA 5 Vss 8 *и*ихі*и*і 9 4 INA+ INA-MAX9638 OUTB 10 3 INB-2 1 INB+ VDD UTQFN

## **Pin Description**

|                     | PIN                 |                       |       |                                                                 |

|---------------------|---------------------|-----------------------|-------|-----------------------------------------------------------------|

| MAX9636<br>(6 SC70) | MAX9637<br>(8 SC70) | MAX9638<br>(10 UTQFN) | NAME  | FUNCTION                                                        |

| 1                   |                     | —                     | IN+   | Positive Input                                                  |

| _                   | 3                   | 4                     | INA+  | Positive Input A                                                |

| _                   | 5                   | 2                     | INB+  | Positive Input B                                                |

| 2                   | 4                   | 5                     | Vss   | Negative Power Supply. Bypass with a 0.1µF capacitor to ground. |

| 3                   | —                   | —                     | IN-   | Negative Input                                                  |

| _                   | 2                   | 9                     | INA-  | Negative Input A                                                |

| _                   | 6                   | 3                     | INB-  | Negative Input B                                                |

| 4                   |                     | —                     | OUT   | Output                                                          |

| _                   | 1                   | 8                     | OUTA  | Output A                                                        |

| _                   | 7                   | 10                    | OUTB  | Output B                                                        |

| _                   |                     | 6                     | SHDNA | Active-Low Shutdown A                                           |

| _                   | —                   | 7                     | SHDNB | Active-Low Shutdown B                                           |

| 5                   | —                   | —                     | SHDN  | Active-Low Shutdown                                             |

| 6                   | 8                   | 1                     | VDD   | Positive Power Supply. Bypass with a 0.1µF capacitor to ground. |

# MAX9636/MAX9637/MAX9638

# **3V/5V Low-Power, Low-Noise, CMOS,** Rail-to-Rail I/O Op Amps

## **Detailed Description**

The MAX9636/MAX9637/MAX9638 are single-supply, CMOS input op amps. They feature wide bandwidth at low quiescent current, making them suitable for a broad range of battery-powered applications such as portable medical instruments, portable media players, and smoke detectors. A combination of extremely low input bias currents, low input current noise, and low input voltage noise allows interface to high-impedance sources such as photodiode and piezoelectric sensors. These devices are also ideal for general-purpose signal processing functions such as filtering and amplification in a broad range of portable, battery-powered applications.

The devices' operational common-mode range extends 0.1V beyond the supply rails, allowing for a wide variety of single-supply applications.

The ICs also feature low quiescent current and a shutdown mode that greatly reduces quiescent current while the device is not operational. This makes the device suitable for portable applications where power consumption must be minimized.

#### **Rail-to-Rail Input Stage**

The operational amplifiers have parallel-connected nand p-channel differential input stages that combine to accept a common-mode range extending 100mV beyond the supply rails. The n-channel stage is active for common-mode input voltages typically greater than (V<sub>DD</sub> - 1.2V), and the p-channel stage is active for common-mode input voltages typically less than (V<sub>DD</sub> - 1.4V). A small transition region exists, typically V<sub>DD</sub> - 1.4 to V<sub>DD</sub> - 1.2V, during which both pairs are on.

#### **Rail-to-Rail Output Stage**

The maximum output voltage swing is load dependent. However, it is guaranteed to be within 100mV of the positive rail even with 3mA of load current. To maximize the output current sourcing capability, these parts do not come with built-in short-circuit protection. If loads heavier than  $600\Omega$  must be driven, then ensure that the maximum allowable power dissipation is not exceeded (see the *Absolute Maximum Ratings* section).

#### Low Input Bias Current

This op-amp family features ultra-low 0.1pA (typ) input bias current and guaranteed maximum current of  $\pm$ 50pA over -40°C to +85°C when the input common-mode voltage is at midrail. For the -40°C to +85°C temperature range, the variation in the input bias current is small with changes in the input voltage due to very high input impedance (in the order of 100G $\Omega$ ).

#### **Power-Up Time**

The ICs typically require a power-up time of 18µs. Supply settling time depends on the supply voltage, the value of the bypass capacitor, the output impedance of the incoming supply, and any lead resistance or inductance between components. Op amp settling time depends primarily on the output voltage and is slew-rate limited. The output settles in approximately 11.5µs for  $V_{DD} = 3V$  and  $V_{OUT} = V_{DD}/2V$  (see the Power-Up Time graph in the *Typical Operating Characteristics* section).

#### **Driving Capacitive Loads**

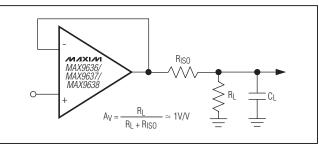

The ICs have a high tolerance for capacitive loads. In unity-gain configuration, the op amps can typically drive up to 300pF pure capacitive load. Increasing the gain enhances the amplifier's ability to drive greater capacitive loads. In unity-gain configurations, capacitive load drive can be improved by inserting a small (5 $\Omega$  to  $30\Omega$ ) isolation resistor, R<sub>ISO</sub>, in series with the output, as shown in Figure 1. This significantly reduces ringing while maintaining DC performance for purely capacitive loads. However, if the load also has a resistive component then a voltage-divider is created, introducing a direct current (DC) error at the output. The error introduced is proportional to the ratio RISO/RL, which is usually negligible in most cases. Applications that cannot tolerate this slight DC error can use an alternative approach of providing stability by placing a suitable resistance in parallel with the capacitive load as shown in Figure 2 (see the Typical Operating Characteristics section for graphs of the stable operating region for various capacitive loads vs. resistive loads). While this approach of adding a resistor parallel to the load does not introduce DC error, it nevertheless reduces the output swing proportionally.

Figure 1. Using a Series Resistor to Isolate the Capacitive Load from the Op Amp

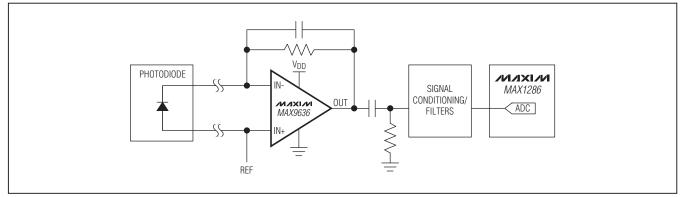

## \_\_\_\_High-Impedance Sensor Front-Ends

The ICs interface to both current-output sensors, such as photodiodes (Figure 3), and high-impedance voltage sources, such as piezoelectric sensors. For currentoutput sensors, a transimpedance amplifier is the most noise-efficient method for converting the input signal to a voltage. High-value feedback resistors are commonly chosen to create large gains, while feedback capacitors help stabilize the amplifier by cancelling any poles introduced in the feedback function by the highly capacitive sensor or cabling. A combination of low-current noise and low-voltage noise is important for these applications. Take care to calibrate out photodiode dark current if DC accuracy is important. The high bandwidth and slew rate also allows AC signal processing in certain medical photodiode sensor applications such as pulse oximetry.

For voltage-output sensors, a noninverting amplifier is typically used to buffer and/or apply a small gain to the input voltage signal. Due to the extremely high impedance of the sensor output, a low input bias current with minimal temperature variation is very important for these applications.

Figure 2. Using a Parallel Resistor to Degenerate the Effect of the Capacitive Load and Increase Stability

Figure 3. The MAX9636 in a Sensor Preamp Configuration

For best performance, follow standard high-impedance layout techniques, which include the following:

- Using shielding techniques to guard against parasitic leakage paths. For example, put a trace connected to the noninverting input around the inverting input.

- Minimizing the amount of stray capacitance connected to op amp's inputs to improve stability. To achieve this, minimize trace lengths and resistor leads by placing external components as close as possible to the package.

- Use separate analog and digital power supplies.

## **Applications Information**

#### **Shutdown Operation**

The MAX9636/MAX9638 feature an active-low shutdown mode that sends the inputs and output into high impedance and substantially lowers the guiescent current.

#### Active-Low Input

The shutdown active-low (VIL) and high (VIH) threshold voltages are designed for ease of integration with digital controls, such as microcontroller outputs. These thresholds are independent of supply, eliminating the need for external pulldown circuitry.

#### **Output During Shutdown**

The MAX9636/MAX9638 output is in a high-impedance state while SHDN is low. The device structure limits the output leakage current in this state to 0.01µA when the output is between OV to VDD.

The MAX9636/MAX9637/MAX9638 are low-power amplifiers ideal for driving high to medium-resolution ADCs. Figure 3 shows how the MAX9636 is connected to a photodiode, with the amplifier output connected to additional signal conditioning/filtering, or directly to the ADC. The MAX1286-MAX1289 family of low-power, 12-bit ADCs are ideal for connecting to the MAX9636/MAX9637/MAX9638.

The MAX1286-MAX1289 ADCs offer sample rates up to 150ksps, with 3V and 5V supplies, as well as 1- and 2-channel options. These ADCs dissipate just 15µA when sampling at 10ksps and 0.2µA in shutdown. Offered in tiny 8-pin SOT23 and 3mm x 3mm TDFN packages, the MAX1286-MAX1289 ADCs are an ideal fit to pair with the MAX9636/MAX9637/MAX9638 amplifiers in portable applications.

Similarly, the MAX1086-MAX1089 is a family of 10-bit pin-compatible low-power ADCs with the same 3V/5V, 1- and 2-channel options. Table 1 details the amplifier and ADC pairings for single- and dual-channel applications.

MAX1086

**Chip Information**

MAX1286

**ADC** Driver

PROCESS: BICMOS

MAX1287

| CHANNELS | AMPLIFIER |            |            | ADC        |            |  |  |  |

|----------|-----------|------------|------------|------------|------------|--|--|--|

| CHANNELS | AWFLIFIEN | 3V, 10 BIT | 3V, 12 BIT | 5V, 10 BIT | 5V, 12 BIT |  |  |  |

| 1        | MAX9636   | MAX1089    | MAX1289    | MAX1088    | MAX1288    |  |  |  |

| 2        | MAX9637   | MAX1087    | MAX1287    | MAX1086    | MAX1286    |  |  |  |

MAX1087

### Table 1 Recommended Amplifiers/ADCs

MAX9638

2

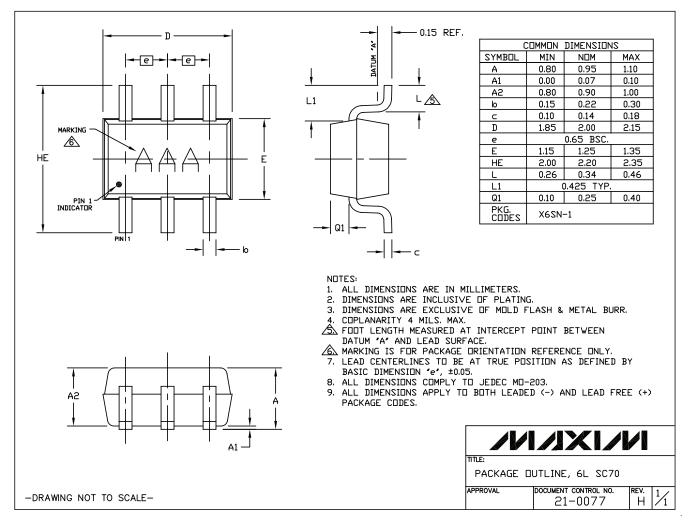

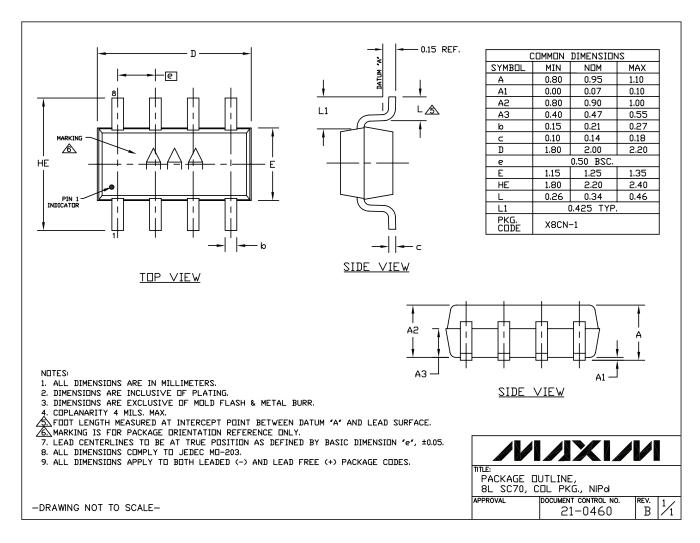

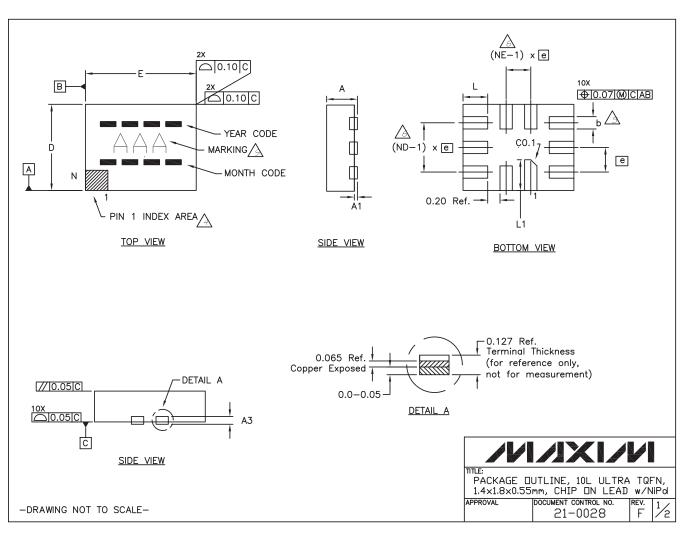

# Package Information

| PACKAGE TYPE | PACKAGE CODE | OUTLINE NO.    | LAND PATTERN NO. |

|--------------|--------------|----------------|------------------|

| 6 SC70       | X6SN+1       | <u>21-0077</u> | <u>90-0189</u>   |

| 8 SC70       | X8CN+1       | <u>21-0460</u> | <u>90-0348</u>   |

| 10 UTQFN     | V101A1CN+1   | <u>21-0028</u> | <u>90-0287</u>   |

# Package Information (continued)

# Package Information (continued)

# Package Information (continued)

| NOTES:<br>1. DIMENSIONING & TOLERANCING CONFORM TO                                                                                  | 2 ASME V14 5M-1994                                          | PKG                         | 10L               | 1.4×1              | 1.8           | N               |

|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------------|-------------------|--------------------|---------------|-----------------|

| 2. ALL DIMENSIONS ARE IN MILLIMETERS. ANG                                                                                           |                                                             | REF.                        | MIN.              | NDM.               | MAX.          | T<br>F          |

| 3. N IS THE TOTAL NUMBER OF TERMINALS.                                                                                              |                                                             |                             |                   |                    | 0.55          |                 |

| 4. THE TERMINAL #1 IDENTIFIER AND TERMINAL                                                                                          | A                                                           | 0.45<br>0                   | 0.50              | 0.05               |               |                 |

| TO JESD 95-1 SPP-012. DETAILS OF TE<br>BUT MUST BE LOCATED WITHIN THE ZONE                                                          | A3                                                          | , v                         | 0.127 RE          |                    |               |                 |

| MAY BE EITHER A MOLD OR MARKED FEATU                                                                                                | b                                                           | 0.15                        | 0.20              | 0.25               |               |                 |

| 5. DIMENSION & APPLIES TO METALLIZED TERM                                                                                           |                                                             | D                           | 1.30              | 1.40               | 1.50          |                 |

| 0.15mm AND 0.25mm FROM TERMINAL TIP                                                                                                 |                                                             | E                           | 1.70              | 1.40               | 1.90          |                 |

| 6. ND AND NE REFER TO THE NUMBER OF TE<br>RESPECTIVELY.                                                                             | RMINALS ON EACH D AND E SIDE                                |                             | 1.70              | 0.40 BS(           |               |                 |

| 7. REFER TO JEDEC MO-248 AND MO-236.                                                                                                |                                                             | e                           | 0.05              |                    | I             |                 |

| 8. WARPAGE SHALL NOT EXCEED 0.05mm.                                                                                                 | L                                                           | 0.35                        | 0.40              | 0.45               |               |                 |

| MARKING IS PACKAGE ORIENTATION PURPOS                                                                                               |                                                             | L1                          | 0.45              | 0.50               | 0.55          |                 |

| 10. DIMENSIONS APPLY TO PEFREE (+) PKG CO<br>11. COPLANARITY APPLIES TO THE EXPOSED PA                                              |                                                             | N                           |                   | 10                 |               |                 |

| COPLANARITY SHALL NOT EXCEED 0.05mm.                                                                                                | D AS WELE AS THE TERMINALS.                                 | ND                          |                   | 3                  |               |                 |

|                                                                                                                                     |                                                             | NE                          |                   | 2                  |               |                 |

|                                                                                                                                     |                                                             | PKG.<br>CDDE                | V101A             | 1CN-1; \           | /101A1C       | v-2             |

| TABLE 1    Translation Table for Calendar Year Code    2008    2009    2010    2011    2012    2013    2014    2015    2016    2017 | TABLE 2    Translation Table for Calendar Month Code    Jan | //                          |                   | IX                 |               |                 |

| Legend: 🔲 Marked with bar 🗔 Blank sp                                                                                                | ace - no bar required fi<br>1<br>1                          | .e:<br>PACKAGE<br>4×1.8×0.5 | OUTLIN<br>i5mm, C | IE, 10L<br>CHIP ON | ULTRA<br>LEAD | TQFN,<br>w∕NiPd |

| -DRAWING NOT TO SCALE-                                                                                                              | AP                                                          | PROVAL                      |                   | INT CONTRO         |               | F 2/2           |

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                                                                                                                                                             | PAGES<br>CHANGED |

|--------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 0                  | 6/10             | Initial release                                                                                                                                                                                                                                                                         | —                |

| 1                  | 9/10             | Removed future product references, updated Input Offset Voltage Drift conditions, updated Output Short-Circuit Current typ value, updated Input Current Noise Density typ value, and added Crosstalk parameter to the <i>Electrical Characteristics</i> table, modified TOCs 12, 14, 19 | 1, 2, 3, 5, 6    |

| 2                  | 1/11             | Corrected the MAX9637 pin configuration                                                                                                                                                                                                                                                 | 8                |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

\_\_\_\_ Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2011 Maxim Integrated Products

Maxim is a registered trademark of Maxim Integrated Products, Inc.