Features

# CMOS 8-Bit DAC with Output Amplifier

## **General Description**

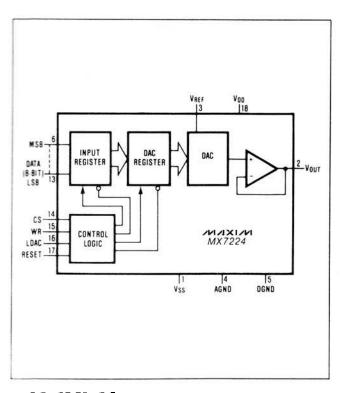

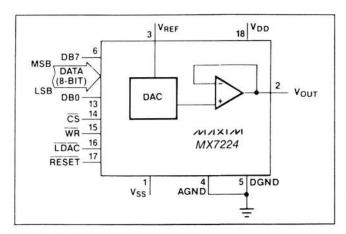

The MX7224 is a precision voltage-output CMOS digital-to-analog converter (DAC) which includes an output amplifier on chip. Only an external reference source is required for operation and the fully specified accuracy is achieved with no external trims.

Double buffered interface logic is included to allow simultaneous updating in systems which have several DAC channels in operation. Control is provided by CS, WR, and LDAC (Load DAC) inputs. A RESET input is provided which acts as a zero override. All logic inputs are compatible with TTL and 5V CMOS logic levels.

Specified Performance is guaranteed for reference inputs ranging from +2V to +12.5V when using dual supplies. With a +10V reference the performance is also specified for single supply operation. The DAC output can drive +10V into a 2kΩ load.

## Applications

Automatic Calibration Motion Control Digital Attenuators **Function Generators**

#### **Voltage Output**

- Complete DAC with Output Amplifier

- Single or Dual Supply Operation

- 1 LSB Unadjusted Error

- **Double Buffered Logic Inputs**

## **Ordering Information**

| PART       | TEMP. RANGE     | PACKAGE*    | ERROR  |

|------------|-----------------|-------------|--------|

| MX7224KN   | 0°C to +70°C    | Plastic DIP | ±2 LSB |

| MX7224LN   | 0°C to +70°C    | Plastic DIP | ±1 LSB |

| MX7224K/D  | 0°C to +70°C    | Dice        | ±2 LSB |

| MX7224KCWN | 0°C to +70°C    | Wide S.O.   | ±2 LSB |

| MX7224LCWN | 0°C to +70°C    | Wide S.O.   | ±1 LSB |

| MX7224BQ   | -25°C to +85°C  | CERDIP**    | ±2 LSB |

| MX7224CQ   | -25°C to +85°C  | CERDIP**    | ±1 LSB |

| MX7224TD   | -55°C to +125°C | Ceramic     | ±2 LSB |

| MX7224UD   | -55°C to +125°C | Ceramic     | ±1 LSB |

| MX7224TQ   | -55°C to +125°C | CERDIP**    | ±2 LSB |

| MX7224UQ   | -55°C to +125°C | CERDIP**    | ±1 LSB |

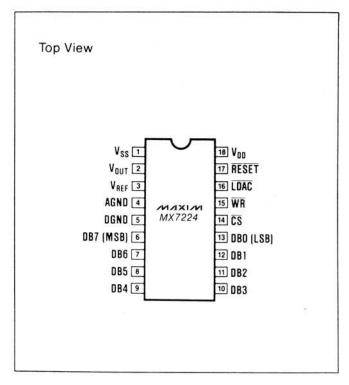

- All devices 18 lead packages

- Maxim reserves the right to ship Ceramic packages in lieu of CERDIP packages.

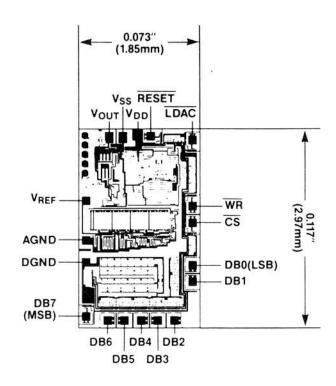

#### Functional Diagram

# Pin Configuration

### ABSOLUTE MAXIMUM RATINGS

| V <sub>DD</sub> to AGND0.3V, +17V                  | Power Dissipation (Any Package) to +75°C 450mW |

|----------------------------------------------------|------------------------------------------------|

| V <sub>DD</sub> to DGND0.3V, +17V                  | Derating above +75°C                           |

| AGND to DGND0.3V, V <sub>DD</sub>                  | Operating Temperature                          |

| V <sub>SS</sub> to DGND7V, V <sub>DD</sub> + 0.3V  | MX7224K/L 0°C to +70°C                         |

| V <sub>DD</sub> to V <sub>SS</sub> 0.3V, +24V      | MX7224A/B25°C to +85°C                         |

| Digital Input Voltage to DGND0.3V, V <sub>DD</sub> | MX7224T/U55°C to +125°C                        |

| V <sub>REF</sub> to AGND0.3V, V <sub>DD</sub>      | Storage Temperature65°C to +160°C              |

| V <sub>OUT</sub> to DGND                           | Lead Temperature (Soldering 10 secs) +300°C    |

The output may be shorted to AGND provided that the power dissipation of the package is not exceeded. Typical short circuit current to AGND is 25mA.

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum ratings conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS—MX7224, Dual Supply Operation

$(V_{DD}$  = +11.4V to +16.5V,  $V_{SS}$  = -5V ±10%, AGND = DGND = 0V,  $V_{REF}$  = +2V to  $(V_{DD}$  - 4V) (Note 1), Over Temperature unless otherwise noted.)

| PARAMETER                                               | SYMBOL           | TEST CON                                    | DITIONS                    | MIN | TYP        | MAX                 | UNITS   |

|---------------------------------------------------------|------------------|---------------------------------------------|----------------------------|-----|------------|---------------------|---------|

| STATIC PERFORMANCE                                      |                  |                                             |                            |     |            |                     |         |

| Resolution                                              |                  |                                             |                            | 8   |            |                     | Bits    |

| Total Unadjusted Error                                  |                  | $V_{REF} = +10V$<br>$V_{DD} = +15V \pm 5\%$ | MX7224L/C/U<br>MX7224K/B/T |     |            | ±1<br>±2            | LSB     |

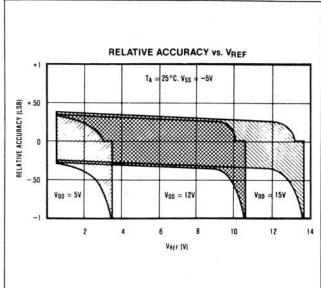

| Relative Accuracy                                       |                  | MX7224L/C/U<br>MX7224K/B/T                  |                            |     |            | ±½<br>±1            | LSB     |

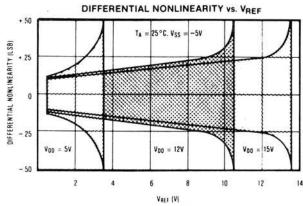

| Differential Nonlinearity                               |                  | Guaranteed Mono                             | tonic                      |     |            | ±1                  | LSB     |

| Full Scale Error                                        |                  | MX7224L/C/U<br>MX7224K/B/T                  |                            |     |            | ±1<br>±1½           | LSB     |

| Full Scale Temperature<br>Coefficient                   |                  | V <sub>REF</sub> = +10V                     |                            |     | ±5         |                     | ppm/° C |

| Zero Code Error                                         |                  | MX7224L/C/U<br>MX7224K/B/T                  |                            |     |            | ±20<br>±30          | mV      |

| Zero Code Temperature<br>Coefficient                    |                  | MX7224L/C/U<br>MX7224K/B/T                  |                            |     | ±30<br>±50 |                     | μV/°C   |

| REFERENCE INPUT                                         | 1                |                                             |                            |     |            |                     |         |

| Reference Input Voltage Range                           | V <sub>REF</sub> |                                             |                            | 2   |            | V <sub>DD</sub> - 4 | V       |

| Reference Input Resistance                              | V <sub>REF</sub> |                                             |                            | 8   |            |                     | kΩ      |

| Reference Input Capacitance<br>(Code Dependent, Note 2) | C <sub>REF</sub> | DAC at full scale of                        | code.                      |     |            | 100                 | pF      |

| DIGITAL INPUTS                                          |                  |                                             |                            |     |            |                     | 1       |

| Digital Input High Voltage                              | V <sub>INH</sub> |                                             |                            | 2.4 |            |                     | V       |

| Digital Input Low Voltage                               | V <sub>INL</sub> |                                             |                            |     |            | 0.8                 | V       |

| Digital Input Leakage Current                           |                  | V <sub>IN</sub> = 0V or V <sub>DD</sub>     |                            |     |            | ±1                  | μА      |

| Digital Input Capacitance<br>(Note 2)                   |                  |                                             |                            |     |            | 8                   | pF      |

# ELECTRICAL CHARACTERISTICS-MX7224, Dual Supply Operation (Continued)

$(V_{DD}$  = +11.4V to +16.5V,  $V_{SS}$  = -5V  $\pm$ 10%, AGND = DGND = 0V,  $V_{REF}$  = +2V to  $(V_{DD}$  - 4V) (Note 1), Over Temperature unless otherwise noted.)

| PARAMETER                             | SYMBOL          | TEST COND                                               | TIONS                                 | MIN        | TYP | MAX    | UNITS |

|---------------------------------------|-----------------|---------------------------------------------------------|---------------------------------------|------------|-----|--------|-------|

| DYNAMIC PERFORMANCE                   | •               |                                                         |                                       |            |     |        | -     |

| Voltage Output Slew Rate (Note 2)     |                 |                                                         |                                       | 2.5        | 10  |        | V/μs  |

| Voltage Output Settling Time (Note 5) |                 | To 1/2 LSB, V <sub>REF</sub> =                          | +10V                                  |            | 2   | 5      | μs    |

| Digital Feedthrough (Notes 3, 4)      |                 | All 0's to all 1's code<br>V <sub>REF</sub> = 0V        | change,                               |            | 50  |        | nV-s  |

| Output Load Resistance                |                 | V <sub>OUT</sub> = +10V                                 |                                       | 2          |     |        | kΩ    |

| POWER SUPPLIES                        |                 |                                                         | · · · · · · · · · · · · · · · · · · · |            |     |        |       |

| V <sub>DD</sub> Range                 |                 | For Specified Perfor                                    | mance                                 | +11.4      |     | +16.5  | V     |

| V <sub>SS</sub> Range                 |                 | For Specified Perfor                                    | mance                                 | -4.5       |     | -5.5   | V     |

| Positive Supply Current               | I <sub>DD</sub> | Outputs unloaded, at V <sub>INL</sub> /V <sub>INH</sub> | T <sub>A</sub> = 25°C<br>Over Temp    |            |     | 4<br>6 | mA    |

| Negative Supply Current               | I <sub>SS</sub> | Outputs unloaded, at V <sub>INL</sub> /V <sub>INH</sub> | T <sub>A</sub> = 25°C<br>Over Temp    |            |     | 3<br>5 | mA    |

| SWITCHING CHARACTERISTICS             | (Note 2)        |                                                         | *                                     |            |     |        |       |

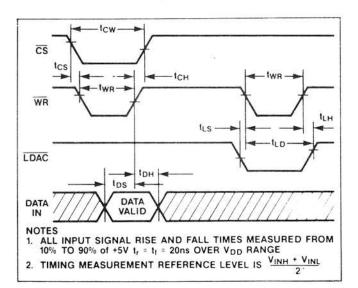

| Chip Select to Write Setup Time       | t <sub>CS</sub> |                                                         |                                       | 0          |     |        | ns    |

| Load DAC to Write Setup Time          | t <sub>LS</sub> |                                                         |                                       | 0          |     |        | ns    |

| Chip select to Write Hold Time        | t <sub>CH</sub> |                                                         |                                       | 0          |     |        | ns    |

| Load DAC to Write Setup Time          | t <sub>LH</sub> |                                                         | •                                     | 0          |     |        | ns    |

| Data Valid to Write Setup Time        | t <sub>DS</sub> | T <sub>A</sub> = 25°C<br>Over Temp                      |                                       | 90<br>100  |     |        | ns    |

| Data Valid to Write Hold Time         | t <sub>DH</sub> |                                                         |                                       | 10         |     |        | ns    |

| Write Pulse Width                     | t <sub>wa</sub> | T <sub>A</sub> = 25°C<br>Over Temp                      |                                       | 150<br>200 |     |        | ns    |

| Chip Select Pulse Width               | t <sub>CW</sub> | T <sub>A</sub> = 25°C<br>Over Temp                      |                                       | 150<br>200 |     |        | ns    |

| Reset Pulse Width                     | t <sub>RS</sub> | T <sub>A</sub> = 25°C<br>Over Temp                      |                                       | 150<br>200 |     |        | ns    |

| Load DAC (LDAC) Pulse Width           | t <sub>LD</sub> | T <sub>A</sub> = 25°C<br>Over Temp                      |                                       | 150<br>200 |     |        | ns    |

Note 1: Maximum possible reference voltage.

Note 2: Sample tested at 25°C to ensure compliance.

Note 3: Guaranteed, but not 100% production tested.

Note 4: Feedthrough is reduced by connecting the metal lid on the ceramic package (suffix D) to DGND.

Note 5: Positive or negative full scale change.

# **ELECTRICAL CHARACTERISTICS—MX7224, Single Supply Operation** $(V_{DD} = +15V \pm 5\%, V_{SS} = AGND = DGND = 0V, V_{REF} = +10V (Note 1), Over Temperature unless otherwise stated.)$

| PARAMETER                                               | SYMBOL           | CC                                             | ONS             | MIN                                | TYP        | MAX | UNITS  |      |

|---------------------------------------------------------|------------------|------------------------------------------------|-----------------|------------------------------------|------------|-----|--------|------|

| STATIC PERFORMANCE                                      |                  |                                                |                 |                                    |            |     |        |      |

| Resolution                                              |                  |                                                |                 |                                    | 8          |     |        | Bits |

| Total Unadjusted Error                                  |                  |                                                |                 |                                    |            |     | ±2     | LSB  |

| Differential Nonlinearity                               |                  | Guaranteed                                     | nic             |                                    |            | ±1  | LSB    |      |

| REFERENCE INPUT                                         |                  |                                                |                 |                                    |            |     |        |      |

| Reference Input Resistance                              | R <sub>REF</sub> |                                                |                 |                                    | 8          |     |        | kΩ   |

| Reference Input Capacitance<br>(Code Dependent)(Note 2) | C <sub>REF</sub> | DAC at full s                                  | scale co        | de                                 |            |     | 100    | pF   |

| DIGITAL INPUTS                                          |                  |                                                |                 |                                    |            |     |        |      |

| Digital Input High Voltage                              | V <sub>INH</sub> |                                                |                 |                                    | 2.4        |     |        | V    |

| Digital Input Low Voltage                               | V <sub>INL</sub> |                                                |                 |                                    |            |     | 0.8    | V    |

| Digital Input Leakage Current                           |                  | V <sub>IN</sub> = 0V to V                      | / <sub>DD</sub> |                                    |            |     | ±1     | μА   |

| Digital Input Capacitance (Note 2)                      |                  |                                                |                 |                                    |            |     | 8      | pF   |

| DYNAMIC PERFORMANCE                                     |                  |                                                |                 | •                                  |            |     |        |      |

| Voltage Output Slew Rate<br>(Note 2)                    |                  |                                                |                 |                                    | 2.5        | 10  |        | V/µs |

| Output Settling Time<br>(Note 2)                        |                  | To 1/2 LSB, Positive FS Chg<br>Negative FS Chg |                 |                                    |            | 2 3 | 5<br>8 | μs   |

| Digital Feedthrough (Notes 3, 4)                        |                  | All 0's to all<br>V <sub>REF</sub> = 0V        | change          |                                    | 50         |     | nV-s   |      |

| Output Load Resistance                                  |                  | V <sub>OUT</sub> = +10V                        |                 |                                    | 2          |     |        | kΩ   |

| POWER SUPPLIES                                          |                  |                                                |                 |                                    |            |     |        |      |

| V <sub>DD</sub> Range                                   |                  | For Specified                                  | Perfori         |                                    | +14.25     |     | +15.75 | V    |

| Positive Supply Current                                 | I <sub>DD</sub>  | Outputs unlo                                   | aded,           | T <sub>A</sub> = 25°C<br>Over Temp |            |     | 4<br>6 | mA   |

| SWITCHING CHARACTERISTICS                               | (Note 2)         |                                                |                 |                                    |            |     |        |      |

| Chip Select to Write Setup Time                         | t <sub>cs</sub>  |                                                |                 |                                    | 0          |     |        | ns   |

| Load DAC to Write Setup Time                            | t <sub>LS</sub>  |                                                |                 |                                    | 0          |     |        | ns   |

| Chip select to Write Hold Time                          | t <sub>CH</sub>  |                                                |                 |                                    | 0          |     |        | ns   |

| Load DAC to Write Setup Time                            | t <sub>LH</sub>  |                                                |                 |                                    | 0          |     |        | ns   |

| Data Valid to Write Setup Time                          | t <sub>DS</sub>  | T <sub>A</sub> = 25°C<br>Over Temp             |                 |                                    | 90<br>100  |     |        | ns   |

| Data Valid to Write Hold Time                           | t <sub>DH</sub>  |                                                |                 |                                    | 10         |     |        | ns   |

| Write Pulse Width                                       | t <sub>WR</sub>  | T <sub>A</sub> = 25°C<br>Over Temp             |                 | 150<br>200                         |            |     | ns     |      |

| Chip Select Pulse Width                                 | t <sub>CW</sub>  | T <sub>A</sub> = 25°C<br>Over Temp             |                 | 150<br>200                         |            |     | ns     |      |

| Reset Pulse Width                                       | t <sub>RS</sub>  | T <sub>A</sub> = 25°C<br>Over Temp             | 20              |                                    | 150<br>200 |     |        | ns   |

| Load DAC (LDAC) Pulse Width                             | t <sub>LD</sub>  | T <sub>A</sub> = 25°C<br>Over Temp             |                 |                                    | 150<br>200 |     |        | ns   |

Note 1: Maximum possible reference voltage.

Note 2: Sample tested at 25°C to ensure compliance. Note 3: Guaranteed, but not 100% production tested.

Note 4: Feedthrough is reduced by connecting the metal lid on the ceramic package (suffix D) to DGND.

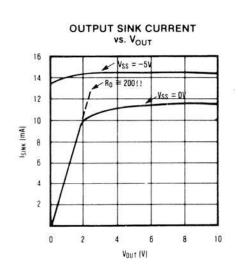

# Typical Operating Characteristics

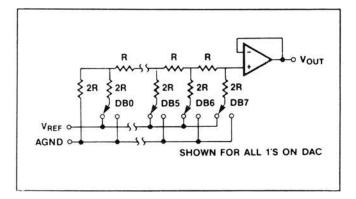

# Detailed Description D/A Section

The MX7224 contains an 8-bit digital-to-analog converter that operates in the voltage output mode. The output voltage is of the same polarity as the external reference voltage thus allowing single supply operation. A DAC switch pair arrangement on the MX7224 allows a reference voltage range from +2V to +12.5V.

The DAC consists of a stable thin-film resistor R-2R ladder and eight NMOS single pole, double-throw switches. A simplified circuit diagram is shown in Figure 1.

Figure 1. D/A Simplified Circuit Diagram

The input impedance at the  $V_{REF}$  pin is code dependent and varies from  $8k\Omega$  minimum to infinity. The lowest input impedance occurs when the DAC is loaded with the digital code 01010101. Therefore, it is important that the reference presents a low impedance under changing load conditions. Capacitance at the reference terminal is also code dependent and typically varies from 25pF to 50pF.

The  $V_{\text{OUT}}$  pin can be considered as a digitally-programmable voltage source with the output defined by:

$$V_{OUT} = D \cdot V_{REF}$$

where D is a fractional representation of the digital input code and can vary from 0 to 255/256.

#### **Output Buffer Amplifier**

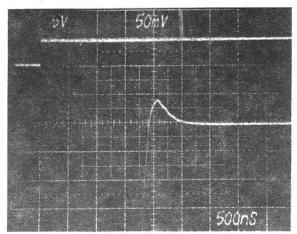

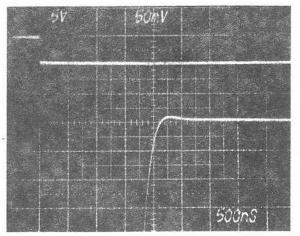

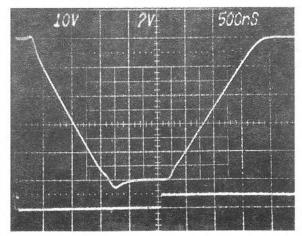

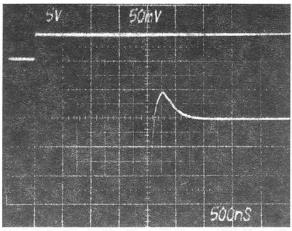

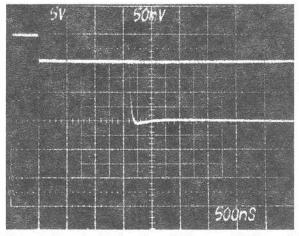

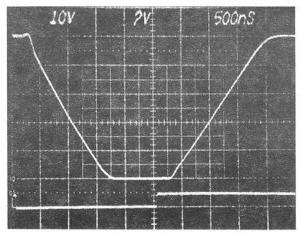

The DAC's voltage output is buffered by a unity-gain CMOS voltage follower that slews at greater than 2.5V/ $\mu$ s. This amplifier is capable of driving a  $2k\Omega$  load to +10V. When driving a  $2k\Omega$  load in parallel with 100pF with full-scale transitions (0V to +10V or +10V to 0V), the output settles to 1/2LSB in less than  $5\mu$ s. Typical dynamic response and settling performance of the MX7224 is shown in Figures 2 through 7.

The MX7224 can be operated single or dual supply. In single supply operation, Maxim's MX7224 can sink and source up to 5mA.

Figure 2. Positive Settling Time with VDD = +15V, VSS = -5V

Figure 4. Negative Settling Time with VDD = +15V, Vss = -5V

Figure 6. Dynamic Response with  $V_{DD} = +15V$ ,  $V_{SS} = -5V$ .

Figure 3. Positive Settling Time with  $V_{DD} = +15V$ ,  $V_{SS} = 0V$ .

Figure 5. Negative Settling Time with VDD = +15V, Vss = 0V.

Figure 7. Dynamic Response with VDD = +15V, VSS = 0V.

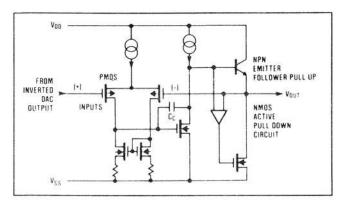

A simplified circuit diagram of the output buffer is shown in Figure 8. Input common-mode range to  $V_{SS}$  is provided by a PMOS input structure. The improved output circuitry incorporates a Maxim proprietary pull-down circuit to actively drive  $V_{OUT}$  to within typically +15mV of the negative supply ( $V_{SS}$ ). Maxim's improved buffer circuitry allows the output to sink and source up to 5mA. This is especially important in single supply applications, where  $V_{SS}$  is connected to GND, so that zero error is kept at or under 1/2LSB ( $V_{REF}$  = +10V). A plot of output sink current versus output voltage is shown in the Typical Operating Characteristics section.

Figure 8. Simplified Output Buffer Circuit

#### Digital Inputs and Interface Logic

The digital inputs are compatible with both TTL and 5V CMOS logic. Power supply current, I<sub>DD</sub> and I<sub>SS</sub>, are specified for TTL input levels. The supply currents are somewhat dependent on input logic level and are highest when the MX7224 is driven from TTL, however, they can be significantly reduced if the inputs are driven as close to +5V as possible.

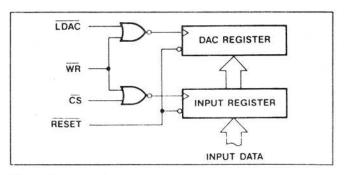

Table 1 shows the truth table for MX7224 operation. The part contains two registers, an input register and a DAC register. CS and WR control the loading of the input register while LDAC and WR control the transfer of information from the input to the DAC register. Only the data held in the DAC register will determine the converter's analog output.

All control signals are level-triggered and therefore either or both registers may be made transparent; the input register by keeping CS and WR "LOW," the DAC register by keeping LDAC and WR "LOW." The rising edge of the WR input latches input data.

The contents of both registers are reset by a low level on the RESET line. With both registers transparent, the RESET line overrides input data for the duration of the RESET pulse. If both registers are latched, a "LOW" pulse on the RESET will latch all 0's into the registers, with the output remaining at 0V after the reset pulse has been removed. The RESET line can be used to force 0V on the output at power-up, and is also useful as a zero override in system calibration cycles. Figure 9 shows the input control logic for the MX7224.

Table 1. MX7224 Truth Table

| RESET | LDAC | WR | CS | Function                                                               |

|-------|------|----|----|------------------------------------------------------------------------|

| н     | L    | L  | L  | Both Registers are<br>Transparent                                      |

| Н     | х    | н  | Х  | Both Registers are Latched                                             |

| Н     | н    | Х  | Н  | Both Registers are Latched                                             |

| н     | н    | L  | L  | Input Register Transparent                                             |

| н     | н    |    | L  | Input Register Latched                                                 |

| н     | L    | L  | Н  | DAC Register Transparent                                               |

| Н     | L    | 5  | н  | DAC Register Latched                                                   |

| L     | х    | х  | Х  | Both Registers Loaded with all Zeros                                   |

|       | н    | н  | Н  | Both Registers Latched<br>with all Zeros and Output<br>Remains at Zero |

| 5     | L    | L  | L  | Both Registers are<br>Transparent and Output<br>Follows Input Data     |

H = High State, L = Low State, X = Don't Care

Figure 9. Input Control Logic

Figure 10. Write Cycle Timing Diagram

# Applications Information Power Supply and Reference Operating Ranges

The MX7224 is fully specified to operate with  $V_{DD}$  between +12V  $\pm$  5% and +15V  $\pm$  10% (+11.4V to +16.5V), and with  $V_{SS}$  from 0V to -5.5V. Eight bit performance is also guaranteed for single supply operation ( $V_{SS}$  = 0V), however zero code error is reduced when  $V_{SS}$  is -5V (see Output Buffer Amplifier section).

For adequate DAC and buffer operating range, the  $V_{REF}$  voltage must always be at least 4V below  $V_{DD}$ . The MX7224 is specified to operate with a reference input range of +2V to  $V_{DD}$  - 4V.

#### **Ground Management**

Digital or AC transient signals between AGND and DGND will create noise at the analog outputs. It is recommended that AGND and DGND be tied together at the DAC and that this point be tied to the highest quality ground that is available. If separate ground busses are used, then two clamp diodes (1N914 or equivalent) should be connected between AGND and DGND to keep the two ground busses within one diode drop of each other. To avoid parasitic device turn-on, AGND must not be allowed to be more negative than DGND. DGND should be used as supply ground for bypassing purposes.

Careful PCB ground layout techniques should be used to minimize crosstalk between the DAC output, the reference input, and the digital inputs. This is particularly important if the reference is driven from an AC source.

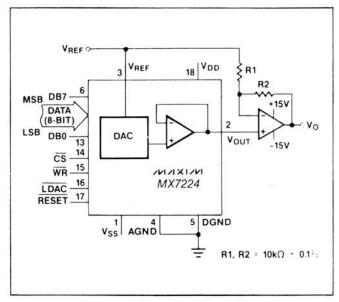

#### **Unipolar Output**

In unipolar operation, the output voltage and the reference input are the same polarity. The unipolar circuit configuration is shown in Figure 11. A slight increase in zero error occurs when the MX7224 is operated from a single supply (see Output Buffer Amplifier section). To avoid parasitic device turn-on, the voltage at V<sub>REF</sub> must always be positive with respect to DGND. The unipolar code table is given in Table 2.

Figure 11. Unipolar Output Circuit

Table 2. Unipolar Code Table

|   |    | AC | со | NTE | NT | s  |   |                                                             |

|---|----|----|----|-----|----|----|---|-------------------------------------------------------------|

| M | SB |    |    |     |    | LS | В | ANALOG OUTPUT                                               |

| 1 | 1  | 1  | 1  | 1   | 1  | 1  | 1 | $+V_{REF}\left(\frac{255}{256}\right)$                      |

| 1 | 0  | 0  | 0  | 0   | 0  | 0  | 1 | $+V_{REF}\left(\frac{129}{256}\right)$                      |

| 1 | 0  | 0  | 0  | 0   | 0  | 0  | 0 | $+V_{REF}\left(\frac{128}{256}\right) = +\frac{V_{REF}}{2}$ |

| 0 | 1  | 1  | 1  | 1   | 1  | 1  | 1 | $+V_{REF}\left(\frac{127}{256}\right)$                      |

| 0 | 0  | 0  | 0  | 0   | 0  | 0  | 1 | $+V_{REF}\left(\frac{1}{256}\right)$                        |

| 0 | 0  | 0  | 0  | 0   | 0  | 0  | 0 | ov                                                          |

Note: 1LSB =  $(V_{REF})(2^{-8}) = +V_{REF} \left(\frac{1}{256}\right)$

#### **Bipolar Output**

The DAC output may be configured for bipolar operation using the circuit in Figure 12. Only one op-amp and two resistors are required. With R1 = R2:

$$V_{OUT} = V_{REF} \cdot (2D - 1)$$

where D is a fractional representation of the digital word in the DAC regiser.

Table 3 shows the digital code versus output voltage for the circuit in Figure 12.

Figure 12. Bipolar Output Circuit

Table 3. Bipolar (Offset Binary) Code Table

| M | ISB |   | co | NTE | NT | S<br>LS | В | ANALOG OUTPUT                                        |

|---|-----|---|----|-----|----|---------|---|------------------------------------------------------|

| 1 | 1   | 1 | 1  | 1   | 1  | 1       | 1 | +V <sub>REF</sub> $\left(\frac{127}{128}\right)$     |

| 1 | 0   | 0 | 0  | 0   | 0  | 0       | 1 | +V <sub>REF</sub> $\left(\frac{1}{128}\right)$       |

| 1 | 0   | 0 | 0  | 0   | 0  | 0       | 0 | ov                                                   |

| 0 | 1   | 1 | 1  | 1   | 1  | 1       | 1 | $-V_{REF}\left(\frac{1}{128}\right)$                 |

| 0 | 0   | 0 | 0  | 0   | 0  | 0       | 1 | -V <sub>REF</sub> ( 127 )                            |

| 0 | 0   | 0 | 0  | 0   | 0  | 0       | 0 | $-V_{REF}$ $\left(\frac{128}{128}\right) = -V_{REF}$ |

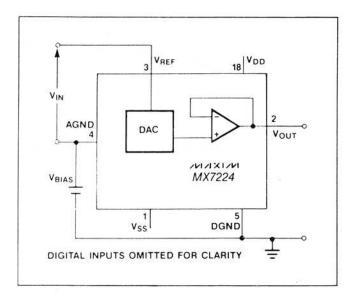

#### Offsetting AGND

AGND can be biased above DGND to provide an arbitrary non-zero output voltage for a "zero" input code. This is shown in Figure 13. The output voltage at  $V_{\text{OUT}}$  is:

$$V_{OUT} = V_{BIAS} + (D \cdot V_{IN})$$

where D is a fractional representation of the digital input word and can vary from 0 to 255/256. For a given  $V_{\rm IN}$ , increasing AGND above system GND will reduce the effective  $V_{\rm DD}\text{--}V_{\rm REF}$  which must be at least 4V to ensure specified operation. Note that  $V_{\rm DD}$  and  $V_{\rm SS}$  for the MX7224 must be referenced to DGND.

Figure 13. AGND Bias Circuit

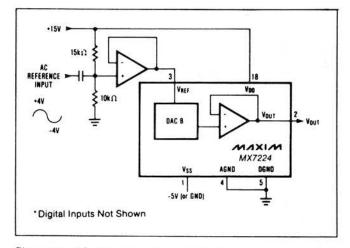

#### Using an AC Reference

In applications where  $V_{REF}$  has AC signal components, the MX7224 has multiplying capability within the limits of the  $V_{REF}$  input range specifications. Figure 14 shows a technique for applying a sinewave signal to the reference input where the AC signal is biased up before being applied to  $V_{REF}$ . Output distortion is typically less than 0.1% with input frequencies up to 50kHz, and the typical –3dB frequency is 700kHz. Note that  $V_{REF}$  must never be more negative than AGND

Figure 14. AC Reference Input Circuit

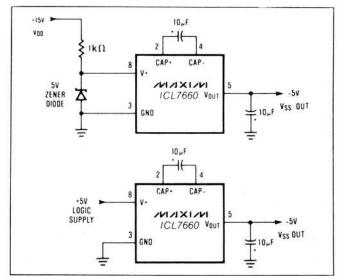

#### Generating V<sub>SS</sub>

The performance of the MX7224 is specified for both dual and single supply ( $V_{SS}$  = 0V) operation. When the improved performance of dual supply operation is desired, but only a single supply is available, a -5V  $V_{SS}$  supply can be generated using an ICL7660 in one of the circuits of Figure 15.

Figure 15. Generating -5V for V<sub>SS</sub>

# Microprocessor Interfacing

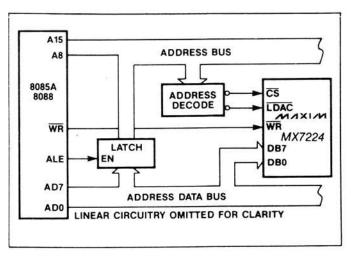

Figure 16. MX7224 to 8085A/8088 Interface

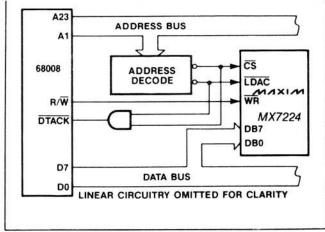

Figure 19. MX7224 to 68008 Interface

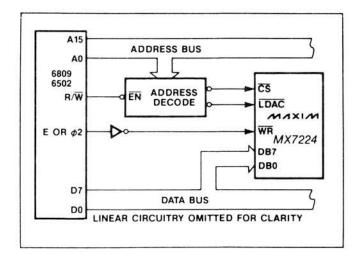

Figure 17. MX7224 to 6809/6502 Interface

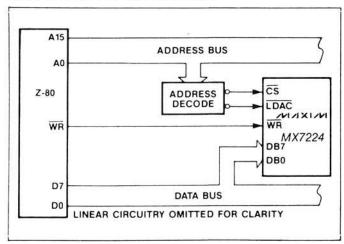

Figure 18. MX7224 to Z-80 Interface

## Chip Topography

# MX7224

# **CMOS 8-Bit DAC with Output Amplifier**

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.