### ASAHI KASEI

# AK2304A

QUAD PCM CODEC/FILTER COMBO LSI

#### Features

- □ Compliant to AT&T and ITU recommendations

- □ Monolithic 4-channel CODEC/Filter

- □ Suitable for PBX/KTS applications

- $\Box$  A-law/ $\mu$ -law pin selectable

- □ Integrated op-amps for input gain adjustment

- □ Integrated anti-alias filter

- □ 2.048Mb/s PCM data output

- □ Individual channel mute function

- □ Power down mode

- □ Single 5 volt operation

- □ 44 pin QFP package

- 1 -

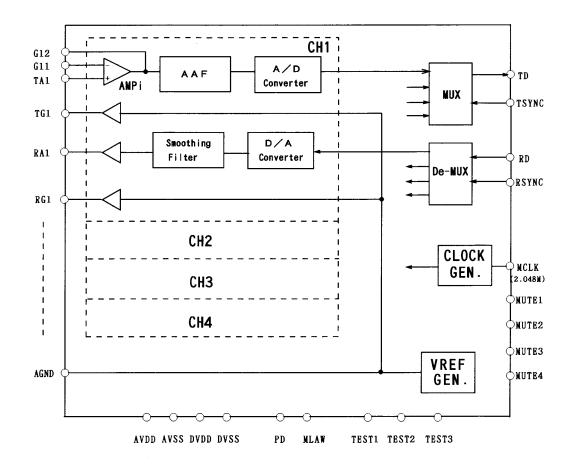

The AK2304A is an integrated monolithic quad PCM CODEC for PBX/KTS applications, which integrates band limiting filters, ADCs, DACs and A-law/ $\mu$ -law compressor/expander. The device can be set to either A-law or  $\mu$ -law companding by pin selection.

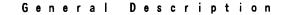

Pin assignment

Ordering information

AK2304A  $-40 \sim +85^{\circ}$ C 44 pin QFP

AKD2304 Evaluation board

[AK2304A]

## Circuit Description

| Block         | Function                                                                                                                                |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| AMP1~4        | Op-amps for input gain adjustment.                                                                                                      |

| Ami 1 4       | AK2304A has an op-amp at each analog input (CH1~CH4). Normally, this                                                                    |

|               | op-amp is used as an inverting amplifier. Adjusting the gain up to                                                                      |

|               | +12dB with external resistors. The resistor larger than 50k $\Omega$ is                                                                 |

|               | recommended for the feedback resistor.                                                                                                  |

|               |                                                                                                                                         |

|               | This op-amp can be also used as a differential amplifier, but it                                                                        |

|               | cannot be used as a non-inverting amplifier.                                                                                            |

|               | As for the recommended value of external resistors and capacitors, see                                                                  |

| 110           | section "Application circuit example".                                                                                                  |

| AAF           | Integrated anti-aliasing filter which prevents signals around the                                                                       |

|               | sampling rate from folding back into the voiceband. AAF is a 2nd                                                                        |

|               | order low-pass filter and it provides typically -40dB gain at the                                                                       |

|               | sampling frequency.                                                                                                                     |

| A/D Converter | Converts analog signal to 8 bit PCM data according to the companding                                                                    |

|               | schemes of CCITT recommendation G. 711; A-Law or $\mu$ -Law. The band                                                                   |

|               | limiting filter is also integrated. The selection of companding                                                                         |

|               | schemes is set by MLAW pin as follows:                                                                                                  |

|               | ${}^{"}H^{"'1}: \mu - Law$                                                                                                              |

| MIN           | "L" <sup>1</sup> : A-Law                                                                                                                |

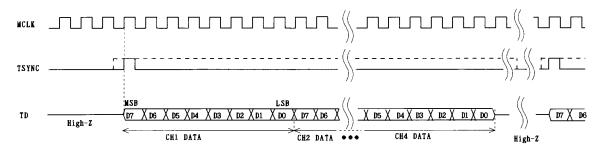

| MUX           | 8 bit PCM data from CH1 to CH4 (8bit * 4CH = 32 bit) is muxed into                                                                      |

|               | serial data of 2.048Mb/s on the rising edges of MCLK and comes out                                                                      |

|               | from TD. The start bit of transmit PCM data is defined by TSYNC. This                                                                   |

|               | 3-state output remains in the high impedance state except during the                                                                    |

|               | assigned transmit time slot. As for the transmit data timing, see sect                                                                  |

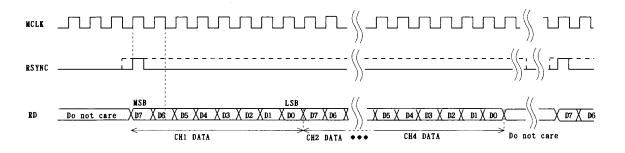

| De-MUX        | ion "Transmit Timing Diagrams".<br>Received serial PCM data (8bit * 4CH) from RD at the rate of 2.048Mb/s                               |

| De-MUX        |                                                                                                                                         |

|               | on the falling edges of MCLK is de-muxed into 4CH serial data. The start bit of receive PCM data is defined by RSYNC. The received data |

|               | is divided into 8bit blocks and sent to CH1 to CH4 sequentially. As                                                                     |

|               | for the receive data timing, see section "Receive Timing Diagrams".                                                                     |

| D/A Converter | Expands 8bit PCM data according to A-Law or $\mu$ -Law and reconstructs a                                                               |

|               | staircase form of analog signal. The selection of companding schemes                                                                    |

|               | is set by MLAW pin as follows:                                                                                                          |

|               | "H": $\mu$ -Law                                                                                                                         |

|               | "L": $A$ -Law                                                                                                                           |

| Smoothing     | The filter for attenuating the harmonic components from D/A output and                                                                  |

| Filter        | extracts the desired inband signal. It also corrects the $sinx/x$                                                                       |

|               | effect of D/A output.                                                                                                                   |

| VREF GEN.     | Provides the stable analog ground voltage (2.4V) using an on-chip                                                                       |

|               | band-gap reference circuit which is temperature compensated.                                                                            |

|               |                                                                                                                                         |

Note-1: "H" refers to high level digital signal. "L" refers to low level digital signal. ASAHI KASEI

٠

| P | i | n | 1 | F | u | n | С | t | i | 0 | n |  |

|---|---|---|---|---|---|---|---|---|---|---|---|--|

|   |   |   |   |   |   |   |   |   |   |   |   |  |

| Pin # | Name  | I/0 | Function                                         | Remarks                               |

|-------|-------|-----|--------------------------------------------------|---------------------------------------|

| 1     | MUTE1 | I   | Mute for CH1.                                    |                                       |

|       |       |     | When set "H", CH1 goes into mute mode. CH1       |                                       |

|       |       |     | output from TD goes to high impedance and RA1    |                                       |

|       |       |     | output goes to analog ground level.              |                                       |

| 2     | G12   | 0   | Output of AMP1.                                  | Note-1                                |

| 3     | G11   | I   | Inverting input of AMP1.                         | Note-1                                |

| 4     | TA1   | I   | Non-inverting input of AMP1.                     | Note-1                                |

| 5     | TG1   | 0   | Analog ground for CH1 analog output.             |                                       |

|       |       |     | To stabilize the analog ground, connect to       |                                       |

|       |       |     | AVSS with 4.7 $\mu$ F or larger.                 |                                       |

| 6     | RG1   | 0   | Analog ground for CH1 analog input.              |                                       |

| · ·   |       | _   | To stabilize the analog ground, connect to       |                                       |

|       |       |     | AVSS with 4.7 $\mu$ F or larger.                 |                                       |

| 7     | RA1   | 0   | CH1 analog output.                               |                                       |

| •     |       |     | This output can drive $10k\Omega$ or larger, and |                                       |

|       |       |     | 50pF or smaller.                                 |                                       |

| 8     | MUTE2 | I   | Mute for CH2.                                    |                                       |

| 0     | MOTOD | 1   | When set "H", CH2 goes into mute mode. CH2       |                                       |

|       |       |     | output from TD goes to high impedance and RA2    |                                       |

|       |       |     | output goes to analog ground level.              |                                       |

| 9     | G22   | 0   | Output of AMP2.                                  | Note-1                                |

| 10    | G21   | I   | Inverting input of AMP2.                         | Note-1                                |

| 11    | TA2   | I   | Non-inverting input of AMP2.                     | Note-1                                |

| 12    | TG2   | 0   | Analog ground for CH2 analog output.             | Note 1                                |

| 12    | 102   |     | To stabilize the analog ground, connect to       |                                       |

|       |       |     | AVSS with 4.7 $\mu$ F or larger.                 |                                       |

| 13    | RG2   | 0   | Analog ground for CH2 analog input.              |                                       |

| 10    | KU2   | , v | To stabilize the analog ground, connect to       |                                       |

|       |       |     | AVSS with 4.7 $\mu$ F or larger.                 |                                       |

| 14    | RA2   | 0   | CH2 analog output.                               | · · · · · · · · · · · · · · · · · · · |

| 14    | INAL  |     | This output can drive $10k\Omega$ or larger, and |                                       |

|       |       |     | 50pF or smaller.                                 |                                       |

| 15    | TEST1 | I   | Test pin reserved for factory use.               |                                       |

| 10    | 10011 |     | When "H", this device goes into test mode.       |                                       |

|       |       |     | Tie to DVSS for normal operation.                |                                       |

| 16    | TEST2 | I   | Test pin reserved for factory use.               |                                       |

| 10    | 16012 | 1   | When "H", this device goes into test mode.       |                                       |

|       |       |     | Tie to DVSS for normal operation.                |                                       |

| 17    | AVDD  | -   | Power supply for analog section.                 |                                       |

|       |       |     |                                                  |                                       |

| 18    | AVSS  | I   | Ground for analog section.                       |                                       |

| 19    | TEST3 |     | Test pin reserved for factory use.               |                                       |

|       |       |     | When "H", this device goes into test mode.       |                                       |

| 0.0   | DIO   | 0   | Tie to DVSS for normal operation.                |                                       |

| 20    | RA3   | 0   | CH3 analog output.                               |                                       |

|       |       |     | This output can drive $10k\Omega$ or larger, and |                                       |

|       |       |     | 50pF or smaller.                                 |                                       |

| Pin # | Name       | I/0 | Function                                                   | Remarks |

|-------|------------|-----|------------------------------------------------------------|---------|

| 21    | RG3        | 0   | Analog ground for CH3 analog input.                        |         |

|       |            |     | To stabilize the analog ground, connect to                 |         |

|       |            |     | AVSS with 4.7 $\mu$ F or larger.                           |         |

| 22    | TG3        | 0   | Analog ground for CH3 analog output.                       |         |

|       | _          |     | To stabilize the analog ground, connect to                 |         |

|       |            |     | AVSS with 4.7 $\mu$ F or larger.                           |         |

| 23    | TA3        | Ι   | Non-inverting input of AMP3.                               | Note-1  |

| 24    | G31        | I   | Inverting input of AMP3.                                   | Note-1  |

| 25    | G32        | 0   | Output of AMP3.                                            | Note-1  |

| 26    | MUTE3      | T   | Mute for CH3.                                              |         |

| 20    | morbo      | -   | When set "H", CH3 goes into mute mode. CH3                 |         |

|       |            |     | output from TD goes to high impedance and RA3              |         |

|       |            |     | output goes to analog ground level.                        |         |

| 27    | RA4        | 0   | Cfl4 analog output.                                        |         |

| 21    | <b>KA4</b> | U   |                                                            |         |

|       |            |     | This output can drive $10k\Omega$ or larger, and           |         |

| 0.0   | DO 4       | -   | 50pF or smaller.                                           |         |

| 28    | RG4        | 0   | Analog ground for CH4 analog input.                        |         |

|       |            |     | To stabilize the analog ground, connect to                 |         |

|       |            |     | AVSS with 4.7 $\mu$ F or larger.                           |         |

| 29    | TG4        | 0   | Analog ground for CH4 analog output.                       |         |

|       |            |     | To stabilize the analog ground, connect to                 |         |

|       |            |     | AVSS with 4.7 $\mu$ F or larger.                           |         |

| 30    | TA4        | I   | Non-inverting input of AMP4.                               | Note-1  |

| 31    | G41        | I   | Inverting input of AMP4.                                   | Note-1  |

| 32    | G42        | 0   | Output of AMP4.                                            | Note-1  |

| 33    | MUTE4      | I   | Mute for CH4.                                              |         |

|       |            |     | When set "H", CH4 goes into mute mode. CH4                 |         |

|       |            |     | output from TD goes to high impedance and RA4              |         |

|       |            |     | output goes to analog ground level.                        |         |

| 34    | PD         | Ι   | Power down.                                                |         |

|       |            |     | When "H", this device goes into power down                 |         |

|       |            |     | mode. TD output and RA1 to RA4 output go to                |         |

|       |            |     | high impedance.                                            |         |

| 35    | MCLK       | Ι   | Master clock 2.048MHz input.                               |         |

| 36    | RSYNC      | I   | Receive frame sync input.                                  |         |

|       |            |     | Input 8kHz clock to define the start bit of                |         |

|       |            |     | the receive time slot.                                     |         |

| 37    | RD         | Ι   | 2.048Mb/s PCM data input.                                  |         |

|       | '          | -   | The 32bit (8bit * 4CH) received PCM data is                |         |

|       |            |     | shifted in on the falling edges of MCLK. The               |         |

|       | -          |     | start bit of received PCM data is defined by               |         |

|       |            |     | RSYNC.                                                     |         |

| 38    | DVSS       | · _ | Ground for digital section.                                |         |

| 39    | DVSS       | _   | $+5V \pm 5\%$ Power supply for digital section.            |         |

| 40    | TSYNC      | I   | Transmit frame sync input. $101 \text{ digital section}$ . |         |

| 40    | ISING      | 1   | · · · ·                                                    |         |

|       |            |     | Input 8kHz clock to define the start bit of                |         |

|       |            | 1   | the transmit time slot.                                    |         |

| Pin # | Name | I/0 | Function                                      | Remarks |

|-------|------|-----|-----------------------------------------------|---------|

| 41    | TD   | 0   | PCM data output at 2.048Mb/s.                 |         |

|       |      |     | The 32bit (4CH * 8bit) serial transmit PCM    |         |

|       |      |     | data is shifted out on the rising edges of    |         |

|       |      |     | MCLK. The start bit of transmit PCM data is   |         |

|       |      |     | defined by TSYNC. This 3-state output remains |         |

|       |      |     | in the high impedance state except during the |         |

|       |      |     | assigned transmit time slot.                  |         |

| 42    | NC   | -   | No connection (Left open).                    | Note-2  |

| 43    | AGND | 0   | Analog ground output.                         |         |

|       |      |     | To stabilize the analog ground, connect to    |         |

|       |      |     | AVSS with 4.7 $\mu$ F or larger.              |         |

| 44    | MLAW | Ι   | Companding schemes selection.                 |         |

|       |      |     | "Η": μ-Law                                    |         |

|       |      |     | "L": A-Law                                    |         |

Note-1: Normally, form the inverting amplifier with external resistors for gain adjustment. For more information, see section "Circuit Description" and "Application Circuit Examples".

Note-2: This pin is used as the digital output during test mode.

### Absolute Maximum Ratings

| Parameter                         | Symbol | min  | max      | units |

|-----------------------------------|--------|------|----------|-------|

| Power Supply Voltages (Note-1, 2) |        |      |          |       |

| Digital Power Supply              | DVDD   | -0.3 | 6.5      | V     |

| Analog Power Supply               | AVDD   | -0.3 | 6.5      | V     |

| Digital Input Voltage (Note-1)    | V I ND | -0.3 | AVDD+0.3 | V     |

| Analog Input Voltage (Note-1)     | VINA   | -0.3 | AVDD+0.3 | V     |

| Storage Temperature               | Tstg   | -55  | 125      | C     |

Note-1: AVSS=DVSS=OV, all voltages with respect to ground. Note-2: When DVDD exceeds AVDD, permanent damage may be caused to the device.

Warning: Exceeding absolute maximum ratings may cause permanent damage. Normal operation is not guaranteed at these extremes.

### Recommended Operating Conditions

| Parameter                     | Symbol | min  | typ | max  | units |

|-------------------------------|--------|------|-----|------|-------|

| Power Supply Voltage (Note-1) |        |      |     |      |       |

| Digital Power Supply          | DVDD   | 4.75 | 5.0 | 5.25 | V     |

| Analog Power Supply           | AVDD   | 4.75 | 5.0 | 5.25 | V     |

| Ambient Operating Temperature | Та     | -40  |     | 85   | °C    |

Note-1: AVSS=DVSS=OV, all voltages with respect to ground.

### Electrical Characteristics

Unless otherwise noted, guaranteed for AVDD = DVDD =  $+5V \pm 5\%$ , Ta =  $-40 \sim +85$  °C.

**DC** characteristics

| Parameter         | Symbol | conditions                 | min    | typ | max | units |

|-------------------|--------|----------------------------|--------|-----|-----|-------|

| Power Consumption | IDD    | Normal operation           |        |     |     |       |

|                   |        | supplying MCLK             |        | 15  | 20  | mA    |

|                   |        | No load at all output pins |        |     |     |       |

|                   |        | Power down mode.           |        |     |     |       |

|                   |        | No load at all output pins |        | 1   | 10  | μA    |

|                   |        | (Note-1)                   |        |     |     |       |

| Input Leak        | Ii     |                            |        |     | ±10 | μA    |

| "H" Output Level  | VOH    | IOH = -2mA                 | DVDD-1 |     |     | V     |

| "L" Output Level  | VOL    | IOL = 2mA                  |        |     | 0.4 | V     |

| "H" Input Level   | VIH    | (Note-2)                   | 2.0    |     |     | V     |

| "L" Input Level   | VIL    | (Note-2)                   |        |     | 0.8 | V     |

Note-1: Connect PD pin to DVDD and connect the others digital input to DVSS Note-2: Except test pins

Analog Characteristics

| Parameter                              | Condit                        | ions               | min   | typ   | max   | units  |

|----------------------------------------|-------------------------------|--------------------|-------|-------|-------|--------|

| Signal to Total                        | 1020Hz                        | -45dBm0            | 23    | -     | -     |        |

| Distortion                             | Sinusoidal test               | -40dBm0            | 28    | _     |       | dB     |

| $(A \rightarrow A)$                    | with C-message                | 0,-30dBm0          | 34    | -     | -     |        |

| Gain Tracking                          | Reference Level               | -55dBm0            | -1.0  | _     | 1.0   |        |

| $(A \rightarrow A)$                    | -10dBm0@1020Hz                | -50dBm0            | -0.5  | _     | 0.5   | dB     |

|                                        | Sinusoidal test               | 3,-40dBm0          | -0.3  | _     | 0.3   |        |

| Analog Input Level                     | Input: OdBm0 @ 1              | 1020Hz             |       | 0.849 |       | Vrms   |

| Analog Output Level                    | Input: OdBmO @ 1              | 020Hz Code         |       | 0.849 |       | Vrms   |

| TX Gain, Absolute                      | 0dBm0@1020Hz                  |                    | -0.6  |       | 0.6   | dB     |

| RX Gain, Absolute                      | VUDBIVEIUZVIIZ                |                    | -0.6  | -     | 0.6   | dB     |

| Idle Channel Noise                     | $\mu$ -law, with C-m          |                    | —     | 5     | 10    | dBrnC0 |

| $A \rightarrow D$ (Note-1)             | A-law, with P-me              | essage             | —     | -85   | -80   | dBmOp  |

| Idle Channel Noise                     | $\mu$ -law, with C-m          | nessage            | -     | 5     | 10    | dBrnC0 |

| $D \rightarrow A$ (Note-2)             | A-law, with P-me              | —                  | -85   | -80   | dBm0p |        |

| Crosstalk between<br>Channels (Note-3) | A to A, Input: (              | )dBm0@1020Hz       | _     | -90   | -82   | dB     |

| Freewordt, Beeronee                    | Input: 0 dBm0                 | 0.06kHz            | 24    | _     | _     |        |

| Frequency Response $(A \rightarrow D)$ | Relative to                   | 0.2kHz             | 0     | -     | 2.5   |        |

| $(A \rightarrow D)$                    | 0dBm0@1020Hz                  | 0.3~3.0kHz         | -0.15 | —     | 0.15  | dB     |

|                                        |                               | 3.4kHz             | 0     | _     | 0.8   |        |

|                                        |                               | 3. 78kHz           | 6.5   | —     | -     |        |

| Frequency Response                     | Input: 0 dBm0                 | 0∼3.0kHz           | -0.15 | _     | 0.15  |        |

| $(D \rightarrow A)$                    | Relative to                   | 3. 4kHz            | 0     | —     | 0.8   | dB     |

|                                        | 0dBm0@1020Hz                  | 3. 78kHz           | 6.5   | —     |       |        |

| Spurious Out-of-Band                   | Input: 0 dBm0,                | 4.6k $\sim$ 7.6kHz |       |       | -30   |        |

| Signals                                | 300Hz~3400Hz                  | 7.6k∼8.4kHz        |       |       | -40   | dB     |

| (Note-4)                               | PCM Code                      | 8.4k $\sim$ 50kHz  |       |       | -30   |        |

| PSRR                                   | AVDD=DVDD= 5.0V $\pm$ 100mVop |                    | _     | 45    | _     | dB     |

| $(A \rightarrow A)$                    | f=300Hz~100kHz                |                    |       |       |       | uD     |

| Delay, Absolute                        | $A \rightarrow D$ , f=1300Hz  |                    | _     | 290   | 300   | μs     |

| (Note-4)                               | D→A, f=1300Hz                 |                    |       | 180   | 230   | μο     |

Note-1: Analog input = Analog ground

Note-2: Digital input (RD) = +0 Code

Note-3: Measured with 4.7  $\mu\,F$  capacitor between AGND, TGi, RGi, and AVSS respectively.

Note-4: Not tested in production test.

Parameters guaranteed by design and characterization.

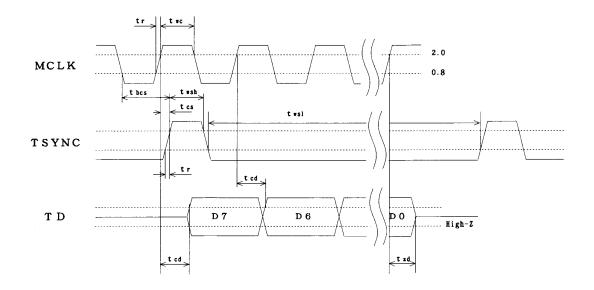

| Parameter                          | Symbol                                 | min | typ   | max | units |

|------------------------------------|----------------------------------------|-----|-------|-----|-------|

| Master Clock Frequency             | MCLK                                   |     | 2.048 |     | MHz   |

| Rise Time of Digital Input(Note-3) | tr                                     | 5.0 | _     | 50  | ns    |

| Fall Time of Digital Input(Note-3) | tf                                     | 5.0 | -     | 50  | ns    |

| Clock Pulse Width                  | twc                                    | 195 | 244   | 293 | ns    |

| Transmitter Side Timing            | •••••••••••••••••••••••••••••••••••••• | •   |       | •   | ·     |

| TSYNC High Period                  | twsh                                   | 200 | _     |     | ns    |

| TSYNC Low Period                   | twsl                                   | 8   | -     | -   | μs    |

| Hold Time from MCLK rising         | tcs                                    | -   | -     | 100 | ns    |

| edge to TSYNC                      |                                        |     |       |     |       |

| Hold Time from MCLK falling        | tbcs                                   | 0   | -     | _   | ns    |

| edge to TSYNC                      |                                        |     |       |     |       |

| Delay Time from MCLK rising        | tcd                                    | -   |       | 180 | ns    |

| edge to Data Valid (Note-1)        |                                        |     |       |     |       |

| Delay Time from MCLK rising        | tzd                                    | _   | _     | 30  | ns    |

| edge to High-Z (Note-2,3)          |                                        |     |       |     |       |

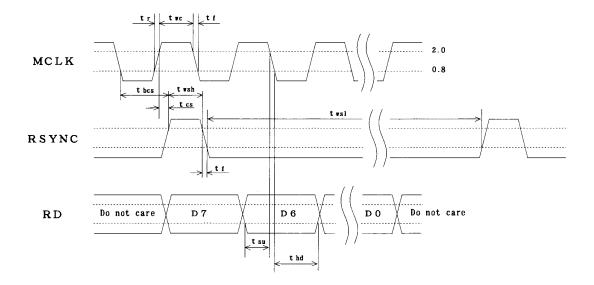

| Receiver Side Timing               |                                        |     |       |     |       |

| RSYNC High Period                  | twsh                                   | 200 | -     | —   | ns    |

| RSYNC Low Period                   | twsl                                   | 8   | _     | —   | μs    |

| Hold Time from MCLK rising         | tcs                                    | -   | -     | 100 | ns    |

| edge to RSYNC                      |                                        |     |       |     |       |

| Hold Time from MCLK falling        | tbcs                                   | 0   | —     | _   | ns    |

| edge to RSYNC                      |                                        |     |       |     |       |

| Set-up Time from RD Valid          | tsu                                    | 65  |       |     | ns    |

| to MCLK falling edge               |                                        |     |       |     |       |

| Hold Time from MCLK falling        | thd                                    | 120 | -     | —   | ns    |

| edge to RD Invalid                 |                                        |     |       |     |       |

# Switching Characteristics (Refer to Timing Diagrams)

Note-1: Measured with 50pF.

Note-2: With no load capacitance.

Note-3: Not tested in production test.

Parameters guaranteed by design and characterization.

Transmit Timing Diagrams

1996/4

[AK2304A]

[AK2304A]

Receive Timing Diagrams

Note: As for RSYNC timing, refer to  $t_{bcs}$ ,  $t_{cs}$  and  $t_{ws1}$  of Timing Diagrams below.

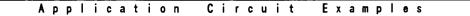

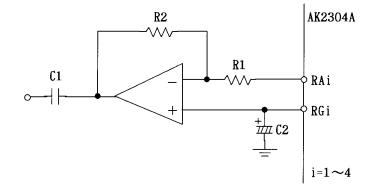

1. Analog input circuit (AMP1~AMP4)

AK2304A has an op-amp at analog input of each channel. Each op-amp can be used as a gain adjustment.

Op-amp can be used as an inverting amplifier or a differential amplifier, but not as a non-inverting amplifier.

Where, Gain: 12dB or smaller, Feedback resistor:  $50k\Omega$  or larger

(Circuit example as inverting amplifier)

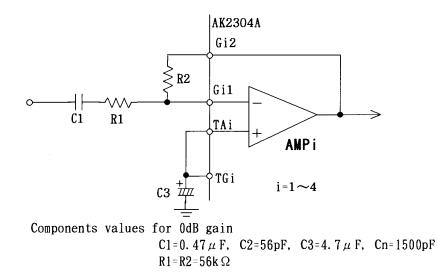

(Circuit Example as differential amplifier)

Components values for OdB gain C1=C2=0.47  $\mu$  F, C3=C4=56pF, C5=4.7  $\mu$  F, Cn=1500pF R1=R2=R3=R4=56k  $\Omega$  2. Analog output circuit

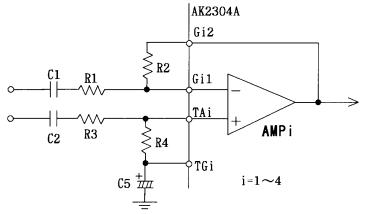

Each AK2304A analog output can drive  $10k\Omega$  or larger, and 50pF or smaller. To drive  $10k\Omega$  or smaller loads, use external op-amps. Since AK2304A analog output is biased, form a high pass filter if necessary.

(Circuit example used inverting amplifier)

Components values for OdB gain C1=0.47  $\mu$  F, C2=4.7  $\mu$  F R1=R2=33k  $\Omega$

(Circuit example used single power supply op-amp)

Components values for OdB gain C1=0. 47  $\mu$  F, C2=4.7  $\mu$  F R1=R2=33k  $\Omega$

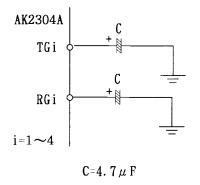

3. Analog ground stabilization capacitor

To stabilize each analog ground (TGi and RGi,  $i=1\sim4$ ), connect to AVSS through 4.7  $\mu$  F or larger capacitor.

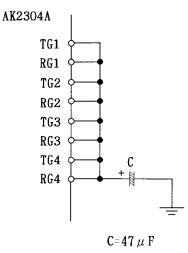

When connecting all analog ground to AVSS through only one capacitor, connect to AVSS through  $47\,\mu$  F or larger capacitor, as shown below. This method could result in higher cross-talk than in above circuit.

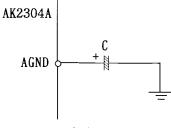

4. Analog reference voltage stabilization capacitor To stabilize the reference voltage (analog ground), connect 4.7 $\mu$ F or larger capacitor between AGND and AVSS.

C=4.7 $\mu$ F

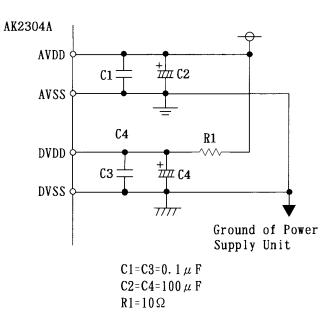

### 5. Power Supply

To use the same supply for both digital and analog power supply (DVDD and AVDD), insert  $10\Omega$  resistor between AVDD and DVDD, and separate analog VSS and digital VSS and connect them at power supply unit.

To attenuate the power supply noise, connect capacitors between AVDD and AVSS, and DVDD and DVSS, as shown below.

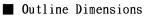

### Packaging Information

### □ 44 Pin QFP

### Marking

- (1) Pin # 1 indication

- (2) Date Code: 7 Digits XXXXXXX

- (3) Marketing Code: AK2304A

- (4) Country of Origin: JAPAN

- (5) Asahi Kasei Logo

### **IMPORTANT NOTICE**

- These products and their specifications are subject to change without notice. Before considering any use or application, consult the Asahi Kasei Microsystems Co., Ltd. (AKM) sales office or authorized distributor concerning their current status.

- AKM assumes no liability for infringement of any patent, intellectual property, or other right in the application or use of any information contained herein.

- Any export of these products, or devices or systems containing them, may require an export license or other official approval under the law and regulations of the country of export pertaining to customs and tariffs, currency exchange, or strategic materials.

- AKM products are neither intended nor authorized for use as critical components in any safety, life support, or other hazard related device or system, and AKM assumes no responsibility relating to any such use, except with the express written consent of the Representative Director of AKM. As used here:

- (a) A hazard related device or system is one designed or intended for life support or maintenance of safety or for applications in medicine, aerospace, nuclear energy, or other fields, in which its failure to function or perform may reasonably be expected to result in loss of life or in significant injury or damage to person or property.

- (b) A critical component is one whose failure to function or perform may reasonably be expected to result, whether directly or indirectly, in the loss of the safety or effectiveness of the device or system containing it, and which must therefore meet very high standards of performance and reliability.

- It is the responsibility of the buyer or distributor of an AKM product who distributes, disposes of, or otherwise places the product with a third party to notify that party in advance of the above content and conditions, and the buyer or distributor agrees to assume any and all responsibility and liability for and hold AKM harmless from any and all claims arising from the use of said product in the absence of such notification.