# CY7C09269V/79V/89V CY7C09369V/89V

# <u>3.3 V 16 K / 32 K / 64 K × 16 / 18</u> Synchronous Dual-Port Static RAM

## Features

- True dual-ported memory cells that allow simultaneous access of the same memory location

- Six flow through/pipelined devices: I 16 K × 16 / 18 organization (CY7C09269V/369V) □ 32 K × 16 organization (CY7C09279V) G4 K × 16 / 18 organization (CY7C09289V/389V)

- Three modes:

- □ Flow through

- Pipelined

- Burst

- Pipelined output mode on both ports allows fast 100 MHz operation

- 0.35 micron CMOS for optimum speed and power

- High speed clock to data access: 7.5<sup>[1]</sup>, 9, 12 ns (max)

- 3.3 V low operating power: Active = 115 mA (typical)

- $\Box$  Standby = 10  $\mu$ A (typical)

- Fully synchronous interface for easier operation

- Burst counters increment addresses internally:

- Shorten cycle times

- Minimize bus noise

- Supported in flow through and pipelined modes

- Dual chip enables easy depth expansion

- Upper and lower byte controls for bus matching

- Automatic power down

- Commercial and industrial temperature ranges

- Pb-free 100-pin TQFP package available

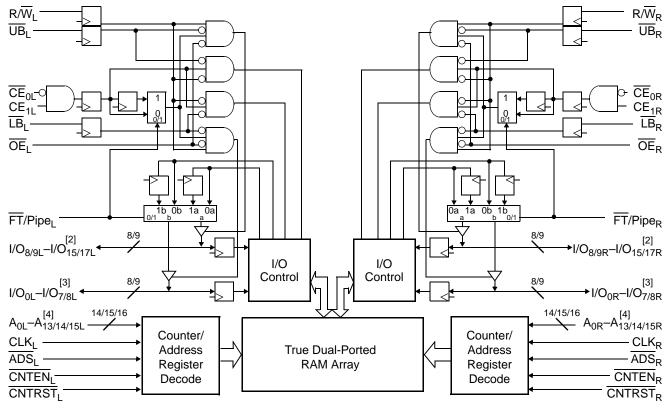

## Logic Block Diagram

#### Notes

- 1. See Figure 4 on page 8 for Load Conditions.

- 1. See Figure 4 on page 8 for Load Conditions. 2.  $I/O_8-I/O_{15}$  for x 16 devices;  $I/O_9-I/O_{17}$  for x 18 devices. 3.  $I/O_0-I/O_7$  for x 16 devices.  $I/O_0-I/O_8$  for x 18 devices. 4.  $A_0-A_{13}$  for 16K;  $A_0-A_{14}$  for 32K;  $A_0-A_{15}$  for 64K devices.

**Cypress Semiconductor Corporation** Document Number: 38-06056 Rev. \*I

198 Champion Court

٠

San JoseCA 95134-1709 408-943-2600 Revised August 1, 2012

# Contents

| 32 K × 16 3.3 V Synchronous Dual-Port SRAM | 18 |

|--------------------------------------------|----|

| ,<br>,                                     |    |

| 16 K × 18 3.3 V Synchronous Dual-Port SRAM | 18 |

| 64 K × 18 3.3 V Synchronous Dual-Port SRAM | 18 |

| Ordering Code Definitions                  | 19 |

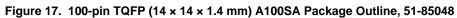

| Package Diagrams                           | 19 |

| Acronyms                                   |    |

| Document Conventions                       |    |

| Units of Measure                           |    |

|                                            | -  |

| Document History Page                      | 21 |

| Sales, Solutions, and Legal Information    | 22 |

| Worldwide Sales and Design Support         | 22 |

| Products                                   | 22 |

| PSoC Solutions                             | 22 |

|                                            |    |

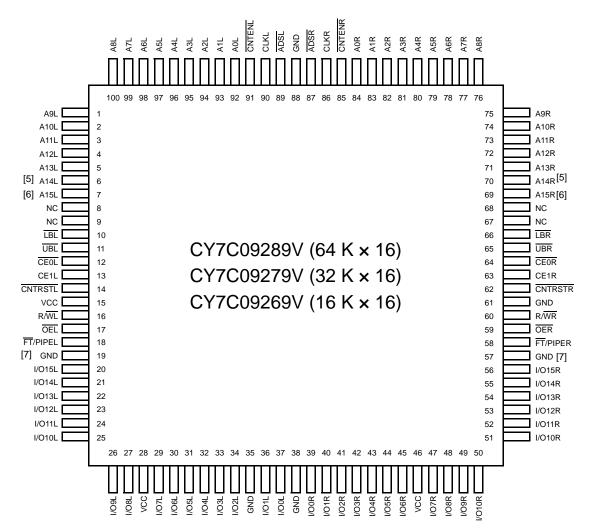

## **Pin Configurations**

Figure 1. 100-pin TQFP (Top View)

Notes

- 5. This pin is NC for CY7C09269V.

- 6. This pin is NC for CY7C09269V and CY7C09279V.

- 7. For CY7C09269V and CY7C09279V, pin #18 connected to V<sub>CC</sub> is pin compatible to an IDT 5 V x 16 pipelined device; connecting pin #18 and #58 to GND is pin compatible to an IDT 5 V x 16 flow through device.

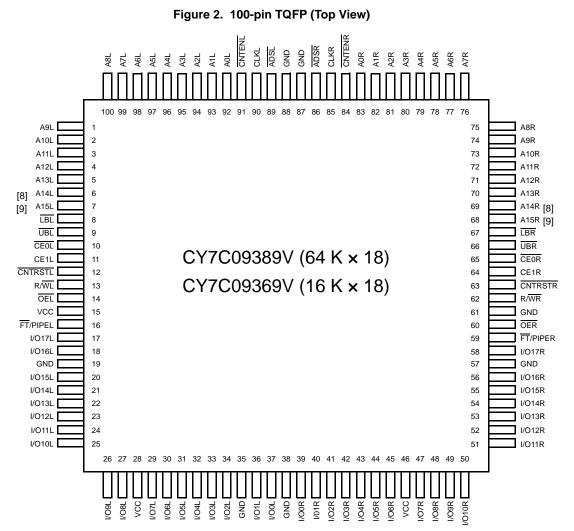

## Pin Configurations (continued)

Notes

8. This pin is NC for CY7C09369V.

9. This pin is NC for CY7C09369V.

# **Selection Guide**

| Specifications                                                                  | CY7C09269V/79V/89V<br>CY7C09369V/89V | CY7C09269V/79V/89V<br>CY7C09369V/89V | CY7C09269V/79V/89V<br>CY7C09369V/89V |

|---------------------------------------------------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|

|                                                                                 | <b>-7</b> <sup>[10]</sup>            | -9                                   | -12                                  |

| f <sub>MAX2</sub> (MHz) (Pipelined)                                             | 83                                   | 67                                   | 50                                   |

| Max. Access Time (ns) (Clock to Data, Pipelined)                                | 7.5                                  | 9                                    | 12                                   |

| Typical Operating Current I <sub>CC</sub> (mA)                                  | 155                                  | 135                                  | 115                                  |

| Typical Standby Current for I <sub>SB1</sub> (mA) (Both Ports TTL Level)        | 25                                   | 20                                   | 20                                   |

| Typical Standby Current for $I_{SB3}\left(\mu A\right)$ (Both Ports CMOS Level) | 10                                   | 10                                   | 10                                   |

# **Pin Definitions**

| Left Port                             | Right Port                            | Description                                                                                                                                                                                                                                                                                                     |

|---------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0L</sub> -A <sub>15L</sub>     | A <sub>0R</sub> -A <sub>15R</sub>     | Address Inputs (A <sub>0</sub> -A <sub>14</sub> for 32K, A <sub>0</sub> -A <sub>13</sub> for 16K devices).                                                                                                                                                                                                      |

| ADSL                                  | ADS <sub>R</sub>                      | Address Strobe Input. Used as an address qualifier. This signal must be asserted LOW to access the part using an externally supplied address. Asserting this signal LOW also loads the burst counter with the address present on the address pins.                                                              |

| CE <sub>0L</sub> , CE <sub>1L</sub>   | CE <sub>0R</sub> ,CE <sub>1R</sub>    | <b>Chip Enable Input.</b> To select either the left or right port, both $\overline{CE}_0$ AND $CE_1$ must be asserted to their active states ( $\overline{CE}_0 \le V_{IL}$ and $CE_1 \ge V_{IH}$ ).                                                                                                            |

| CLKL                                  | CLK <sub>R</sub>                      | Clock Signal. This input can be free running or strobed. Maximum clock input rate is f <sub>MAX</sub> .                                                                                                                                                                                                         |

| CNTENL                                | CNTENR                                | <b>Counter Enable Input.</b> Asserting this signal LOW increments the burst address counter of its respective port on each rising edge of CLK. CNTEN is disabled if ADS or CNTRST are asserted LOW.                                                                                                             |

| CNTRSTL                               | CNTRSTR                               | <b>Counter Reset Input.</b> Asserting this signal LOW resets the burst address counter of its respective port to zero. CNTRST is not disabled by asserting ADS or CNTEN.                                                                                                                                        |

| I/O <sub>0L</sub> -I/O <sub>17L</sub> | I/O <sub>0R</sub> -I/O <sub>17R</sub> | Data Bus Input/Output (I/O <sub>0</sub> -I/O <sub>15</sub> for x 16 devices).                                                                                                                                                                                                                                   |

| LBL                                   | LB <sub>R</sub>                       | <b>Lower Byte Select Input</b> . Asserting this signal LOW enables read and write operations to the lower byte. ( $I/O_0-I/O_8$ for x 18, $I/O_0-I/O_7$ for x 16) of the memory array. For read operations both the LB and OE signals must be asserted to drive output data on the lower byte of the data pins. |

| UBL                                   | UB <sub>R</sub>                       | <b>Upper Byte Select Input.</b> Same function as $\overline{LB}$ , but to the upper byte ( $I/O_{8/9L}$ - $I/O_{15/17L}$ ).                                                                                                                                                                                     |

| OEL                                   | OE <sub>R</sub>                       | Output Enable Input. This signal must be asserted LOW to enable the I/O data pins during read operations.                                                                                                                                                                                                       |

| R/WL                                  | R/W <sub>R</sub>                      | <b>Read/Write Enable Input</b> . This signal is asserted LOW to write to the dual port memory array. For read operations, assert this pin HIGH.                                                                                                                                                                 |

| FT/PIPE <sub>L</sub>                  | FT/PIPE <sub>R</sub>                  | Flow Through/Pipelined Select Input. For flow through mode operation, assert this pin LOW. For pipelined mode operation, assert this pin HIGH.                                                                                                                                                                  |

| GND                                   | ·                                     | Ground Input.                                                                                                                                                                                                                                                                                                   |

| NC                                    |                                       | No Connect.                                                                                                                                                                                                                                                                                                     |

| V <sub>CC</sub>                       |                                       | Power Input.                                                                                                                                                                                                                                                                                                    |

## **Functional Description**

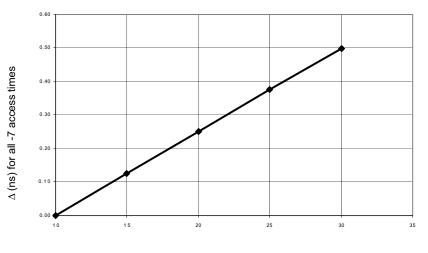

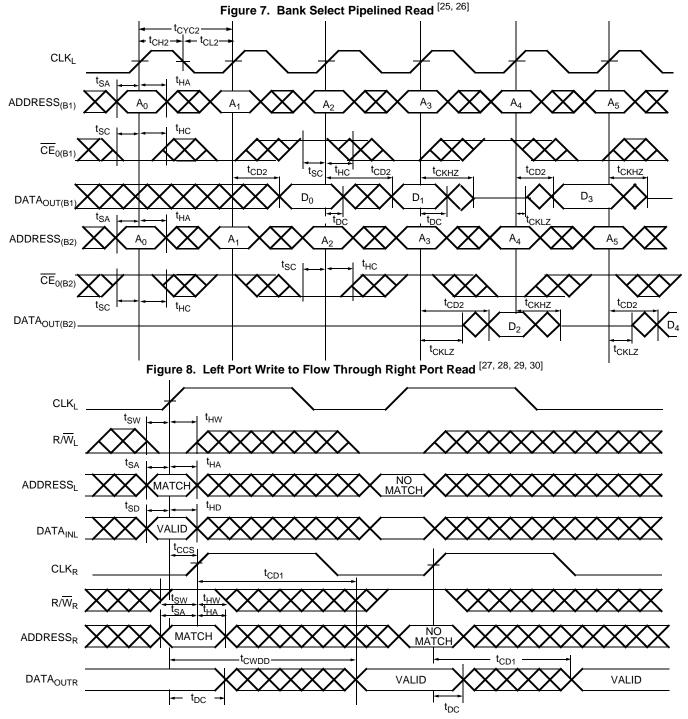

The CY7C09269V/79V/89V and CY7C09369V/89V are high speed 3.3 V synchronous CMOS 16 K, 32 K, and 64 K × 16 and 16 K and 64 K × 18 dual-port static RAMs. Two ports are provided, permitting independent, simultaneous access for reads and writes to any location in memory <sup>[11]</sup>. Registers on control, address, and data lines allow for minimal setup and hold times. In pipelined output mode, data is registered for decreased cycle time and clock to data valid  $t_{CD2} = 7.5$  ns <sup>[12]</sup> (pipelined). Flow through mode can also be used to bypass the pipelined output register to eliminate access latency. In flow through mode, data is available  $t_{CD1} = 18$  ns after the address is clocked into the device. Pipelined output or flow through mode is selected through the FT/Pipe pin.

Each port contains a burst counter on the input address register. The internal write pulse width is independent of the LOW to HIGH transition of the clock signal. The internal write pulse is self timed to allow the shortest possible cycle times. A HIGH on  $\overline{CE}_0$  or LOW on  $CE_1$  for one clock cycle powers down the internal circuitry to reduce the static power consumption. The use of multiple Chip Enables enables easier banking of multiple chips for depth expansion <u>configurations</u>. In the pipelined mode, one cycle is required with  $\overline{CE}_0$  LOW and  $\overline{CE}_1$  HIGH to reactivate the outputs.

Counter enable inputs are provided to stall the operation of the address input and use the internal address generated by the internal counter for fast interleaved memory applications. A <u>port's</u> burst counter is loaded with th<u>e port's</u> Address Strobe (ADS). When the port's Count Enable (CNTEN) is asserted, the address counter increments on each LOW to HIGH transition of that port's clock signal. This reads/writes <u>one word</u> from or into each successive address location, until CNTEN is deasserted. The counter can address th<u>e entire memory</u> array and loop back to the start. Counter Reset (CNTRST) is used to reset the burst counter.

All parts are available in 100-pin Thin Quad Plastic Flatpack (TQFP) packages.

Notes

11. When writing simultaneously to the same location, the final value cannot be guaranteed.

12. See Figure 4 on page 8 for Load Conditions.

## **Maximum Ratings**

Exceeding maximum ratings <sup>[13]</sup> may impair the useful life of the device. These user guidelines are not tested.

| Storage Temperature65 °C to +                                  | -150 °C |

|----------------------------------------------------------------|---------|

| Ambient Temperature with<br>Power Applied55 °C to +            | -125 °C |

| Supply Voltage to Ground Potential0.5 V to                     | +4.6 V  |

| DC Voltage Applied to Outputs in High Z State0.5 V to $V_{CC}$ | + 0.5 V |

# **Electrical Characteristics**

Over the Operating Range

| DC Input Voltage                                           | –0.5 V to V <sub>CC</sub> + 0.5 V |

|------------------------------------------------------------|-----------------------------------|

| Output Current into Outputs (LOW) .                        | 20 mA                             |

| Static Discharge Voltage<br>(per MIL-STD-883, Method 3015) | > 1100 V                          |

| Latch up Current                                           | > 200 mA                          |

## **Operating Range**

| Range      | Ambient Temperature | V <sub>CC</sub>    |

|------------|---------------------|--------------------|

| Commercial | 0 ℃ to +70 ℃        | $3.3~V~\pm 300~mV$ |

| Industrial | –40 ℃ to +85 ℃      | $3.3~V~\pm 300~mV$ |

| Demonster        | Description                                                                                                                                                     | CY7C09269V/79V/89V<br>CY7C09369V/89V |     |                           |     |     |     |     |     |     |     |      |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----|---------------------------|-----|-----|-----|-----|-----|-----|-----|------|

| Parameter        | Description                                                                                                                                                     |                                      |     | <b>-7</b> <sup>[14]</sup> |     |     | -9  |     |     | -12 |     | Unit |

|                  |                                                                                                                                                                 |                                      | Min | Тур                       | Max | Min | Тур | Max | Min | Тур | Max |      |

| V <sub>OH</sub>  | Output HIGH Voltage ( $V_{CC}$ = Min, $I_{OH}$                                                                                                                  | = -4.0 mA)                           | 2.4 | -                         | -   | 2.4 | -   | -   | 2.4 | -   | -   | V    |

| V <sub>OL</sub>  | Output LOW Voltage ( $V_{CC}$ = Min, I <sub>OH</sub>                                                                                                            | = +4.0 mA)                           | _   | -                         | 0.4 | -   | -   | 0.4 | -   | -   | 0.4 | V    |

| V <sub>IH</sub>  | Input HIGH Voltage                                                                                                                                              |                                      | 2.0 | _                         | -   | 2.0 | _   | -   | 2.0 | _   | -   | V    |

| V <sub>IL</sub>  | Input LOW Voltage                                                                                                                                               |                                      | _   | _                         | 0.8 | -   | _   | 0.8 | -   | _   | 0.8 | V    |

| I <sub>OZ</sub>  | Output Leakage Current                                                                                                                                          | -10                                  | _   | 10                        | -10 | _   | 10  | -10 | _   | 10  | μΑ  |      |

| I <sub>CC</sub>  | Operating Current                                                                                                                                               | Commercial                           | _   | 155                       | 275 | -   | 135 | 230 | -   | 115 | 180 | mA   |

|                  | (V <sub>CC</sub> = Max, I <sub>OUT</sub> = 0 mA)<br>Outputs Disabled                                                                                            | Industrial                           | -   | 275                       | 390 | -   | 185 | 300 | -   | -   | -   | mA   |

| I <sub>SB1</sub> | Standby Current                                                                                                                                                 | Commercial                           | -   | 25                        | 85  | -   | 20  | 75  | -   | 20  | 70  | mA   |

|                  | $\frac{(Both Ports TTL Level)}{CE_L \& CE_R \ge V_{IH}, f = f_{MAX}}$                                                                                           | Industrial                           | -   | 85                        | 120 | -   | 35  | 85  | -   | -   | -   | mA   |

| I <sub>SB2</sub> | Standby Current                                                                                                                                                 | Commercial                           | -   | 105                       | 165 | -   | 95  | 155 | -   | 85  | 140 | mA   |

|                  | $\frac{(One Port TTL Level)}{CE_L   CE_R \ge V_{IH}, f = f_{MAX}}$                                                                                              | Industrial                           | -   | 165                       | 210 | Ι   | 105 | 165 | Ι   | -   | -   | mA   |

| I <sub>SB3</sub> | Standby Current                                                                                                                                                 | Commercial                           | -   | 10                        | 250 | -   | 10  | 250 | -   | 10  | 250 | μΑ   |

|                  | $\label{eq:both_constraints} \begin{array}{l} \underline{(Both\ Ports\ CMOS\ Level)}\ ^{[15]}\\ \hline CE_L\ \&\ CE_R \geq V_{CC} - 0.2\ V,\ f = 0 \end{array}$ | Industrial                           | -   | 10                        | 250 | Ι   | 10  | 250 | Ι   | -   | -   | μΑ   |

| I <sub>SB4</sub> | Standby Current                                                                                                                                                 | Commercial                           | -   | 95                        | 125 | 1   | 85  | 115 | Ι   | 75  | 100 | mA   |

|                  | $\label{eq:constraint} \frac{(One \ Port \ CMOS \ Level)^{[15]}}{CE_L \   \ CE_R \ge V_{IH}, \ f = f_{MAX}}$                                                    | Industrial                           | -   | 125                       | 170 | -   | 95  | 125 | -   | -   | -   | mA   |

## Capacitance

| Parameter <sup>[16]</sup> | Description        | Test Conditions                                                  | Мах | Unit |

|---------------------------|--------------------|------------------------------------------------------------------|-----|------|

| C <sub>IN</sub>           | Input Capacitance  | $T_A = 25 \text{ °C}, f = 1 \text{ MHz}, V_{CC} = 3.3 \text{ V}$ | 10  | pF   |

| C <sub>OUT</sub>          | Output Capacitance |                                                                  | 10  | pF   |

#### Notes

13. The voltage on any input or I/O pin can not exceed the power pin during power up.

14. See Figure 4 on page 8 for Load Conditions.

15.  $\overline{CE}_L$  and  $\overline{CE}_R$  are internal signals. To select either the left or right port, both  $\overline{CE}_0$  and  $CE_1$  must be asserted to their active states ( $\overline{CE}_0 \le V_{IL}$  and  $CE_1 \ge V_{IH}$ ).

16. Tested initially and after any design or process changes that may affect these parameters.

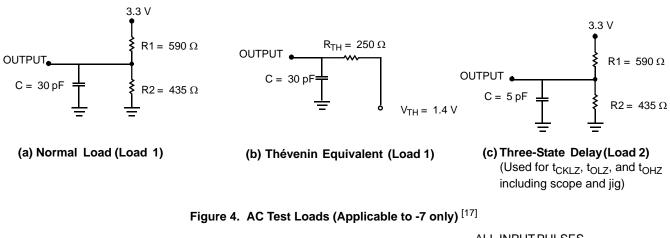

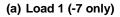

## **AC Test Loads and Waveforms**

Figure 3. AC Test Loads and Waveforms

Capacitance (pF)

(b) Load Derating Curve

# **Switching Characteristics**

#### Over the Operating Range

| Parameter                             | Description                              | CY7C09269V/79V/89V<br>CY7C09369V/89V<br>-7 <sup>[18]</sup> -9 -12 |     |     |     |     |     |      |

|---------------------------------------|------------------------------------------|-------------------------------------------------------------------|-----|-----|-----|-----|-----|------|

| Parameter                             | Description                              |                                                                   |     |     | 9   |     | 12  | Unit |

|                                       |                                          | Min                                                               | Max | Min | Max | Min | Max |      |

| f <sub>MAX1</sub>                     | f <sub>Max</sub> Flow Through            | -                                                                 | 45  | -   | 40  | -   | 33  | MHz  |

| f <sub>MAX2</sub>                     | f <sub>Max</sub> Pipelined               | -                                                                 | 83  | -   | 67  | -   | 50  | MHz  |

| t <sub>CYC1</sub>                     | Clock Cycle Time - Flow Through          | 22                                                                | -   | 25  | -   | 30  | -   | ns   |

| t <sub>CYC2</sub>                     | Clock Cycle Time - Pipelined             | 12                                                                | -   | 15  | -   | 20  | -   | ns   |

| t <sub>CH1</sub>                      | Clock HIGH Time - Flow Through           | 7.5                                                               | -   | 12  | -   | 12  | -   | ns   |

| t <sub>CL1</sub>                      | Clock LOW Time - Flow Through            | 7.5                                                               | -   | 12  | -   | 12  | -   | ns   |

| t <sub>CH2</sub>                      | Clock HIGH Time - Pipelined              | 5                                                                 | -   | 6   | -   | 8   | -   | ns   |

| t <sub>CL2</sub>                      | Clock LOW Time - Pipelined               | 5                                                                 | -   | 6   | -   | 8   | _   | ns   |

| t <sub>R</sub>                        | Clock Rise Time                          | -                                                                 | 3   | -   | 3   | -   | 3   | ns   |

| t <sub>F</sub>                        | Clock Fall Time                          | -                                                                 | 3   | -   | 3   | -   | 3   | ns   |

| t <sub>SA</sub>                       | Address Set-Up Time                      | 4                                                                 | -   | 4   | -   | 4   | -   | ns   |

| t <sub>HA</sub>                       | Address Hold Time                        | 0                                                                 | -   | 1   | -   | 1   | -   | ns   |

| t <sub>SC</sub>                       | Chip Enable Setup Time                   | 4                                                                 | -   | 4   | -   | 4   | -   | ns   |

| t <sub>HC</sub>                       | Chip Enable Hold Time                    | 0                                                                 | -   | 1   | -   | 1   | _   | ns   |

| t <sub>SW</sub>                       | R/W Set-Up Time                          | 4                                                                 | -   | 4   | -   | 4   | _   | ns   |

| t <sub>HW</sub>                       | R/W Hold Time                            | 0                                                                 | -   | 1   | -   | 1   | -   | ns   |

| t <sub>SD</sub>                       | Input Data Setup Time                    | 4                                                                 | -   | 4   | -   | 4   | -   | ns   |

| t <sub>HD</sub>                       | Input Data Hold Time                     | 0                                                                 | -   | 1   | -   | 1   | -   | ns   |

| t <sub>SAD</sub>                      | ADS Set-Up Time                          | 4                                                                 | -   | 4   | -   | 4   | -   | ns   |

| t <sub>HAD</sub>                      | ADS Hold Time                            | 0                                                                 | -   | 1   | -   | 1   | _   | ns   |

| t <sub>SCN</sub>                      | CNTEN Setup Time                         | 4.5                                                               | -   | 5   | -   | 5   | _   | ns   |

| t <sub>HCN</sub>                      | CNTEN Hold Time                          | 0                                                                 | -   | 1   | -   | 1   | _   | ns   |

| t <sub>SRST</sub>                     | CNTRST Setup Time                        | 4                                                                 | -   | 4   | -   | 4   | _   | ns   |

| t <sub>HRST</sub>                     | CNTRST Hold Time                         | 0                                                                 | -   | 1   | -   | 1   | _   | ns   |

| t <sub>OE</sub>                       | Output Enable to Data Valid              | -                                                                 | 9   | _   | 10  | _   | 12  | ns   |

| t <sub>OLZ</sub> <sup>[19, 20]</sup>  | OE to Low Z                              | 2                                                                 | _   | 2   | _   | 2   | _   | ns   |

| t <sub>OHZ</sub> <sup>[19, 20]</sup>  | OE to High Z                             | 1                                                                 | 7   | 1   | 7   | 1   | 7   | ns   |

| t <sub>CD1</sub>                      | Clock to Data Valid - Flow Through       | -                                                                 | 18  | -   | 20  | _   | 25  | ns   |

| t <sub>CD2</sub>                      | Clock to Data Valid - Pipelined          | _                                                                 | 7.5 | _   | 9   | _   | 12  | ns   |

| t <sub>DC</sub>                       | Data Output Hold After Clock HIGH        | 2                                                                 | _   | 2   | _   | 2   | _   | ns   |

| t <sub>СКНZ</sub> <sup>[19, 20]</sup> | Clock HIGH to Output High Z              | 2                                                                 | 9   | 2   | 9   | 2   | 9   | ns   |

| t <sub>CKLZ</sub> <sup>[19, 20]</sup> | Clock HIGH to Output Low Z               | 2                                                                 | -   | 2   | -   | 2   | _   | ns   |

| Port to Port                          | Delays                                   | 1                                                                 | I   | I   | I   | 1   | 1   | 1    |

| t <sub>CWDD</sub>                     | Write Port Clock HIGH to Read Data Delay | -                                                                 | 35  | -   | 40  | -   | 40  | ns   |

| t <sub>CCS</sub>                      | Clock to Clock Setup Time                | -                                                                 | 10  | -   | 15  | _   | 15  | ns   |

Notes18. See Figure 4 on page 8 for Load Conditions.19. Test conditions used are Load 2.20. This parameter is guaranteed by design, but it is not production tested.

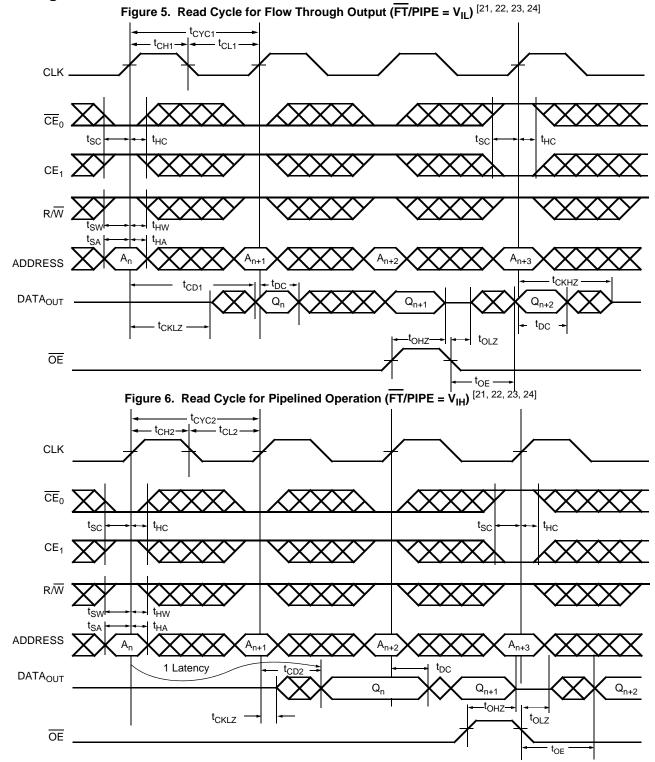

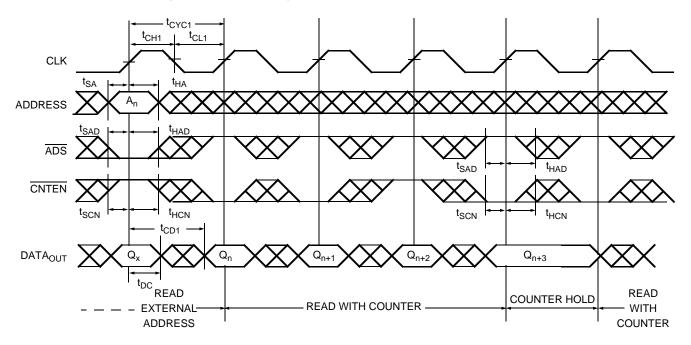

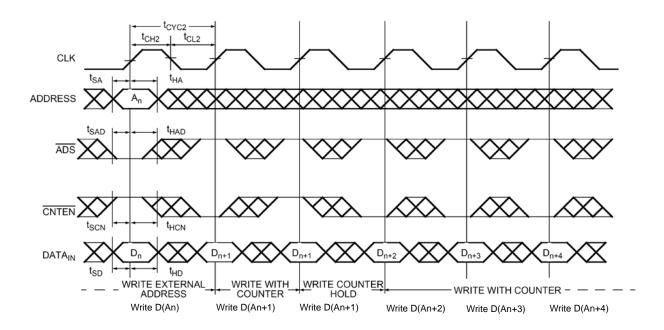

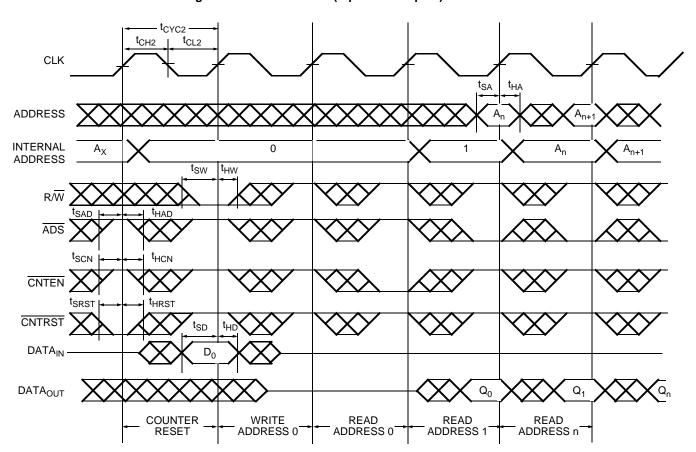

# **Switching Waveforms**

#### Notes

Notes 21.  $\overrightarrow{DE}$  is asynchronously controlled; all other inputs are synchronous to the rising clock edge. 22.  $\overrightarrow{ADS} = V_{IL}$ ,  $\overrightarrow{CNTEN}$  and  $\overrightarrow{CNTRST} = V_{IH}$ . 23. The output is disabled (high impedance state) by  $\overrightarrow{CE}_0 = V_{IH}$  or  $\overrightarrow{CE}_1 = V_{IL}$  following the next rising edge of the clock. 24. Addresses do not have to be accessed sequentially since  $\overrightarrow{ADS} = V_{IL}$  constantly loads the address on the rising edge of the CLK. Numbers are for reference only.

#### Notes

Notes 25. In this depth expansion example, B1 represents Bank #1 and B2 is Bank #2; Each Bank consists of one Cypress dual-port device from this datasheet. <u>ADDRESS<sub>(B1)</sub> = ADDRESS<sub>(B2)</sub>.</u> 26. UB, LB, OE and ADS = V<sub>IL</sub>; CE<sub>1(B1)</sub>, CE<sub>1(B2)</sub>, RW, CNTEN, and CNTRST = V<sub>IH</sub>. 27. The same waveforms apply for a right port write to flow through left port read. 28. <u>CE<sub>0</sub></u>, UB, LB, and ADS = V<sub>IL</sub>; CE<sub>1</sub>, CNTEN, and CNTRST = V<sub>IH</sub>. 29. OE = V<sub>IL</sub> for the Right Port, which is being read from. OE = V<sub>IH</sub> for the Left Port, which is being written to. 30. It toos < maximum specified then data from right port PAD is not valid until the maximum specified for toward.

30. It  $t_{CCS} \le maximum$  specified, then data from right port READ is not valid until the maximum specified for  $t_{CWDD}$ . If  $t_{CCS}$ -maximum specified, then data is not valid until  $t_{CCS} \le t_{CD1}$ .  $t_{CWDD}$  does not apply in this case.

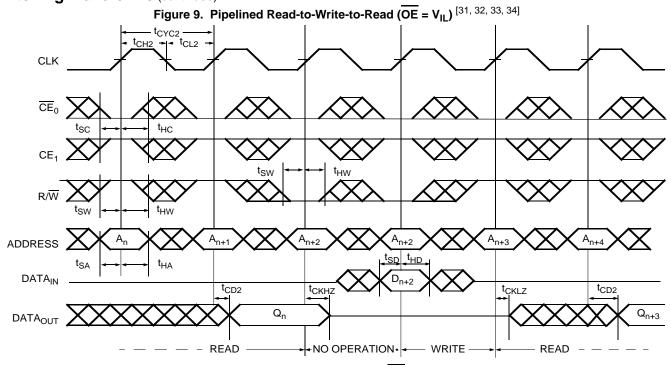

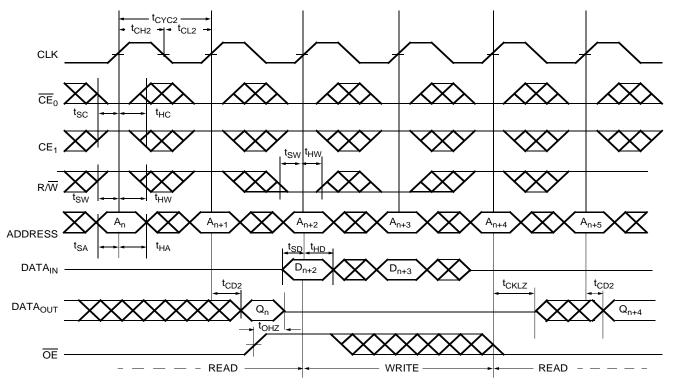

Figure 10. Pipelined Read-to-Write-to-Read (OE Controlled) <sup>[31, 32, 33, 34]</sup>

#### Notes

31. Addresses do not have to be accessed sequentially since  $\overline{ADS} = V_{IL}$  constantly loads the address on the rising edge of the CLK. Numbers are for reference only. 32. <u>Output state (High, LOW, or high impedance) is determined by the previous cycle control signals.</u>

33.  $\overline{CE}_0$  and  $\overline{ADS} = V_{IL}$ ;  $CE_1$ ,  $\overline{CNTEN}$ , and  $\overline{CNTRST} = V_{IH}$ .

34. During "No Operation", data in memory at the selected address may be corrupted and must be rewritten to ensure data integrity.

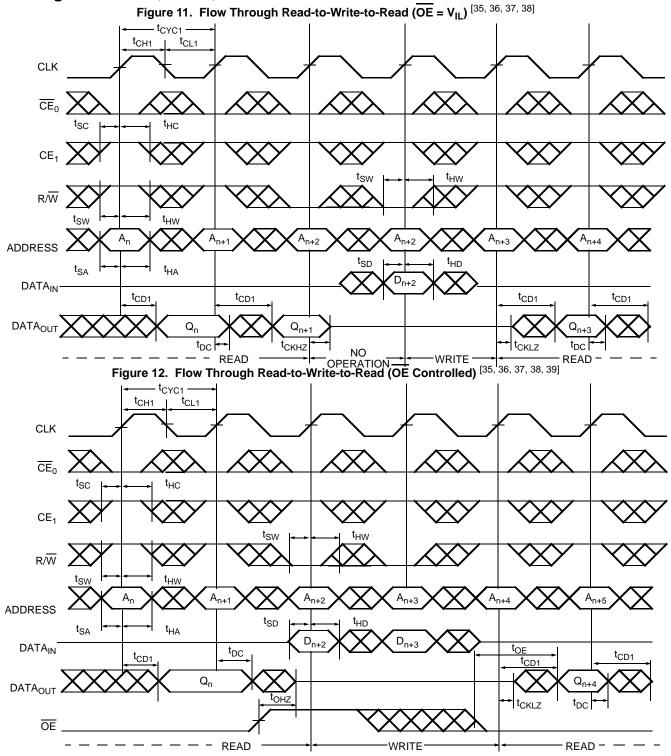

#### Notes

35.  $\overline{\text{ADS}} = V_{\text{IL}}$ ,  $\overline{\text{CNTEN}}$  and  $\overline{\text{CNTRST}} = V_{\text{IH}}$ .

36. Addresses do not have to be accessed sequentially since  $\overline{ADS} = V_{IL}$  constantly loads the address on the rising edge of the CLK. Numbers are for reference only. 37.  $\overline{CE}_0$  and  $\overline{ADS} = V_{IL}$ ;  $\overline{CE}_1$ ,  $\overline{CNTEN}$ , and  $\overline{CNTRST} = V_{IH}$ .

38. During "No Operation", data in memory at the selected address may be corrupted and must be rewritten to ensure data integrity.

39. Output state (High, LOW, or high impedance) is determined by the previous cycle control signals.

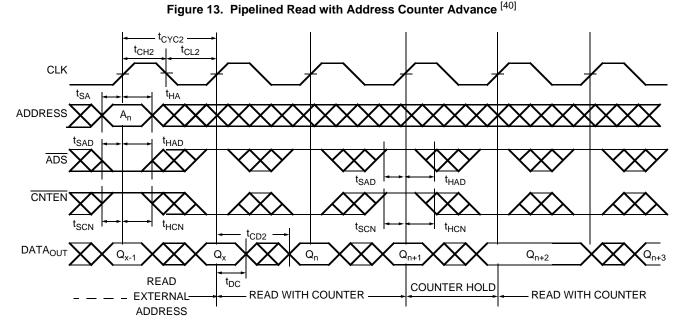

Figure 14. Flow Through Read with Address Counter Advance <sup>[40]</sup>

Note 40.  $\overline{CE}_0$  and  $\overline{OE} = V_{IL}$ ;  $CE_1$ , R/W and  $\overline{CNTRST} = V_{IH}$ .

Figure 15. Write with Address Counter Advance (Flow Through or Pipelined Outputs) <sup>[41, 42]</sup>

Notes 41.  $\overline{CE}_0$ ,  $\overline{UB}$ ,  $\overline{LB}$ , and  $\overline{R/W} = V_{IL}$ ;  $\overline{CE}_1$  and  $\overline{CNTRST} = V_{IH}$ . 42. The "Internal Address" is equal to the "External Address" when  $\overline{ADS} = V_{IL}$  and equals the counter output when  $\overline{ADS} = V_{IH}$ .

Figure 16. Counter Reset (Pipelined Outputs) [43, 44, 45, 46]

Notes

43. Addresses do not have to be accessed sequentially since ADS = V<sub>IL</sub> constantly loads the address on the rising edge of the CLK. Numbers are for reference only.

44. <u>Output state (High, LOW, or high impedance)</u> is determined by the previous cycle control signals. 45.  $\overline{CE}_0$ ,  $\overline{UB}$ , and  $\overline{LB} = V_{IL}$ ;  $\overline{CE}_1 = V_{IH}$ .

<sup>46.</sup> No dead cycle exists during counter reset. A READ or WRITE cycle may be coincidental with the counter reset.

## **Read/Write and Enable Operation**

The Read/Write and Enable Operation is described as follows. <sup>[47, 48, 49]</sup>

|    |     | Inputs |                 |     | Outputs                            | Operation                  |

|----|-----|--------|-----------------|-----|------------------------------------|----------------------------|

| OE | CLK |        | CE <sub>1</sub> | R/W | I/O <sub>0</sub> I/O <sub>17</sub> | Operation                  |

| Х  |     | Н      | Х               | Х   | High Z                             | Deselected <sup>[50]</sup> |

| Х  |     | Х      | L               | Х   | High Z                             | Deselected <sup>[50]</sup> |

| Х  |     | L      | Н               | L   | D <sub>IN</sub>                    | Write                      |

| L  |     | L      | Н               | Н   | D <sub>OUT</sub>                   | Read <sup>[51]</sup>       |

| Н  | Х   | L      | Н               | Х   | High Z                             | Outputs Disabled           |

## **Address Counter Control Operation**

The Address Counter Control Operation is described as follows. <sup>[47, 52, 53, 54]</sup>

| Address        | Previous<br>Address | CLK | ADS | CNTEN | CNTRST | I/O                   | Mode      | Operation                                     |

|----------------|---------------------|-----|-----|-------|--------|-----------------------|-----------|-----------------------------------------------|

| х              | х                   |     | Х   | Х     | L      | D <sub>out(0)</sub>   | Reset     | Counter Reset to Address 0                    |

| A <sub>n</sub> | Х                   |     | L   | Х     | Н      | D <sub>out(n)</sub>   | Load      | Address Load into Counter                     |

| Х              | A <sub>n</sub>      | 4   | H   | Н     | H      | D <sub>out(n)</sub>   | Hold      | External Address Blocked — Counter Disabled   |

| Х              | A <sub>n</sub>      | 5   | H   | L     | H      | D <sub>out(n+1)</sub> | Increment | Counter Enabled — Internal Address Generation |

- 49.  $\overline{\text{OE}}$  is an asynchronous input signal. 50. When  $\overline{\text{CE}}$  changes state in the pipelined mode, deselection and read happen in the following clock cycle. 51.  $\overline{\text{ADS}} = V_{|L|}$ ,  $\overline{\text{CNTEN}}$  and  $\overline{\text{CNTRST}} = V_{|H|}$ . 52.  $\overline{\text{CE}}_0$  and  $\overline{\text{OE}} = V_{|L|}$ ;  $\overline{\text{CE}}_1$  and  $\overline{\text{RW}} = V_{|H|}$ .

- 53. Data shown for flow through mode; pipelined mode output is delayed by one cycle. 54. Counter operation is independent of  $\overline{CE}_0$  and  $\overline{CE}_1$ .

## **Ordering Information**

#### 16 K × 16 3.3 V Synchronous Dual-Port SRAM

| Speed<br>(ns)       | Ordering Code    | Package<br>Diagram | Package Type           | Operating<br>Range |

|---------------------|------------------|--------------------|------------------------|--------------------|

| 7.5 <sup>[55]</sup> | CY7C09269V-7AXC  | 51-85048           | 100-pin TQFP (Pb-free) | Commercial         |

| 9                   | CY7C09269V-9AXC  | 51-85048           | 100-pin TQFP (Pb-free) | Commercial         |

| 12                  | CY7C09269V-12AXC | 51-85048           | 100-pin TQFP (Pb-free) | Commercial         |

#### 32 K × 16 3.3 V Synchronous Dual-Port SRAM

| Speed<br>(ns)       | Ordering Code    | Package<br>Diagram | Package Type           | Operating<br>Range |

|---------------------|------------------|--------------------|------------------------|--------------------|

| 7.5 <sup>[55]</sup> | CY7C09279V-7AXC  | 51-85048           | 100-pin TQFP (Pb-free) | Commercial         |

| 12                  | CY7C09279V-12AXC | 51-85048           | 100-pin TQFP (Pb-free) | Commercial         |

#### 64 K × 16 3.3 V Synchronous Dual-Port SRAM

| Speed<br>(ns) | Ordering Code    | Package<br>Diagram | Package Type           | Operating<br>Range |

|---------------|------------------|--------------------|------------------------|--------------------|

| 9             | CY7C09289V-9AXC  | 51-85048           | 100-pin TQFP (Pb-free) | Commercial         |

|               | CY7C09289V-9AXI  | 51-85048           | 100-pin TQFP (Pb-free) | Industrial         |

| 12            | CY7C09289V-12AXC | 51-85048           | 100-pin TQFP (Pb-free) | Commercial         |

#### 16 K × 18 3.3 V Synchronous Dual-Port SRAM

| Speed<br>(ns) | Ordering Code    | Package<br>Diagram | Package Type           | Operating<br>Range |

|---------------|------------------|--------------------|------------------------|--------------------|

| 9             | CY7C09369V-9AXC  | 51-85048           | 100-pin TQFP (Pb-free) | Commercial         |

| 12            | CY7C09369V-12AXC | 51-85048           | 100-pin TQFP (Pb-free) | Commercial         |

#### 64 K × 18 3.3 V Synchronous Dual-Port SRAM

| Speed<br>(ns)       | Ordering Code Package Diagram |          | Package Type           | Operating<br>Range |

|---------------------|-------------------------------|----------|------------------------|--------------------|

| 7.5 <sup>[55]</sup> | CY7C09389V-7AXC               | 51-85048 | 100-pin TQFP (Pb-free) | Commercial         |

| 9                   | CY7C09389V-9AI                | 51-85048 | 100-pin TQFP           | Industrial         |

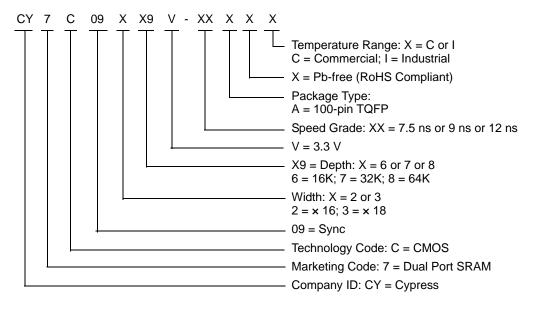

#### **Ordering Code Definitions**

## Package Diagrams

51-85048 \*G

# Acronyms

| Acronym | Description                             |

|---------|-----------------------------------------|

| CE      | chip enable                             |

| CMOS    | complementary metal oxide semiconductor |

| I/O     | input/output                            |

| OE      | output enable                           |

| SRAM    | static random access memory             |

| TQFP    | thin quad flat pack                     |

| TTL     | transistor-transistor logic             |

## **Document Conventions**

#### **Units of Measure**

| Symbol | Unit of Measure |

|--------|-----------------|

| C      | degree Celsius  |

| MHz    | megahertz       |

| μA     | microampere     |

| mA     | milliampere     |

| mm     | millimeter      |

| mV     | millivolt       |

| ns     | nanosecond      |

| Ω      | ohm             |

| %      | percent         |

| pF     | picofarad       |

| V      | volt            |

# **Document History Page**

| Revision | ECN     | Submission<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|---------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **       | 110215  | 12/18/01           | SZV                | Change from Spec number: 38-00668 to 38-06056                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| *A       | 122306  | 12/27/02           | RBI                | Power up requirements added to Maximum Ratings Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| *B       | 344354  | See ECN            | PCX                | Added Pb-Free Part Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| *C       | 2678221 | 03/25/2009         | VKN /<br>AESA      | Added CY7C09379V-12AXCT part.<br>Updated 51-85048 to *C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| *D       | 2896210 | 03/22/2010         | RAME               | Updated Ordering Information.<br>Updated Package Diagrams.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| *E       | 3111417 | 12/15/2010         | ADMU               | Updated Ordering Information.<br>Added Ordering Code Definitions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| *F       | 3124048 | 12/30/2010         | ADMU               | No technical updates.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| *G       | 3352110 | 08/23/2011         | ADMU               | Updated Features (Removed CY7C09379V information and also removed -6<br>speed bin information).<br>Updated Pin Configurations (Removed CY7C09379V information).<br>Updated Selection Guide (Removed CY7C09379V information and also<br>removed -6 speed bin information).<br>Updated Functional Description (Removed CY7C09379V information).<br>Updated Electrical Characteristics (Removed CY7C09379V information).<br>Updated Electrical Characteristics (Removed CY7C09379V information and<br>also removed -6 speed bin information).<br>Updated AC Test Loads and Waveforms (Removed -6 speed bin information)<br>Updated Switching Characteristics (Removed CY7C09379V information and<br>also removed -6 speed bin information).<br>Updated Ordering Information (Removed part CY7C09279V-7AC).<br>Updated Package Diagrams.<br>Added Acronyms and Units of Measure.<br>Updated in new template. |

| *H       | 3402091 | 10/12/2011         | ADMU               | Updated Ordering Information (Removed pruned part CY7C09289V-9AI).<br>Updated Package Diagrams.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| *        | 3680923 | 08/01/2012         | ADMU /<br>SMCH     | Updated Pin Configurations (Updated Figure 2).<br>Updated Switching Characteristics (Changed name of parameter from $t_{CKZ}$ to $t_{CKHZ}$ , changed name of parameter from $t_{CKZ}$ to $t_{CKLZ}$ in the next corresponding row).<br>Updated Switching Waveforms (Updated Figure 15).<br>Updated Address Counter Control Operation.<br>Updated Ordering Information (Removed pruned part CY7C09289V-9AC).<br>Updated Package Diagrams (spec 51-85048 (Changed revision from *E to *G)).                                                                                                                                                                                                                                                                                                                                                                                                               |

## Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at cypress.com/sales.

#### Products

| Automotive               | cypress.com/go/automotive |

|--------------------------|---------------------------|

| Clocks & Buffers         | cypress.com/go/clocks     |

| Interface                | cypress.com/go/interface  |

| Lighting & Power Control | cypress.com/go/powerpsoc  |

|                          | cypress.com/go/plc        |

| Memory                   | cypress.com/go/memory     |

| Optical & Image Sensing  | cypress.com/go/image      |

| PSoC                     | cypress.com/go/psoc       |

| Touch Sensing            | cypress.com/go/touch      |

| USB Controllers          | cypress.com/go/USB        |

| Wireless/RF              | cypress.com/go/wireless   |

#### **PSoC Solutions**

psoc.cypress.com/solutions PSoC 1 | PSoC 3 | PSoC 5

© Cypress Semiconductor Corporation, 2001-2012. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

Document Number: 38-06056 Rev. \*I

Revised August 1, 2012

All products and company names mentioned in this document may be the trademarks of their respective holders.