### Freescale Semiconductor Advance Information

Document Number: MC34709 Rev. 2.0, 10/2012

# Power Management Integrated Circuit (PMIC) for i.MX50/53 Families

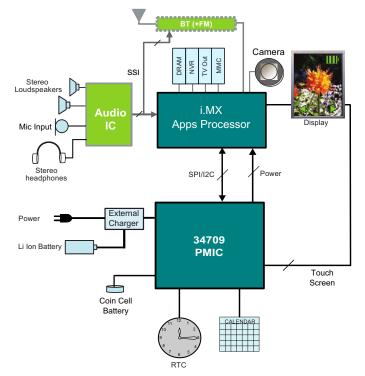

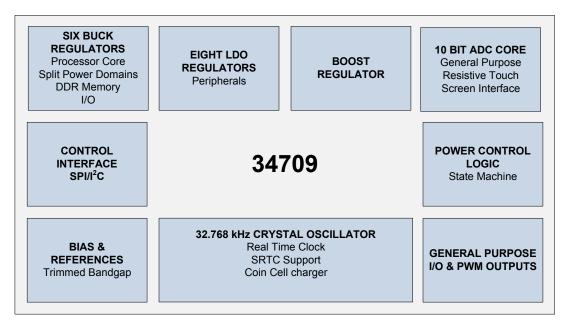

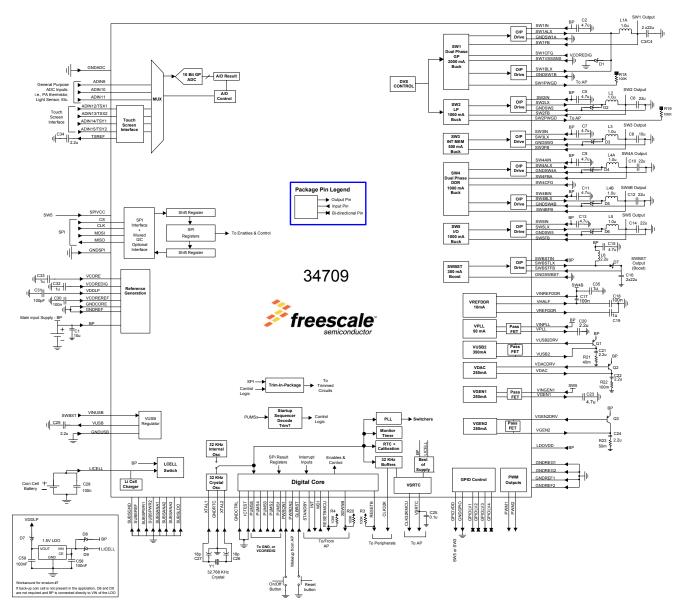

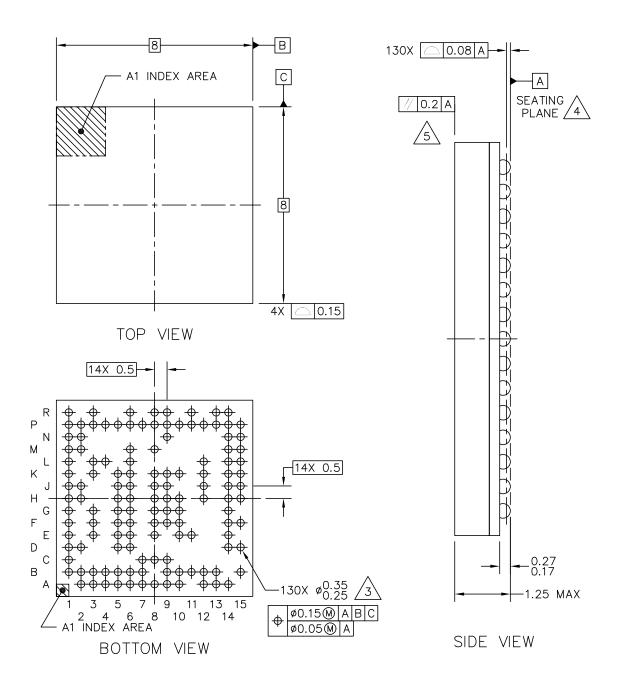

The 34709 is the Power Management Integrated Circuit (PMIC) designed primarily for use with the Freescale i.MX50 and i.MX53 families. It offers a low cost solution targeting embedded applications that do not require a battery charger. However, it can be easily combined with an external charger, allowing flexibility for either single or multi-cell Li-Ion battery configurations. It supports both consumer and industrial applications with a single 130-pin 8x8 MAPBGA 0.5 mm pitch package that is easily routable in low cost board designs.

#### Features

- Six multi-mode buck regulators for direct supply of the processor core, memory, and peripherals.

- Boost regulator for USB PHY domain on i.MX processors.

- Eight LDO regulators with internal and external pass devices for thermal budget optimization and DDR memory voltage reference

- 10-bit ADC for monitoring battery and other inputs

- Real time clock and crystal oscillator circuitry with a coin cell backup/charger

- SPI/I<sup>2</sup>C bus for control and register interface

- · Four general purpose low-voltage I/Os with interrupt capability

- Two PWM outputs

Human Machine Interfaces (HMI)

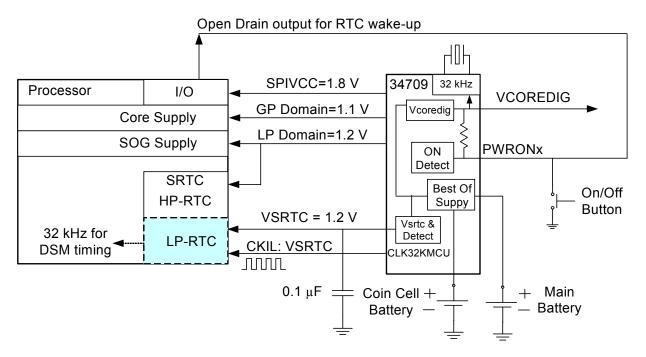

Figure 1. Simplified Application Diagram

\* This document contains certain information on a new product. Specifications and information herein are subject to change without notice.

© Freescale Semiconductor, Inc., 2012. All rights reserved.

# **Table of Contents**

| 1        | Orde  | rable Parts   |                                        | 4 |

|----------|-------|---------------|----------------------------------------|---|

| 2        | Part  | dentification | n                                      | 5 |

|          | 2.1   | Description   | n                                      | 5 |

|          | 2.2   | Format and    | d Examples                             | 5 |

|          | 2.3   |               | · · · · · · · · · · · · · · · · · · ·  |   |

| 3        | Inter |               | agram                                  |   |

|          | 3     |               | ock Diagram                            |   |

| 4        | Pin C |               | ······································ |   |

|          | 4.1   |               |                                        |   |

|          | 4.2   |               | ions                                   |   |

| 5        | Gene  |               | Characteristics                        |   |

|          | 5.1   |               | Ratings                                |   |

|          | 5.2   |               | haracteristics                         |   |

|          |       |               | ower Dissipation                       |   |

|          | 5.3   |               | Characteristics                        |   |

|          | 0.0   |               | ieneral PMIC Specifications            |   |

|          |       |               | surrent Consumption                    |   |

| 6        | Gene  |               | tion                                   |   |

| Č        | 6.1   |               |                                        |   |

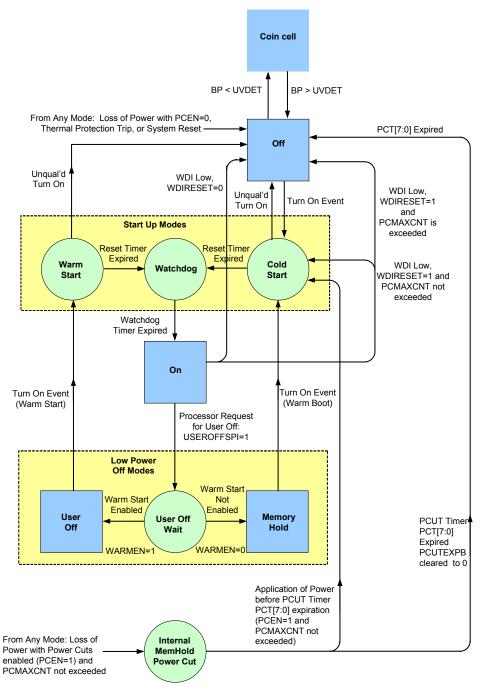

|          | 6.2   |               | jram                                   |   |

|          | 7     | •             | Block Description                      |   |

| 7        |       |               | Description                            |   |

| <b>'</b> | 7.1   |               | equirements                            |   |

|          | 7.2   |               | References Block                       |   |

|          | 7.3   |               | ind Oscillators                        |   |

|          | 1.5   | -             | lock Generation                        |   |

|          |       |               | RTC Support                            |   |

|          |       |               | oin Cell Battery Backup                |   |

|          | 7.4   |               | lanagement                             |   |

|          | 1.4   |               | iontrol                                |   |

|          |       |               | nterrupt Bit Summary                   |   |

|          | 7.5   |               | neration                               |   |

|          | 1.0   |               | ower Tree                              |   |

|          |       |               | lodes of Operation                     |   |

|          |       |               | ower Control Logic                     |   |

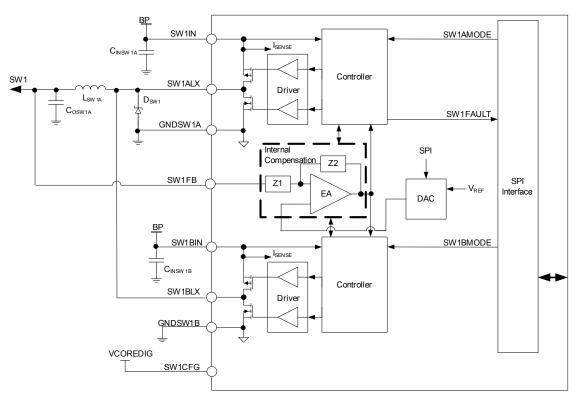

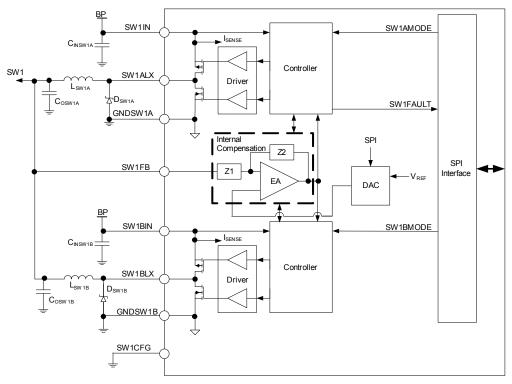

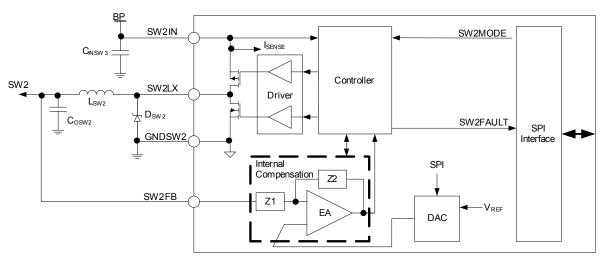

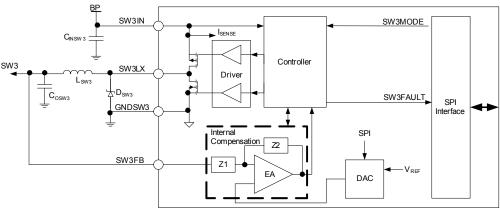

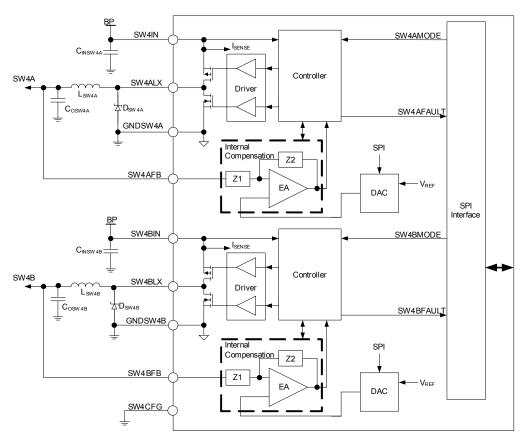

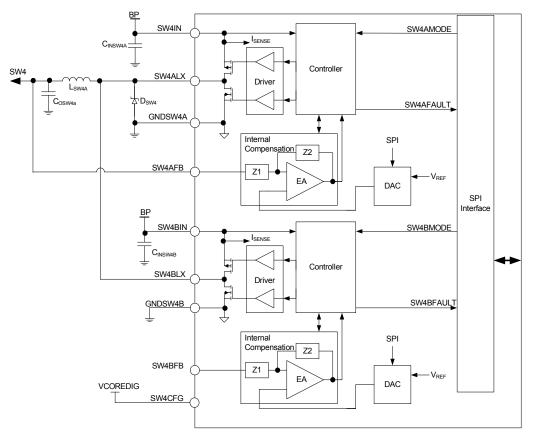

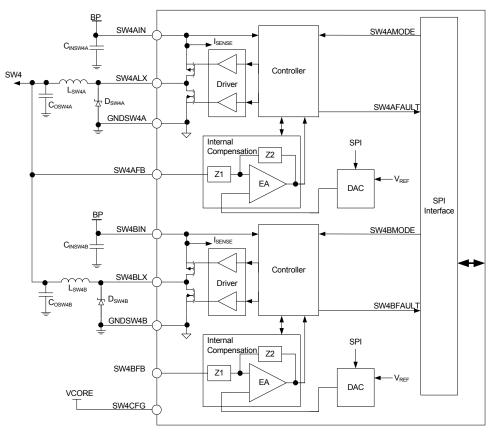

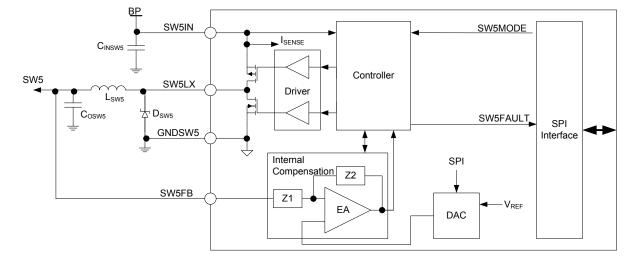

|          |       |               | uck Switching Regulators               |   |

|          |       |               | oost Switching Regulator               |   |

|          |       |               | inear Regulators (LDOs)                |   |

|          | 7.6   |               | Digital Converter                      |   |

|          | 1.0   |               | nput Selector                          |   |

|          |       |               | iontrol                                |   |

|          |       |               | redicated Readings                     |   |

|          |       |               | ouch Screen Interface                  |   |

|          |       |               | DC Specifications                      |   |

|          | 7.7   |               | Sircuits                               |   |

|          |       |               | ieneral Purpose I/Os                   |   |

|          |       |               | WM Outputs                             |   |

|          | 7.8   |               | rfaces                                 |   |

|          | 1.0   |               | PI Interface                           |   |

|          |       |               | 2C Interface                           |   |

|          |       |               | PI/I2C Specification                   |   |

|          |       | 1.0.0 0       | • m20 opcomoditori                     | 1 |

34709

|                      | 7.9                     | Configu    | ration Registers                           | 88  |  |  |  |

|----------------------|-------------------------|------------|--------------------------------------------|-----|--|--|--|

|                      |                         | 7.9.1      | Register Set structure                     |     |  |  |  |

|                      |                         | 7.9.2      | Specific Registers                         | 89  |  |  |  |

|                      |                         | 7.9.3      | SPI/I2C Register Map                       | 90  |  |  |  |

|                      |                         | 7.9.4      | SPI Register's Bit Description             | 96  |  |  |  |

| 8                    | Туріс                   | al Applic  | ations                                     | 128 |  |  |  |

|                      | 8.1 Application Diagram |            |                                            |     |  |  |  |

| 8.2 Bill of Material |                         |            |                                            |     |  |  |  |

|                      | 8.3                     | 34709 L    | ayout Guidelines                           | 132 |  |  |  |

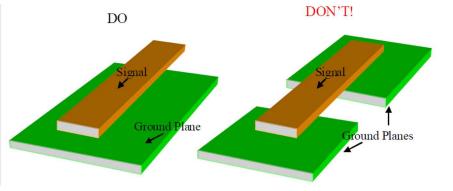

|                      |                         | 8.3.1      | General board recommendations              | 132 |  |  |  |

|                      |                         | 8.3.2      | General Routing Requirements               | 132 |  |  |  |

|                      |                         | 8.3.3      | Parallel Routing Requirements              | 132 |  |  |  |

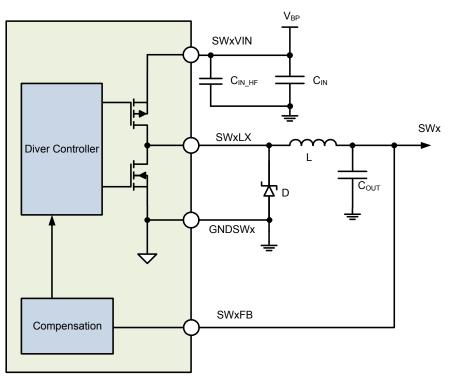

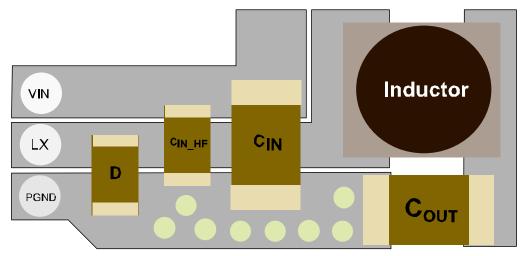

|                      |                         | 8.3.4      | Switching Regulator Layout Recommendations | 133 |  |  |  |

| 9                    | Pack                    | aging      | · · · · · · · · · · · · · · · · · · ·      | 135 |  |  |  |

| 10                   | Refe                    | rence Se   | ction                                      | 138 |  |  |  |

| 11                   | Revis                   | sion Histo | ۲ <b>γ</b>                                 | 139 |  |  |  |

### 34709

# 1 Orderable Parts

This section describes the part numbers available to be purchased, along with their differences. Valid orderable part numbers are provided on the web. To determine the orderable part numbers for this device, go to <a href="http://www.freescale.com">http://www.freescale.com</a> and perform a part number search for the following device numbers.

### Table 1. Orderable Part Variations

| Part Number <sup>(1)</sup> | Temperature (T <sub>A</sub> ) | Package                                  |

|----------------------------|-------------------------------|------------------------------------------|

| MC34709VK                  | -40 to 85 °C                  | 130 MAPBGA - 8.0 x 8.0 mm - 0.5 mm Pitch |

Notes

1. To Order parts in Tape & Reel, add the R2 suffix to the part number.

# 2 Part Identification

This section provides an explanation of the part numbers and their alpha numeric breakdown.

# 2.1 Description

Part numbers for the chips have fields that identify the specific part configuration. You can use the values of these fields to determine the specific part you have received.

# 2.2 Format and Examples

Part numbers for a given device have the following format, followed by a device example:

```

Table 2 - Part Numbering - Analog:

```

MC tt xxx r v PP RR - MC34709VKR2

## 2.3 Fields

These tables list the possible values for each field in the part number (not all combinations are valid).

| FIELD | DESCRIPTION             | VALUES                                                                              |

|-------|-------------------------|-------------------------------------------------------------------------------------|

| МС    | Product Category        | MC- Qualified Standard     PC- Prototype Device                                     |

| tt    | Temperature Range       | • 33 = -40 °C to > 105 °C<br>• 34 = -40 °C to ≤ 105 °C<br>• 35 = -55 °C to ≥ 125 °C |

| ххх   | Product Number          | Assigned by Marketing                                                               |

| r     | Revision                | • (default blank)                                                                   |

| v     | Variation               | • (default blank)                                                                   |

| PP    | Package Identifier      | Varies by package                                                                   |

| RR    | Tape and Reel Indicator | • R2 = 13 inch reel hub size                                                        |

### Table 2: Part Numbering - Analog

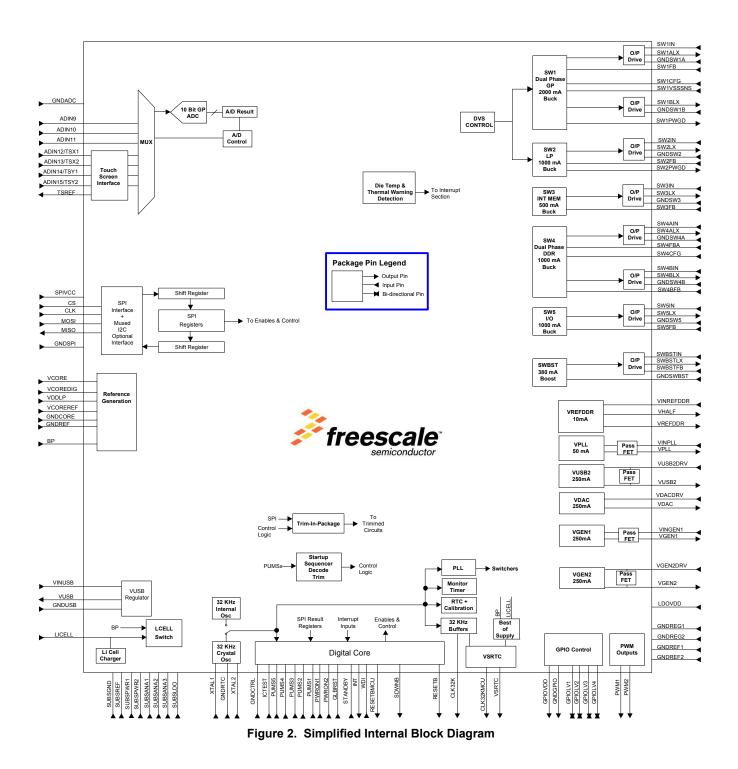

# 3 Internal Block Diagram

**Pin Connections**

# 4 Pin Connections

# 4.1 Ballmap

|   | 1        | 2      | 3         | 4      | 5         | 6       | 7       | 8        | 9        | 10       | 11       | 12       | 13        | 14        | 15      |

|---|----------|--------|-----------|--------|-----------|---------|---------|----------|----------|----------|----------|----------|-----------|-----------|---------|

| A |          | MISO   | GNDSPI    | SPIVCC | GLBRST    | PWRON1  | PWM2    | PWM1     | ICTEST   | SW2LX    |          | SW2FB    | SW2PWGD   | NC_2      |         |

| в | CLK      | CS     | MOSI      | INT    | RESETB    | GNDCTRL | GPIOLV1 |          | GPIOLV2  | GNDSW2   | SW2IN    | GNDREF2  | SW3FB     |           | NC_3    |

| С | GNDUSB   |        |           |        |           |         | GPIOLV0 | GPIOVDD  | GNDGPIO  |          |          |          |           |           |         |

| D | VINUSB   | VUSB   |           |        | RESETBMCU | SDWNB   |         |          |          |          |          |          |           | GNDSW3    | SW3LX   |

| E | XTAL1    |        | CLK32K    |        | PWRON2    | PUMS5   |         | SUBSPWR1 |          | GPIOLV3  | SUBSPWR2 |          |           | SW3IN     |         |

| F | GNDRTC   |        | CLK32KVCC |        | PUMS4     | PUMS3   |         | SUBSPWR1 | SUBSPWR1 | SUBSANA2 |          |          |           | GNDSWBST  | SWBSTIN |

| G | XTAL2    |        | CLK32KMCU |        | PUMS2     | PUMS1   |         | SUBSPWR1 | SUBSPWR1 | SUBSPWR3 |          |          |           | SWBSTLX   |         |

| н | GNDCORE  | VSRTC  |           |        | GNDADC    | ADIN9   |         | SUBSPWR1 | SUBSPWR1 | SUBSLDO  |          | VGEN1    |           | VINGEN1   | SWBSTFB |

| J | VCOREDIG | VCORE  |           |        | ADIN10    | ADIN11  |         | SUBSGND  | SUBSPWR1 |          |          | GNDREG2  |           | VINREFDDR | VHALF   |

| К | VCOREREF |        | WDI       |        | TSX1      | TSREF   |         | SUBSREF  | SUBSPWR  | SW1PWGD  |          | SUBSANA1 |           | VPLL      | VREFDDR |

| L | VDDLP    |        | TSY2      | TSX2   |           | TSY1    |         |          |          |          |          | SW1CFG   |           | VGEN2DRV  | VINPLL  |

| М | GNDREF   | LICELL |           |        |           | SW4CFG  |         | SW5FB    |          |          |          |          |           | GNDREG1   | VGEN2   |

| N | BP       | SW4AFB |           |        |           |         |         |          | GNDREF1  |          |          |          |           | VDACDRV   | LDOVDD  |

| Ρ | STANDBY  | SW4BFB | GNDSW4A   | SW4AIN | SW4BIN    | GNDSW4B | SW5IN   | GNDSW5   | GNDSW1A  | SW1IN    | SW1IN    | GNDSW1B  | SW1FB     | VUSB2DRV  | VDAC    |

| R | NC_1     |        | SW4ALX    |        |           | SW4BLX  |         | SW5LX    | SW1ALX   |          | SW1BLX   |          | SW1VSSSNS | VUSB2     |         |

Figure 3. Top View Ballmap

# 4.2 Pin Definitions

### Table 3. Pin Definitions

| Pin Number      | Pin Name  | Pin Function | Definition                                                                                  |  |

|-----------------|-----------|--------------|---------------------------------------------------------------------------------------------|--|

| Supply          |           | •            |                                                                                             |  |

| N1              | BP        | I            | <ol> <li>Application supply point</li> <li>Input supply to the IC core circuitry</li> </ol> |  |

| D6              | SDWNB     | 0            | Indication of imminent system shutdown                                                      |  |

| IC Core         |           |              |                                                                                             |  |

| J2              | VCORE     | 0            | Regulated supply for the IC analog core circuitry                                           |  |

| J1              | VCOREDIG  | 0            | Regulated supply for the IC digital core circuitry                                          |  |

| K1              | VCOREREF  | 0            | Main bandgap reference                                                                      |  |

| L1              | VDDLP     | 0            | VDDLP reference                                                                             |  |

| H1              | GNDCORE   | GND          | Ground for the IC core circuitry                                                            |  |

| M1              | GNDREF    | GND          | Ground reference for IC core circuitry                                                      |  |

| Switching Regul | ators     |              | ·                                                                                           |  |

| P10<br>P11      | SW1IN     | I            | Regulator 1 input <sup>(2)</sup>                                                            |  |

| R9              | SW1ALX    | 0            | Regulator 1A switch node connection <sup>(2)</sup>                                          |  |

| P13             | SW1FB     | I            | Regulator 1 feedback <sup>(2)</sup>                                                         |  |

| P9              | GNDSW1A   | GND          | Ground for Regulator 1A                                                                     |  |

| R13             | SW1VSSSNS | GND          | Regulator 1 sense                                                                           |  |

| K10             | SW1PWGD   | 0            | Power good signal for SW1 <sup>(2)</sup>                                                    |  |

| R11             | SW1BLX    | 0            | Regulator 1B switch node connection <sup>(2)</sup>                                          |  |

| P12             | GNDSW1B   | GND          | Ground for Regulator 1B                                                                     |  |

| L12             | SW1CFG    | I            | Regulator 1A/B mode configuration <sup>(2)</sup>                                            |  |

| B11             | SW2IN     | I            | Regulator 2 input <sup>(2)</sup>                                                            |  |

| A10             | SW2LX     | 0            | Regulator 2 switch node connection <sup>(2)</sup>                                           |  |

| A12             | SW2FB     | I            | Regulator 2 feedback <sup>(2)</sup>                                                         |  |

| B10             | GNDSW2    | GND          | Ground for Regulator 2                                                                      |  |

| A13             | SW2PWGD   | 0            | Power good signal for SW2 <sup>(2)</sup>                                                    |  |

| E14             | SW3IN     | I            | Regulator 3 input <sup>(2)</sup>                                                            |  |

| D15             | SW3LX     | 0            | Regulator 3 switch node connection <sup>(2)</sup>                                           |  |

| B13             | SW3FB     | I            | Regulator 3 feedback <sup>(2)</sup>                                                         |  |

| D14             | GNDSW3    | GND          | Ground for Regulator 3                                                                      |  |

| B12             | GNDREF2   | GND          | Ground reference for Regulators                                                             |  |

| P4              | SW4AIN    | I            | Regulator 4A input <sup>(2)</sup>                                                           |  |

| R3              | SW4ALX    | 0            | Regulator 4A switch node connection <sup>(2)</sup>                                          |  |

| N2              | SW4AFB    | ļ            | Regulator 4A feedback <sup>(2)</sup>                                                        |  |

| P3              | GNDSW4A   | GND          | Ground for Regulator 4A                                                                     |  |

8

### Table 3. Pin Definitions (continued)

| P5       SW4BIN       I       Regulator 4B input <sup>(2)</sup> R6       SW4BLX       O       Regulator 4B switch node connection <sup>(2)</sup> P2       SW4BFB       I       Regulator 4B feedback <sup>(2)</sup> P6       GNDSW4B       GND       Ground for Regulator 4B         M6       SW4CFG       I       Regulator 4A/B mode configuration <sup>(2)</sup> P7       SW5IN       I       Regulator 5 input <sup>(2)</sup> R8       SW5LX       O       Regulator 5 output <sup>(2)</sup> M8       SW5FB       I       Regulator 5 feedback <sup>(2)</sup> P8       GNDSW5       GND       Ground for Regulator 5         N9       GNDREF1       GND       Ground reference for regulators         F15       SWBSTIN       I       Boost Regulator BP supply <sup>(2)</sup> G14       SWBSTLX       O       SWBST switch node connection <sup>(2)</sup> H15       SWBSTFB       I       Boost Regulator feedback <sup>(2)</sup> F14       GNDSWBST       GND       Ground for regulator boost         LDO Regulators       I       VREFDDR input supply       K15         K15       VREFDDR       I       VREFDDR regulator output         J15       VHALF       O       Half supply re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                        |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|

| P2SW4BFBIRegulator 4B feedback (2)P6GNDSW4BGNDGround for Regulator 4BM6SW4CFGIRegulator 4A/B mode configuration (2)P7SW5INIRegulator 5 input (2)R8SW5LXORegulator 5 output (2)M8SW5FBIRegulator 5 feedback (2)P8GNDSW5GNDGround for Regulator 5N9GNDREF1GNDGround reference for regulatorsF15SWBSTINIBoost Regulator BP supply (2)G14SWBSTLXOSWBST switch node connection (2)H15SWBSTFBIBoost Regulator feedback (2)F14GNDSWBSTGNDGround for regulator boostLDO RegulatorsJ14VINREFDDRIVREFDDR regulator outputJ15VHALFOHalf supply reference for VREFDDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                        |  |

| P6GNDSW4BGNDGround for Regulator 4BM6SW4CFGIRegulator 4A/B mode configuration (2)P7SW5INIRegulator 5 input (2)R8SW5LXORegulator 5 output (2)M8SW5FBIRegulator 5 feedback (2)P8GNDSW5GNDGround for Regulator 5N9GNDREF1GNDGround reference for regulatorsF15SWBSTINIBoost Regulator BP supply (2)G14SWBSTLXOSWBST switch node connection (2)H15SWBSTFBIBoost Regulator feedback (2)F14GNDSWBSTGNDGround for regulator boostLDO RegulatorsJ14VINREFDDRIVREFDDR not for regulator outputJ15VHALFOHalf supply reference for VREFDDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                        |  |

| M6SW4CFGIRegulator 4A/B mode configuration (2)P7SW5INIRegulator 5 input (2)R8SW5LXORegulator 5 output (2)M8SW5FBIRegulator 5 feedback (2)P8GNDSW5GNDGround for Regulator 5N9GNDREF1GNDGround reference for regulatorsF15SWBSTINIBoost Regulator BP supply (2)G14SWBSTLXOSWBST switch node connection (2)H15SWBSTFBIBoost Regulator feedback (2)F14GNDSWBSTGNDGround for regulator boostLDO RegulatorsJ14VINREFDDRIVREFDDR regulator outputVREFDDR regulator outputJ15VHALFOHalf supply reference for VREFDDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                        |  |

| P7SW5INIRegulator 5 input (2)R8SW5LXORegulator 5 output (2)M8SW5FBIRegulator 5 feedback (2)P8GNDSW5GNDGround for Regulator 5N9GNDREF1GNDGround reference for regulatorsF15SWBSTINIBoost Regulator BP supply (2)G14SWBSTLXOSWBST switch node connection (2)H15SWBSTFBIBoost Regulator feedback (2)F14GNDSWBSTGNDGround for regulator boostLDO RegulatorsJ14VINREFDDRIJ15VHALFOHalf supply reference for VREFDDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                        |  |

| R8SW5LXORegulator 5 output (2)M8SW5FBIRegulator 5 feedback (2)P8GNDSW5GNDGround for Regulator 5N9GNDREF1GNDGround reference for regulatorsF15SWBSTINIBoost Regulator BP supply (2)G14SWBSTLXOSWBST switch node connection (2)H15SWBSTFBIBoost Regulator feedback (2)F14GNDSWBSTGNDGround for regulator boostLDO RegulatorsJ14VINREFDDRIVREFDDROVREFDDR regulator outputJ15VHALFOHalf supply reference for VREFDDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |  |

| M8SW5FBIRegulator 5 feedback (2)P8GNDSW5GNDGround for Regulator 5N9GNDREF1GNDGround reference for regulatorsF15SWBSTINIBoost Regulator BP supply (2)G14SWBSTLXOSWBST switch node connection (2)H15SWBSTFBIBoost Regulator feedback (2)F14GNDSWBSTGNDGround for regulator boostLDO RegulatorsJ14VINREFDDRIVREFDDR input supplyK15VREFDDRJ15VHALFOHalf supply reference for VREFDDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |  |

| P8GNDSW5GNDGround for Regulator 5N9GNDREF1GNDGround reference for regulatorsF15SWBSTINIBoost Regulator BP supply (2)G14SWBSTLXOSWBST switch node connection (2)H15SWBSTFBIBoost Regulator feedback (2)F14GNDSWBSTGNDGround for regulator boostLDO RegulatorsJ14VINREFDDRIVREFDDR input supplyK15VREFDDRJ15VHALFOHalf supply reference for VREFDDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |  |

| N9GNDREF1GNDGround reference for regulatorsF15SWBSTINIBoost Regulator BP supply (2)G14SWBSTLXOSWBST switch node connection (2)H15SWBSTFBIBoost Regulator feedback (2)F14GNDSWBSTGNDGround for regulator boostLDO RegulatorsJ14VINREFDDRIVREFDDR input supplyVREFDDR regulator outputJ15VHALFOHalf supply reference for VREFDDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                        |  |

| F15SWBSTINIBoost Regulator BP supply (2)G14SWBSTLXOSWBST switch node connection (2)H15SWBSTFBIBoost Regulator feedback (2)F14GNDSWBSTGNDGround for regulator boostLDO RegulatorsJ14VINREFDDRIVREFDDR input supplyVREFDDR regulator outputJ15VHALFOHalf supply reference for VREFDDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                        |  |

| G14       SWBSTLX       O       SWBST switch node connection (2)         H15       SWBSTFB       I       Boost Regulator feedback (2)         F14       GNDSWBST       GND       Ground for regulator boost         LDO Regulators         J14       VINREFDDR       I       VREFDDR input supply         K15       VREFDDR       O       VREFDDR regulator output         J15       VHALF       O       Half supply reference for VREFDDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                        |  |

| H15       SWBSTFB       I       Boost Regulator feedback (2)         F14       GNDSWBST       GND       Ground for regulator boost         LDO Regulators       I       VREFDDR input supply         K15       VREFDDR       I       VREFDDR regulator output         J15       VHALF       O       Half supply reference for VREFDDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                        |  |

| F14     GNDSWBST     GND     Ground for regulator boost       LDO Regulators       J14     VINREFDDR     I     VREFDDR input supply       K15     VREFDDR     O     VREFDDR regulator output       J15     VHALF     O     Half supply reference for VREFDDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                        |  |

| Image: Second S |                        |  |

| J14     VINREFDDR     I     VREFDDR input supply       K15     VREFDDR     O     VREFDDR regulator output       J15     VHALF     O     Half supply reference for VREFDDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                        |  |

| K15     VREFDDR     O     VREFDDR regulator output       J15     VHALF     O     Half supply reference for VREFDDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                        |  |

| J15 VHALF O Half supply reference for VREFDDR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                        |  |

| L15 VINPLL I VPLL input supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                        |  |

| K14 VPLL O VPLL regulator output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                        |  |

| N14         VDACDRV         O         Drive output for VDAC regulator using an external PNP device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                        |  |

| P15 VDAC O VDAC regulator output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                        |  |

| N15         LDOVDD         I         Supply pin for VUSB2, VDAC, and VGEN2           N15         LDOVDD         I         Must be always connected to the same supply as the PNP emitter. Fuse BP as the LDOVDD supply. See Figure 24 for a typical connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                        |  |

| D2 VUSB O USB transceiver regulator output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                        |  |

| D1 VINUSB I VUSB input supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                        |  |

| C1 GNDUSB GND Ground for VUSB LDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |  |

| I VUSB2 input using internal PMOS FET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                        |  |

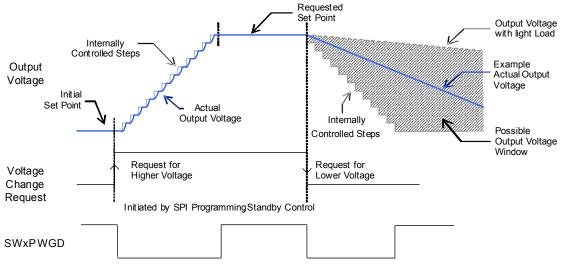

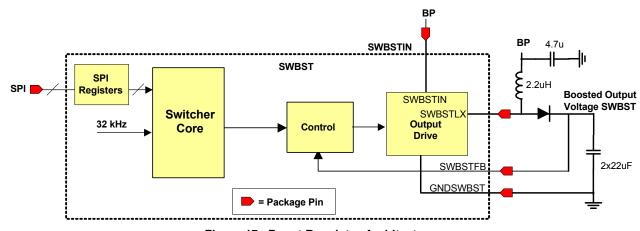

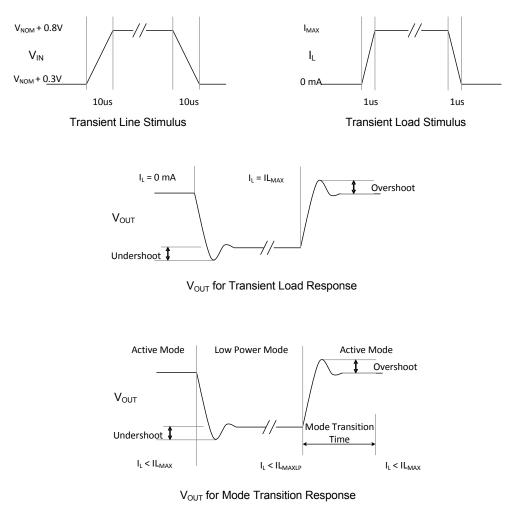

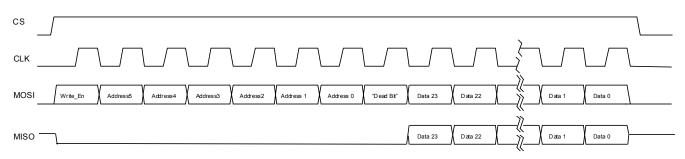

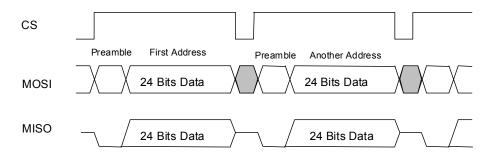

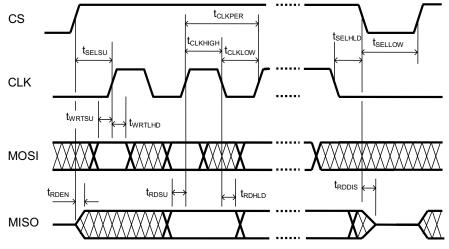

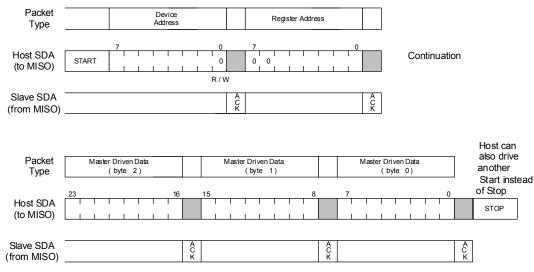

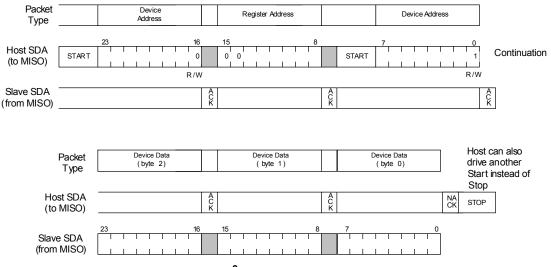

| P14 VUSB2DRV O Drive output for VUSB2 regulator using an external PNP device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                        |  |