DC1957A

Analog Devices Inc.The LTM2892 is a complete galvanic digital ?Module? (micromodule) isolator. No external components are required. Individual 3V to 5.5V supplies power each side of the digital isolator. Separate logic supply pins allow easy interfacing with different logic levels from 1.62V to 5.5V, independent of the main supply.Module options are available with compatibility to SPI (LTM2892-S) and I2C (LTM2892-I), master mode only, specifications.Coupled inductors provide 3500VRMS of isolation between the input and output logic interface. This device is ideal for systems where the ground loop is broken, allowing uninterrupted communication through large common mode transients faster than 50kV/?s.Applications Isolated SPI or I2C Interfaces Industrial Systems Test and Measurement Equipment Breaking Ground Loops

DC1959B-B

Analog Devices Inc.The LTC6948 is a high performance, low noise, 6.39GHz phase-locked loop (PLL) with a fully integrated VCO, including a reference divider, phase-frequency detector (PFD), ultralow noise charge pump, fractional feedback divider, and VCO output divider.The fractional divider uses an advanced, 4th order ?? modulator which provides exceptionally low spurious levels. This allows wide loop bandwidths, producing extremely low integrated phase noise values.The programmable VCO output divider, with a range of 1 through 6, extends the output frequency range.Applications Wireless Basestations (LTE, WiMAX, W-CDMA, PCS) Microwave Data Links Military and Secure Radio Test and Measurement

DC1959B-D

Analog Devices Inc.The LTC6948 is a high performance, low noise, 6.39GHz phase-locked loop (PLL) with a fully integrated VCO, including a reference divider, phase-frequency detector (PFD), ultralow noise charge pump, fractional feedback divider, and VCO output divider.The fractional divider uses an advanced, 4th order ?? modulator which provides exceptionally low spurious levels. This allows wide loop bandwidths, producing extremely low integrated phase noise values.The programmable VCO output divider, with a range of 1 through 6, extends the output frequency range.Applications Wireless Basestations (LTE, WiMAX, W-CDMA, PCS) Microwave Data Links Military and Secure Radio Test and Measurement

DC1963A

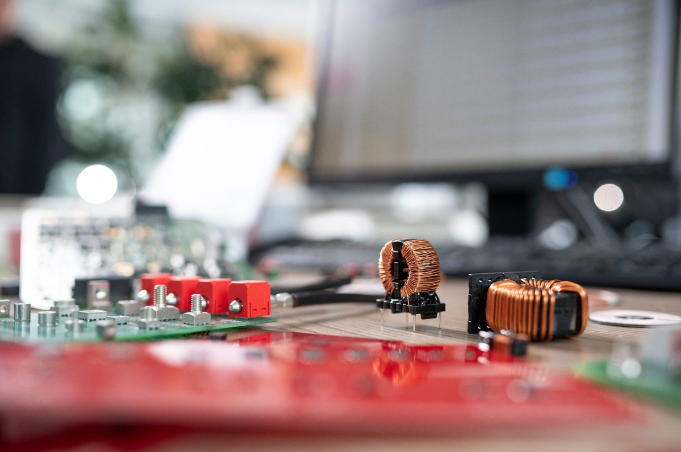

Analog Devices Inc.The LT8310 is a simple-to-use resonant reset forward converter controller that drives the gate of a low side N-channel MOSFET from an internally regulated 10V supply. The LT8310 features duty mode control that generates a stable, regulated, isolated output using a single power transformer. With the addition of output voltage feedback, via opto-coupler (isolated) or directly wired (nonisolated), current mode regulation is activated, improving output accuracy and load response. The flexibility to choose transformer turns ratio makes high step-down or step-up ratios possible without operating at duty cycle extremes.The user can program the switching frequency from 100kHz to 500kHz to optimize efficiency, performance or external component size. A synchronous output is available for controlling secondary side synchronous rectification to improve efficiency. User programmable protection features include monitors on input voltage (UVLO and OVLO) and switch current (overcurrent limit). The LT8310 soft-start feature helps protect the transformer from flux saturation.Applications Industrial, Automotive and Military Systems 48V Telecommunication Isolated Power Supplies Isolated and Nonisolated DC/DC Converters

AD9627-125EBZ

Analog Devices Inc.The AD9627 is a dual, 12-bit, 80 MSPS/105 MSPS/125 MSPS/150 MSPS analog-to-digital converter (ADC). The AD9627 is designed to support communications applications where low cost, small size and versatility are desired.The dual ADC core features a multistage, differential pipelined architecture with integrated output error correction logic. Each ADC features wide bandwidth differential sample-and-hold analog input amplifiers supporting a variety of user-selectable input ranges. An integrated voltage reference eases design considerations. A duty cycle stabilizer is provided to compensate for variations in the ADC clock duty cycle, allowing the converters to maintain excellent performance. The AD9627 has several functions that simplify the automatic gain control (AGC) function in the system receiver. The fast detect feature allows fast overrange detection by outputting four bits of input level information with very short latency. In addition, the programmable threshold detector allows monitoring of the incoming signal power, using the four fast detect bits of the ADC with very low latency. If the input signal level exceeds the programmable threshold, the coarse upper threshold indicator goes high. Because this threshold indicator has very low latency, the user can quickly turn down the system gain to avoid an overrange condition. The second AGC-related function is the signal monitor. This block allows the user to monitor the composite magnitude of the incoming signal, which aids in setting the gain to optimize the dynamic range of the overall system. The ADC output data can be routed directly to the two external 12-bit output ports. These outputs can be set from 1.8 V to 3.3 V CMOS or 1.8 V LVDS. Flexible power-down options allow significant power savings, when desired.Programming for setup and control is accomplished using a 3-bit SPI-compatible serial interface.The AD9627 is available in a 64-lead LFCSP and is specified over the industrial temperature range of ?40?C to +85?C.PRODUCT HIGHLIGHTS Integrated dual, 12-bit, 80 MSPS/105 MSPS/125 MSPS/150 MSPS ADC. Fast overrange detect and signal monitor with serial output. Signal monitor block with dedicated serial output mode. Proprietary differential input that maintains excellent SNR performance for input frequencies up to 450 MHz. Operation from a single 1.8 V supply and a separate digital output driver supply to accommodate 1.8 V to 3.3 V logic families. Standard serial port interface (SPI) that supports various product features and functions, such as data formatting (offset binary, twos complement, or gray coding), enabling the clock DCS, power-down, test modes, and voltage reference mode. Pin compatibility with the AD9640, AD9627-11, and AD9600 for a simple migration from 12 bits to 14 bits, 11 bits, or 10 bits.APPLICATIONS Communications Diversity radio systems Multimode digital receivers (3G) GSM, EDGE, WCDMA, CDMA2000, WiMAX, TD-SCDMA I/Q demodulation systems Smart antenna systems General-purpose software radios Broadband data applications

AD9628-125EBZ

Analog Devices Inc.The AD9628 is a monolithic, dual-channel, 1.8 V supply, 12-bit, 125 MSPS/105 MSPS analog-to-digital converter (ADC). It features a high performance sample-and-hold circuit and on-chip voltage reference.The product uses multistage differential pipeline architecture with output error correction logic to provide 12-bit accuracy at 125 MSPS data rates and to guarantee no missing codes over the full operating temperature range.The ADC contains several features designed to maximize flexibility and minimize system cost, such as programmable clock and data alignment and programmable digital test pattern generation. The available digital test patterns include built-in deterministic and pseudorandom patterns, along with custom user-defined test patterns entered via the serial port interface (SPI).A differential clock input controls all internal conversion cycles. An optional duty cycle stabilizer (DCS) compensates for wide variations in the clock duty cycle while maintaining excellent overall ADC performance.The digital output data is presented in offset binary, Gray code, or twos complement format. A data output clock (DCO) is provided for each ADC channel to ensure proper latch timing with receiving logic. 1.8 V CMOS or LVDS output logic levels are supported. Output data can also be multiplexed onto a single output bus.APPLICATIONS Communications Diversity radio systems Multimode digital receivers GSM, EDGE, W-CDMA, LTE, CDMA2000, WIMAX, TD-SCDMA I/Q demodulation systems Smart antenna systems Broadband data applications Battery-powered instruments Hand-held scope meters Portable medical imaging Ultrasound Radar/LIDARPRODUCT HIGHLIGHTS The AD9628 operates from a single 1.8 V analog power supply and features a separate digital output driver supply to accommodate 1.8 V CMOS or LVDS logic families.? The patented sample-and-hold circuit maintains excellent performance for input frequencies up to 200 MHz and is designed for low cost, low power, and ease of use.? A standard serial port interface supports various product features and functions, such as data output formatting, internal clock divider, power-down, DCO/data timing and offset adjustments.? The AD9628 is packaged in a 64-lead RoHS-compliant LFCSP that is pin compatible with the AD9650?/ AD9269?/ AD9268?16-bit ADC, the AD9258?/ AD9251?/ AD9648?14-bit ADCs, the AD9231 12-bit ADC, and the AD9608?/ AD9204?10-bit ADCs, enabling a simple migration path between 10-bit and 16-bit converters sampling from 20MSPS to 125MSPS.

AD9629-40EBZ

Analog Devices Inc.The AD9629 is a monolithic, single channel 1.8 V supply, 12-bit, 20 MSPS/40 MSPS/65MSPS/80 MSPS analog-to-digital converter (ADC). It features a high performance sample-and-hold circuit and on-chip voltage reference.The product uses multistage differential pipeline architecture with output error correction logic to provide 12-bit accuracy at 80 MSPS data rates and to guarantee no missing codes over the full operating temperature range.The ADC contains several features designed to maximize flexibility and minimize system cost, such as programmable clock and data alignment and programmable digital test pattern generation. The available digital test patterns include built-in deterministic and pseudorandom patterns, along with custom user-defined test patterns entered via the serial port interface (SPI).A differential clock input with optional 1, 2, or 4 divide ratios controls all internal conversion cycles.The digital output data is presented in offset binary, gray code, or twos complement format. A data output clock (DCO) is provided to ensure proper latch timing with receiving logic. Both 1.8 V and 3.3 V CMOS levels are supported.The AD9629 is available in a 32-lead RoHS compliant LFCSP and is specified over the industrial temperature range (?40?C to +85?C).Applications Communications Diversity radio systems Multimode digital receivers GSM, EDGE, W-CDMA, LTE, CDMA2000, WiMAX, TD-SCDMA Smart antenna systems Battery-powered instruments Hand held scope meters Portable medical imaging Ultrasound Radar/LIDAR PET/SPECT imagingProduct Highlights1. The AD9629 operates from a single 1.8 V analog power supply and features a separate digital output driver supply to accommodate 1.8 V to 3.3 V logic families.2. The sample-and-hold circuit maintains excellent performance for input frequencies up to 200 MHz and is designed for low cost, low power, and ease of use.3. A standard serial port interface (SPI) supports various product features and functions, such as data output formatting, internal clock divider, power-down, DCO and data output (D11 to D0) timing and offset adjustments, and voltage reference modes.4. The AD9629 is packaged in a 32-lead RoHS compliant LFCSP that is pin compatible with the AD9609 10-bit ADC and the AD9649 14-bit ADC, enabling a simple migration path between 10-bit and 14-bit converters sampling from 20 MSPS to 80 MSPS.

AD9634-250EBZ

Analog Devices Inc.The AD9634 is a 12-bit, analog-to-digital converter (ADC) with sampling speeds of up to 250 MSPS. The AD9634 is designed to support communications applications where low cost, small size, wide bandwidth, and versatility are desired.The ADC core features a multistage, differential pipelined architecture with integrated output error correction logic. The ADC features wide bandwidth inputs that can support a variety of user-selectable input ranges. An integrated voltage reference eases design considerations. A duty cycle stabilizer (DCS) is provided to compensate for variations in the ADC clock duty cycle, allowing the converter to maintain excellent performance.The ADC output data are routed directly to the external 12-bit LVDS output port.Flexible power-down options allow significant power savings, when desired.Programming for setup and control is accomplished using a 3-wire, SPI-compatible serial interface.The AD9634 is available in a 32-lead LFCSP and is specified over the industrial temperature range of ?40?C to +85?C. This product is protected by a U.S. patent.PRODUCT HIGHLIGHTS Integrated 12-bit, 170 MSPS/210 MSPS/250 MSPS ADC. Fast overrange and threshold detect. Proprietary differential input maintains excellent SNR performance for input frequencies up to 350 MHz. 3-pin, 1.8V SPI port for register programming and readback. Pin compatibility with the?AD9642, allowing a simple migration up to 14 bits, and with the?AD6672. APPLICATIONS Communications Diversity radio systems Multimode digital receivers (3G) TD-SCDMA, WiMax, WCDMA, CDMA2000, GSM, EDGE, LTE I/Q demodulation systems Smart antenna systems General-purpose software radios Ultrasound equipment Broadband data applications

AD9642-250EBZ

Analog Devices Inc.The AD9642 is a 14-bit analog-to-digital converter (ADC) with sampling speeds of up to 250 MSPS. The AD9642 is designed to support communications applications, where low cost, small size, wide bandwidth, and versatility are desired.The ADC core features a multistage, differential pipelined architecture with integrated output error correction logic. The ADC features wide bandwidth inputs that can support a variety of user-selectable input ranges. An integrated voltage reference eases design considerations. A duty cycle stabilizer (DCS) is provided to compensate for variations in the ADC clock duty cycle, allowing the converter to maintain excellent performance.The ADC output data is routed directly to the external 14-bit LVDS output port.Flexible power-down options allow significant power savings, when desired.Programming for setup and control is accomplished using a 3-wire SPI-compatible serial interface.The AD9642 is available in a 32-lead LFCSP and is specified over the industrial temperature range of ?40?C to +85?C. This product is protected by a U.S. patent. APPLICATIONS Communications Diversity radio systems Multimode digital receivers (3G) TD-SCDMA, WiMax, WCDMA, CDMA2000, GSM, EDGE, LTE I/Q demodulation systems Smart antenna systems General-purpose software radios Ultrasound equipment Broadband data applicationsPRODUCT HIGHLIGHTS Integrated 14-bit, 170 MSPS/210 MSPS/250 MSPS ADC. Operation from a single 1.8 V supply and a separate digital output driver supply accommodating LVDS outputs. Proprietary differential input maintains excellent SNR performance for input frequencies of up to 350 MHz. 3-pin, 1.8 V SPI port for register programming and readback. Pin compatibility with the AD9634, allowing a simple migration from 14 bits to 12 bits, and with the AD6672.

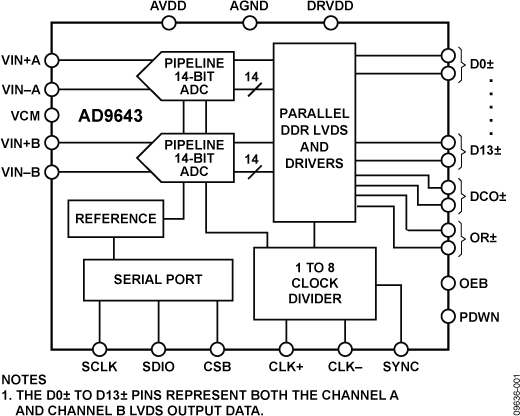

AD9643-250EBZ

Analog Devices Inc.The AD9643 is a dual, 14-bit analog-to-digital converter (ADC) with sampling speeds of up to 250 MSPS. The AD9643 is designed to support communications applications, where low cost, small size, wide bandwidth, and versatility are desired.The dual ADC cores feature a multistage, differential pipelined architecture with integrated output error correction logic. Each ADC features wide bandwidth inputs supporting a variety of user-selectable input ranges. An integrated voltage reference eases design considerations. A duty cycle stabilizer is provided to compensate for variations in the ADC clock duty cycle, allowing the converters to maintain excellent performance.The ADC output data is routed directly to the external, 14-bit, LVDS output port and formatted as either interleaved or channel multiplexed.Flexible power-down options allow significant power savings, when desired.Programming for setup and control are accomplished using a 3-wire SPI-compatible serial interface.The AD9643 is available in a 64-lead LFCSP and is specified over the industrial temperature range of ?40?C to +85?C. Thisproduct is protected by a U.S. patent.Product Highlights Integrated dual, 14-bit, 170 MSPS/210 MSPS/250 MSPS ADCs. Operation from a single 1.8 V supply and a separate digital output driver supply accommodating LVDS outputs. Proprietary differential input maintains excellent SNR performance for input frequencies of up to 400 MHz. SYNC input allows synchronization of multiple devices. 3-pin, 1.8 V SPI port for register programming and register readback. Pin compatibility with the AD9613, allowing a simple migration down from 14 bits to 12 bits. This part is also pin compatible with the AD6649 and the AD6643.Applications Communications Diversity radio systems Multimode digital receivers (3G) TD-SCDMA, WiMax, WCDMA, CDMA2000, GSM, EDGE, LTE I/Q demodulation systems Smart antenna systems General-purpose software radios Ultrasound equipment Broadband data applications

AD9650-105EBZ

Analog Devices Inc.The AD9650 is a dual, 16-bit, 25 MSPS/65 MSPS/80 MSPS/ 105 MSPS analog-to-digital converter (ADC) designed for digitizing high frequency, wide dynamic range signals with input frequencies of up to 300 MHz.The dual ADC core features a multistage, differential pipelined architecture with integrated output error correction logic. Each ADC features wide bandwidth, differential sample-and-hold analog input amplifiers, and shared integrated voltage reference, which eases design considerations. A duty cycle stabilizer is provided to compensate for variations in the ADC clock duty cycle, allowing the converters to maintain excellent performance.The ADC output data can be routed directly to the two external 16-bit output ports or multiplexed on a single 16-bit bus. These outputs can be set to either 1.8 V CMOS or LVDS.Flexible power-down options allow significant power savings, when desired.Programming for setup and control is accomplished using a 3-wire SPI-compatible serial interface.The AD9650 is available in a 64-lead LFCSP and is specified over the industrial temperature range of ?40?C to +85?C.PRODUCT HIGHLIGHTS On-chip dither option for improved SFDR performance with low power analog input. Proprietary differential input that maintains excellent SNR performance for input frequencies up to 300 MHz. Operation from a single 1.8 V supply and a separate digital output driver supply accommodating 1.8 V CMOS or LVDS outputs. Standard serial port interface (SPI) that supports various product features and functions, such as data formatting (offset binary, twos complement, or gray coding), enabling the clock DCS, power-down, and test modes. Pin compatible with the AD9268 and other dual families, AD9269, AD9251, AD9231, and AD9204. This allows a simple migration across resolutions and bandwidth.?APPLICATIONS Industrial instrumentation X-Ray, MRI, and ultrasound equipment High speed pulse acquisition Chemical and spectrum analysis Direct conversion receivers Multimode digital receivers Smart antenna systems General-purpose software radios

AD9655-125EBZ

Analog Devices Inc.The AD9655 is a dual, 16-bit, 125 MSPS analog-to-digital converter (ADC) with an on-chip sample-and-hold circuit designed for low cost, low power, small size, and ease of use. The product operates at a conversion rate of up to 125 MSPS and is optimized for outstanding dynamic performance and low power in applications where a small package size is critical.The ADC requires a single 1.8 V power supply and an LVPECL-/CMOS-/LVDS-compatible sample rate clock for full performance operation. External reference or driver components are not required for many applications.The ADC automatically multiplies the sample rate clock for the appropriate LVDS serial data rate. A data clock output (DCO) for capturing data on the output and a frame clock output (FCO) for signaling a new output byte are provided. Individual channel power-down is supported.The AD9655 typically consumes less than 2 mW in SPI powerdown mode. The available digital test patterns include built-in deterministic and pseudorandom patterns, along with custom user-defined test patterns entered via the serial port interface (SPI).The AD9655 is available in a RoHS-compliant, 32-lead LFCSP. It is specified over the industrial temperature range of ?40?C to +85?C. This device is protected by a U.S. patent.PRODUCT HIGHLIGHTS Small Footprint. Two ADCs are contained in a small, spacesaving package. Pin compatible to the AD9645 14-bit and AD9635 12-bit dual ADCs. Ease of use. A DCO operates at frequencies of up to 500 MHz and supports double data rate (DDR) operation. User Flexibility. The SPI control offers a wide range of flexible features to meet specific system requirements.APPLICATIONS Communications Diversity radio systems Multimode digital receivers GSM, EDGE, W-CDMA, LTE, CDMA2000, WiMAX, TD-SCDMA I/Q demodulation systems Smart antenna systems Broadband data applications Battery-powered instruments Hand held scope meters Portable medical imaging Radar/LIDAR

AD9680-500EBZ

Analog Devices Inc.The AD9680 is a dual, 14-bit, 1.25 GSPS/1 GSPS/820 MSPS/500 MSPS analog-to-digital converter (ADC). The device has an on-chip buffer and sample-and-hold circuit designed for low power, small size, and ease of use. This device is designed for sampling wide bandwidth analog signals of up to 2 GHz. The AD9680 is optimized for wide input bandwidth, high sampling rate, excellent linearity, and low power in a small package.The dual ADC cores feature a multistage, differential pipelined architecture with integrated output error correction logic. Each ADC features wide bandwidth inputs supporting a variety of user-selectable input ranges. An integrated voltage reference eases design considerations.The analog input and clock signals are differential inputs. Each ADC data output is internally connected to two digital down-converters (DDCs). Each DDC consists of up to five cascaded signal processing stages: a 12-bit frequency translator (NCO), and four half-band decimation filters. The DDCs are bypassed by default.In addition to the DDC blocks, the AD9680 has several functions that simplify the automatic gain control (AGC) function in the communications receiver. The programmable threshold detector allows monitoring of the incoming signal power using the fast detect output bits of the ADC. If the input signal level exceeds the programmable threshold, the fast detect indicator goes high. Because this threshold indicator has low latency, the user can quickly turn down the system gain to avoid an overrange condition at the ADC input.Users can configure the Subclass 1 JESD204B-based high speed serialized output in a variety of one-, two-, or four-lane configurations, depending on the DDC configuration and the acceptable lane rate of the receiving logic device. Multiple device synchronization is supported through the SYSREF? and SYNCINB? input pins.The AD9680 has flexible power-down options that allow significant power savings when desired. All of these features can be programmed using a 1.8 V to 3.3 V capable, 3-wire SPI.The AD9680 is available in a Pb-free, 64-lead LFCSP and is specified over the ?40?C to +85?C industrial temperature range. This product is protected by a U.S. patent.PRODUCT HIGHLIGHTS Wide full power bandwidth supports IF sampling of signals up to 2 GHz. Buffered inputs with programmable input termination eases filter design and implementation. Four integrated wideband decimation filters and numerically controlled oscillator (NCO) blocks supporting multiband receivers. Flexible serial port interface (SPI) controls various product features and functions to meet specific system requirements. Programmable fast overrange detection. 9 mm ? 9 mm, 64-lead LFCSP.APPLICATIONS Communications Diversity multiband, multimode digital receivers 3G/4G, TD-SCDMA, W-CDMA, GSM, LTE General-purpose software radios Ultrawideband satellite receivers Instrumentation Radars Signals intelligence (SIGINT) DOCSIS 3.0 CMTS upstream receive paths HFC digital reverse path receivers

AD9680-LF1000EBZ

Analog Devices Inc.The AD9680 is a dual, 14-bit, 1.25 GSPS/1 GSPS/820 MSPS/500 MSPS analog-to-digital converter (ADC). The device has an on-chip buffer and sample-and-hold circuit designed for low power, small size, and ease of use. This device is designed for sampling wide bandwidth analog signals of up to 2 GHz. The AD9680 is optimized for wide input bandwidth, high sampling rate, excellent linearity, and low power in a small package.The dual ADC cores feature a multistage, differential pipelined architecture with integrated output error correction logic. Each ADC features wide bandwidth inputs supporting a variety of user-selectable input ranges. An integrated voltage reference eases design considerations.The analog input and clock signals are differential inputs. Each ADC data output is internally connected to two digital down-converters (DDCs). Each DDC consists of up to five cascaded signal processing stages: a 12-bit frequency translator (NCO), and four half-band decimation filters. The DDCs are bypassed by default.In addition to the DDC blocks, the AD9680 has several functions that simplify the automatic gain control (AGC) function in the communications receiver. The programmable threshold detector allows monitoring of the incoming signal power using the fast detect output bits of the ADC. If the input signal level exceeds the programmable threshold, the fast detect indicator goes high. Because this threshold indicator has low latency, the user can quickly turn down the system gain to avoid an overrange condition at the ADC input.Users can configure the Subclass 1 JESD204B-based high speed serialized output in a variety of one-, two-, or four-lane configurations, depending on the DDC configuration and the acceptable lane rate of the receiving logic device. Multiple device synchronization is supported through the SYSREF? and SYNCINB? input pins.The AD9680 has flexible power-down options that allow significant power savings when desired. All of these features can be programmed using a 1.8 V to 3.3 V capable, 3-wire SPI.The AD9680 is available in a Pb-free, 64-lead LFCSP and is specified over the ?40?C to +85?C industrial temperature range. This product is protected by a U.S. patent.PRODUCT HIGHLIGHTS Wide full power bandwidth supports IF sampling of signals up to 2 GHz. Buffered inputs with programmable input termination eases filter design and implementation. Four integrated wideband decimation filters and numerically controlled oscillator (NCO) blocks supporting multiband receivers. Flexible serial port interface (SPI) controls various product features and functions to meet specific system requirements. Programmable fast overrange detection. 9 mm ? 9 mm, 64-lead LFCSP.APPLICATIONS Communications Diversity multiband, multimode digital receivers 3G/4G, TD-SCDMA, W-CDMA, GSM, LTE General-purpose software radios Ultrawideband satellite receivers Instrumentation Radars Signals intelligence (SIGINT) DOCSIS 3.0 CMTS upstream receive paths HFC digital reverse path receivers

AD9680-LF500EBZ

Analog Devices Inc.The AD9680 is a dual, 14-bit, 1.25 GSPS/1 GSPS/820 MSPS/500 MSPS analog-to-digital converter (ADC). The device has an on-chip buffer and sample-and-hold circuit designed for low power, small size, and ease of use. This device is designed for sampling wide bandwidth analog signals of up to 2 GHz. The AD9680 is optimized for wide input bandwidth, high sampling rate, excellent linearity, and low power in a small package.The dual ADC cores feature a multistage, differential pipelined architecture with integrated output error correction logic. Each ADC features wide bandwidth inputs supporting a variety of user-selectable input ranges. An integrated voltage reference eases design considerations.The analog input and clock signals are differential inputs. Each ADC data output is internally connected to two digital down-converters (DDCs). Each DDC consists of up to five cascaded signal processing stages: a 12-bit frequency translator (NCO), and four half-band decimation filters. The DDCs are bypassed by default.In addition to the DDC blocks, the AD9680 has several functions that simplify the automatic gain control (AGC) function in the communications receiver. The programmable threshold detector allows monitoring of the incoming signal power using the fast detect output bits of the ADC. If the input signal level exceeds the programmable threshold, the fast detect indicator goes high. Because this threshold indicator has low latency, the user can quickly turn down the system gain to avoid an overrange condition at the ADC input.Users can configure the Subclass 1 JESD204B-based high speed serialized output in a variety of one-, two-, or four-lane configurations, depending on the DDC configuration and the acceptable lane rate of the receiving logic device. Multiple device synchronization is supported through the SYSREF? and SYNCINB? input pins.The AD9680 has flexible power-down options that allow significant power savings when desired. All of these features can be programmed using a 1.8 V to 3.3 V capable, 3-wire SPI.The AD9680 is available in a Pb-free, 64-lead LFCSP and is specified over the ?40?C to +85?C industrial temperature range. This product is protected by a U.S. patent.PRODUCT HIGHLIGHTS Wide full power bandwidth supports IF sampling of signals up to 2 GHz. Buffered inputs with programmable input termination eases filter design and implementation. Four integrated wideband decimation filters and numerically controlled oscillator (NCO) blocks supporting multiband receivers. Flexible serial port interface (SPI) controls various product features and functions to meet specific system requirements. Programmable fast overrange detection. 9 mm ? 9 mm, 64-lead LFCSP.APPLICATIONS Communications Diversity multiband, multimode digital receivers 3G/4G, TD-SCDMA, W-CDMA, GSM, LTE General-purpose software radios Ultrawideband satellite receivers Instrumentation Radars Signals intelligence (SIGINT) DOCSIS 3.0 CMTS upstream receive paths HFC digital reverse path receivers

AD9689-2000EBZ

Analog Devices Inc.The AD9689 is a dual, 14-bit, 2.0 GSPS/2.6 GSPS analog-to-digital converter (ADC). The device has an on-chip buffer and a sample-and-hold circuit designed for low power, small size, and ease of use. This product is designed to support communications applications capable of direct sampling wide bandwidth analog signals of up to 5 GHz. The ?3 dB bandwidth of the ADC input is 9 GHz. The AD9689 is optimized for wide input bandwidth, high sampling rate, excellent linearity, and low power in a small package.The dual ADC cores feature a multistage, differential pipelined architecture with integrated output error correction logic. Each ADC features wide bandwidth inputs supporting a variety of user-selectable input ranges. An integrated voltage reference eases design considerations. The analog input and clock signals are differential inputs. The ADC data outputs are internally connected to four digital downconverters (DDCs) through a crossbar mux. Each DDC consists of multiple cascaded signal processing stages: a 48-bit frequency translator (numerically controlled oscillator (NCO)), and decimation rates. The NCO has the option to select preset bands over the general-purpose input/output (GPIO) pins, which enables the selection of up to three bands. Operation of the AD9689 between the DDC modes is selectable via SPI-programmable profiles.In addition to the DDC blocks, the AD9689 has several functions that simplify the automatic gain control (AGC) function in a communications receiver. The programmable threshold detector allows monitoring of the incoming signal power using the fast detect control bits in Register 0x0245 of the ADC. If the input signal level exceeds the programmable threshold, the fast detect indicator goes high. Because this threshold indicator has low latency, the user can quickly turn down the system gain to avoid an overrange condition at the ADC input. In addition to the fast detect outputs, the AD9689 also offers signal monitoring capability. The signal monitoring block provides additional information about the signal being digitized by the ADC.The user can configure the Subclasss 1 JESD204B-based high speed serialized output in a variety of one-lane, two-lane, four-lane, and eight-lane configurations, depending on the DDC configuration and the acceptable lane rate of the receiving logic device. Multidevice synchronization is supported through the SYSREF? and SYNCINB? input pins.The AD9689 has flexible power-down options that allow significant power savings when desired. All of these features can be programmed using a 3-wire serial port interface (SPI).The AD9689 is available in a Pb-free, 196-ball BGA, specified over the ?40?C to +85?C ambient temperature range. This product is protected by a U.S. patent.Note that throughout this data sheet, multifunction pins, such as FD_A/GPIO_A0, are referred to either by the entire pin name or by a single function of the pin, for example, FD_A, when only that function is relevant.Product Highlights Wide, input ?3 dB bandwidth of 9 GHz supports direct radio frequency (RF) sampling of signals up to about 5 GHz. Four integrated, wideband decimation filters and NCO blocks supporting multiband receivers. Fast NCO switching enabled through the GPIO pins. SPI controls various product features and functions to meet specific system requirements. Programmable fast overrange detection and signal monitoring. On-chip temperature diode for system thermal management. 12 mm ? 12 mm, 196-ball BGA. Pin, package, feature, and memory map compatible with the AD9208 14-bit, 3.0 GSPS, JESD204B dual ADC.Applications Diversity multiband and multimode digital receivers 3G/4G, TD-SCDMA, W-CDMA, and GSM, LTE, LTE-A Electronic test and measurement systems Phased array radar and electronic warfare DOCSIS 3.0 CMTS upstream receive paths HFC digital reverse path receivers

AD9707-DPG2-EBZ

Analog Devices Inc.The AD9704/AD9705/AD9706/AD9707?are the fourth-generation family in the TxDAC series of high performance, CMOS digital-to-analog converters (DACs). This pin-compatible, 8-/10-/12-/14-bit resolution family is optimized for low power operation, while maintaining excellent dynamic performance. The AD9704/AD9705/AD9706/AD9707 family is pin-compatible with the AD9748/AD9740/AD9742/AD9744 family of TxDAC converters and is specifically optimized for the transmit signal path of communication systems. All of the devices share the same interface, LFCSP package, and pinout, providing an upward or downward component selection path based on performance, resolution, and cost. The AD9704/AD9705/AD9706/AD9707 offers exceptional ac and dc performance, while supporting update rates up to 175 MSPS.The flexible power supply operating range of 1.7 V to 3.6 V and low power dissipation of the AD9704/AD9705/AD9706/AD9707 parts make them well suited for portable and low power applications.Power dissipation of the AD9704/AD9705/AD9706/AD9707 can be reduced to 15 mW, with a small trade-off in performance, by lowering the full-scale current output. In addition, a power-down mode reduces the standby power dissipation to approximately 2.2 mW.The AD9704/AD9705/AD9706/AD9707 has an optional serial peripheral interface (SPI?) that provides a higher level of programmability to enhance performance of the DAC. An adjustable output, common-mode feature allows for easy interfacing to other components that require common modes from 0 V to 1.2 V.Edge-triggered input latches and a 1.0 V temperature-compensated band gap reference have been integrated to provide a complete, monolithic DAC solution. The digital inputs support 1.8 V and 3.3 V CMOS logic families.PRODUCT HIGHLIGHTS Pin Compatible. The AD9704/AD9705/AD9706/AD9707 line of TxDAC?converters is pin-compatible with theAD9748/AD9740/AD9742/AD9744 TxDAC line (LFCSP package). Low Power. Complete CMOS DAC operates on a single supply of 3.6 V down to 1.7 V, consuming 50 mW (3.3 V) and 12 mW (1.8 V). The DAC full-scale current can be reduced for lower power operation. Sleep and power-down modes are provided for low power idle periods. Self-Calibration. Self-calibration enables true 14-bit INL and DNL performance in the AD9707. Twos Complement/Binary Data Coding Support. Data input supports twos complement or straight binary data coding. Flexible Clock Input. A selectable high speed, single-ended,and differential CMOS clock input supports 175 MSPS conversion rate. Device Configuration. Device can be configured through pin strapping, and SPI control offers a higher level of programmability. Easy Interfacing to Other Components. Adjustable common-mode output allows for easy interfacing to other signal chain components that accept common-mode levels from 0 V to 1.2 V. On-Chip Voltage Reference. The AD9704/AD9705/AD9706/AD9707 include a 1.0 V temperature-compensated band gap voltage reference. Industry-Standard 32-Lead LFCSP Package.

AD9739A-EBZ

Analog Devices Inc.The AD9737A/AD9739A are 11-bit and 14-bit, 2.5 GSPS high performance RF DACs that are capable of synthesizing wideband signals from dc up to 3 GHz. The AD9737A/AD9739A are pin and functionally compatible with the AD9739 with the exception that the AD9737A/AD9739A do not support synchronization or RZ mode, and are specified to operate between 1.6 GSPS and 2.5 GSPS. By elimination of the synchronization circuitry, some nonideal artifacts such as images and discrete clock spurs remain stationary on the AD9737A/AD9739A between power-up cycles, thus allowing for possible system calibration. AC linearity and noise performance remain the same between the AD9739 and the AD9737A/AD9739A.The inclusion of on-chip controllers simplifies system integration. A dual-port, source synchronous, LVDS interface simplifies the digital interface with existing FGPA/ASIC technology. On-chip controllers are used to manage external and internal clock domain variations over temperature to ensure reliable data transfer from the host to the DAC core. A serial peripheral interface (SPI) is used for device configuration as well as readback of status registers.The AD9737A/AD9739A are manufactured on a 0.18 ?m CMOS process and operate from 1.8 V and 3.3 V supplies. They are supplied in a 160-ball chip scale ball grid array for reduced package parasitics.Product Highlights Ability to synthesize high quality wideband signals with bandwidths of up to 1.25 GHz in the first or second Nyquist zone. A proprietary quad-switch DAC architecture provides exceptional ac linearity performance while enabling mixmode operation. A dual-port, double data rate, LVDS interface supports the maximum conversion rate of 2500 MSPS. On-chip controllers manage external and internal clock domain skews. Programmable differential current output with an 8.66 mA to 31.66 mA range.Applications Broadband communications systems DOCSIS CMTS systems Military jammers Instrumentation, automatic test equipment Radar, avionics

AD9745-DPG2-EBZ

Analog Devices Inc.The AD9743/AD9745/AD976/AD9747 are pin-compatible, high dynamic range, dual digital-to-analog converters (DACs) with 10-/12-/14-/16-bit resolutions and sample rates of up to 250 MSPS. The devices include specific features for direct conversion transmit applications, including gain and offset compensation, and they interface seamlessly with analog quadrature modulators, such as the ADL5370.A proprietary, dynamic output architecture permits synthesis of analog outputs even above Nyquist by shifting energy away from the fundamental and into the image frequency.A serial peripheral interface (SPI) port provides full programmability. In addition, some pin-programmable features are offered for those applications without a controller.PRODUCT HIGHLIGHTS Low noise and intermodulation distortion (IMD) enables high quality synthesis of wideband signals. Proprietary switching output for enhanced dynamic performance. Programmable current outputs and dual auxiliary DACs provide flexibility and system enhancements.APPLICATIONS Wireless infrastructure: W-CDMA, CDMA2000, TD-SCDMA, WiMAX Wideband communications: LMDS/MMDS, point-to-point Instrumentation: Radio Frequency (RF) signal generators, arbitrary waveform generators

AD9764-EBZ

Analog Devices Inc.The AD9764 is the 14-bit resolution member of the TxDAC?series of high performance, low power CMOS digital-to-analogconverters (DACs). The TxDAC?; family, which consists of pincompatible 8-, 10-, 12-, and 14-bit DACs, is specificallyoptimized for the transmit signal path of communicationsystems. All of the devices share the same interface options,small outline package and pinout, providing an upward ordownward component selection path based on performance,resolution and cost. The AD9764 offers exceptional ac and dcperformance while supporting update rates up to 125 MSPS.The AD9764?s flexible single-supply operating range of 2.7 V to5.5 V and low power dissipation are well suited for portable andlow power applications. Its power dissipation can be furtherreduced to a mere 45 mW with a slight degradation in performanceby lowering the full-scale current output. Also, a power-downmode reduces the standby power dissipation to approximately25?mW.The AD9764 is manufactured on an advanced CMOS process.A segmented current source architecture is combined with aproprietary switching technique to reduce spurious componentsand enhance dynamic performance. Edge-triggered inputlatches and a 1.2 V temperature compensated bandgap referencehave been integrated to provide a complete monolithicDAC solution. Flexible supply options support +3 V and +5 VCMOS logic families.The AD9764 is a current-output DAC with a nominal full-scaleoutput current of 20 mA and >100 k? output impedance.Differential current outputs are provided to support single-endedor differential applications. Matching between the twocurrent outputs ensures enhanced dynamic performance in adifferential output configuration. The current outputs may betied directly to an output resistor to provide two complementary,single-ended voltage outputs or fed directly into a transformer.The output voltage compliance range is 1.25 V.The on-chip reference and control amplifier are configured formaximum accuracy and flexibility. The AD9764 can be drivenby the on-chip reference or by a variety of external referencevoltages. The internal control amplifier, which provides a wide(>10:1) adjustment span, allows the AD9764 full-scale currentto be adjusted over a 2 mA to 20 mA range while maintainingexcellent dynamic performance. Thus, the AD9764 may operateat reduced power levels or be adjusted over a 20 dB range toprovide additional gain ranging capabilities.The AD9764 is available in a 28-lead SOIC package. It isspecified for operation over the industrial temperature range.Product Highlights The AD9764 is a member of the TxDAC product family that provides an upward or downward component selection path based on resolution (8 to 14 bits), performance and cost. Manufactured on a CMOS process, the AD9764 uses a proprietary switching technique that enhances dynamic performance beyond that previously attainable by higher power/cost bipolar or BiCMOS devices. On-chip, edge-triggered input CMOS latches readily interface to +3 V and +5 V CMOS logic families. The AD9764 can support update rates up to 125 MSPS. A flexible single-supply operating range of 2.7 V to 5.5 V, and a wide full-scale current adjustment span of 2 mA to 20 mA, allows the AD9764 to operate at reduced power levels. The current output(s) of the AD9764 can be easily configured for various single-ended or differential circuit topologies.Applications Communication Transmit Channel: - Basestations - ADSL/HFC Modems Instrumentation