AD9520-1/PCBZ

Analog Devices Inc.The AD9520-11 provides a multioutput clock distributionfunction with subpicosecond jitter performance, along with anon-chip PLL and VCO. The on-chip VCO tunes from 2.27 GHzto 2.65 GHz. An external 3.3 V/5 V VCO/VCXO of up to 2.4 GHzcan also be used.The AD9520 serial interface supports both SPI and I2C? ports. An in-package EEPROM can be programmed through the serial interface and store user-defined register settings for power-up and chip reset.The AD9520 features 12 LVPECL outputs in four groups. Anyof the 1.6 GHz LVPECL outputs can be reconfigured as two250 MHz CMOS outputsEach group of outputs has a divider that allows both the divideratio (from 1 to 32) and the phase (coarse delay) to be set.The AD9520 is available in a 64-lead LFCSP and can be operatedfrom a single 3.3 V supply. The external VCO can have anoperating voltage up to 5.5 V. A separate output driver powersupply can be from 2.375 V to 3.465 VThe AD9520 is specified for operation over the standard industrialrange of ?40?C to +85?C.1The AD9520 is used throughout this data sheet to refer to all the members of the AD9520 family. However, when AD9520-1 is used, it is referring to that specificmember of the AD9520 family.ApplicationsLow jitter, low phase noise clock distributionClock generation and translation for SONET, 10Ge, 10G FC, and other 10 Gbps protocolsForward error correction (G.710)Clocking high speed ADCs, DACs, DDSs, DDCs, DUCs, MxFEsHigh performance wireless transceiversATE and high performance instrumentationBroadband infrastructures

AD9520-2/PCBZ

Analog Devices Inc.The AD9520-2 provides a multioutput clock distributionfunction with subpicosecond jitter performance, along with anon-chip PLL and VCO. The on-chip VCO tunes from 2.02 GHzto 2.335 GHz. An external 3.3 V/5 V VCO/VCXO of up to 2.4 GHzcan also be used.The AD9520-2 serial interface supports both SPI and I2C?ports.An in-package EEPROM, which can be programmed through theserial interface, can store user-defined register settings forpower-up and chip reset.The AD9520-2 features 12 LVPECL outputs in four groups. Anyof the 1.6 GHz LVPECL outputs can be reconfigured as two250 MHz CMOS outputs. If an application requires LVDSdrivers instead of LVPECL drivers, refer to the AD9522-2.Each group of three outputs has a divider that allows both thedivide ratio (from 1 to 32) and the phase offset or coarse timedelay to be set.The AD9520-2 is available in a 64-lead LFCSP and can be operatedfrom a single 3.3 V supply. The external VCO can have anoperating voltage of up to 5.5 V. A separate output driver powersupply can be from 2.375 V to 3.465 V.The AD9520-2 is specified for operation over the standardindustrial range of ?40?C to +85?C.Applications Low jitter, low phase noise clock distribution Clock generation and translation for SONET, 10Ge, 10GFC, Synchronous Ethernet, OTU2/3/4 Forward error correction (G.710) Clocking high speed ADCs, DACs, DDSs, DDCs, DUCs, MxFEs High performance wireless transceivers ATE and high performance instrumentation Broadband infrastructures

AD9520-3/PCBZ

Analog Devices Inc.The AD9520-31 provides a multioutput clock distribution function with subpicosecond jitter performance, along with an on-chip PLL and VCO. The on-chip VCO tunes from 1.72 GHz to 2.25 GHz. An external 3.3 V/5 V VCO/VCXO of up to 2.4 GHz can also be used.The AD9520 serial interface supports both SPI and I2C? ports. An in-package EEPROM can be programmed through the serial interface and store user-defined register settings for power-up and chip reset.The AD9520 features 12 LVPECL outputs in four groups. Any of the 1.6 GHz LVPECL outputs can be reconfigured as two 250 MHz CMOS outputs.Each group of outputs has a divider that allows both the divide ratio (from 1 to 32) and the phase (coarse delay) to be set.The AD9520 is available in a 64-lead LFCSP and can be operated from a single 3.3 V supply. The external VCO can have an operating voltage up to 5.5 V. A separate output driver power supply can be from 2.375 V to 3.465 V.The AD9520 is specified for operation over the standard industrial range of ?40?C to +85?C.1The AD9520 is used throughout this data sheet to refer to all the members of the AD9520 family. However, when AD9520-3 is used, it is referring to that specific member of the AD9520 family.Applications Low jitter, low phase noise clock distribution Clock generation and translation for SONET, 10Ge, 10G FC, and other 10 Gbps protocols Forward error correction (G.710) Clocking high speed ADCs, DACs, DDSs, DDCs, DUCs, MxFEs High performance wireless transceivers ATE and high performance instrumentation Broadband infrastructures

AD9522-1/PCBZ

Analog Devices Inc.The AD9522-11 provides a multioutput clock distribution function with subpicosecond jitter performance, along with an on-chip PLL and VCO. The on-chip VCO tunes from 2.27 GHz to 2.65 GHz. An external 3.3 V/5 V VCO/VCXO of up to 2.4 GHz can also be used.The AD9522 serial interface supports both SPI and I2C? ports. An in-package EEPROM can be programmed through the serial interface and store user-defined register settings for power-up and chip reset.The AD9522 features 12 LVDS outputs in four groups. Any of the 800 MHz LVDS outputs can be reconfigured as two 250 MHz CMOS outputs.Each group of outputs has a divider that allows both the divide ratio (from 1 to 32) and the phase (coarse delay) to be set.The AD9522 is available in a 64-lead LFCSP and can be operated from a single 3.3 V supply. The external VCO can have an operating voltage up to 5.5 V.The AD9522 is specified for operation over the standard industrial range of ?40?C to +85?C.The AD9520-1 is an equivalent part to the AD9522-1 featuring LVPECL/CMOS drivers instead of LVDS/CMOS drivers.1The AD9522 is used throughout this data sheet to refer to all the members of the AD9522 family. However, when AD9522-1 is used, it is referring to that specific member of the AD9522 family.ApplicationsLow jitter, low phase noise clock distributionClock generation and translation for SONET, 10Ge, 10G FC, and other 10 Gbps protocolsForward error correction (G.710)Clocking high speed ADCs, DACs, DDSs, DDCs, DUCs, MxFEsHigh performance wireless transceiversATE and high performance instrumentationBroadband infrastructures

AD9523-1/PCBZ

Analog Devices Inc.The AD9523-1 provides a low power, multi-output, clock distribution function with low jitter performance, along with an on-chip PLL and VCO with two VCO dividers. The on-chip VCO tunes from 2.94 GHz to 3.1 GHz.The AD9523-1 is designed to support the clock requirements for long term evolution (LTE) and multicarrier GSM base station designs. It relies on an external VCXO to provide the reference jitter cleanup to achieve the restrictive low phase noise requirements necessary for acceptable data converter SNR performance.The input receivers, oscillator, and zero delay receiver provide both single-ended and differential operation. When connected to a recovered system reference clock and a VCXO, the device generates 14 low noise outputs with a range of 1 MHz to 1 GHz, and one dedicated buffered output from the input PLL (PLL1). The frequency and phase of one clock output relative to another clock output can be varied by means of a divider phase select function that serves as a jitter-free, coarse timing adjustment in increments that are equal to half the period of the signal coming out of the VCO.An in-package EEPROM can be programmed through the serial interface to store user-defined register settings for power-up and chip reset.APPLICATIONS LTE and multicarrier GSM base stations Wireless and broadband infrastructure Medical instrumentation Clocking high speed ADCs, DACs, DDSs, DDCs, DUCs, MxFEs Low jitter, low phase noise clock distribution Clock generation and translation for SONET, 10Ge, 10G FC, and other 10 Gbps protocols Forward error correction (G.710) High performance wireless transceivers ATE and high performance instrumentation

AD9544/PCBZ

Analog Devices Inc.The 10 clock outputs of the AD9544 are synchronized to any one of up to four input references. The digital phase-locked loops (DPLLs) reduce timing jitter associated with the external references. The digitally controlled loop and holdover circuitry continuously generate a low jitter output signal, even when all reference inputs fail.The AD9544 is available in a 48-lead LFCSP (7 mm ? 7 mm) package and operates over the ?40?C to +85?C temperature range.Note that throughout this data sheet, multifunction pins, such as SDO/M5, are referred to either by the entire pin name or by a single function of the pin, for example, M5, when only that function is relevant.Appliations SyncE and GPS synchronization and jitter cleanup Optical transport networks (OTN), SDH, and macro and small cell base stations OTN mapping/demapping with jitter cleaning Small base station clocking, including baseband and radio Stratum 2, Stratum 3e, and Stratum 3 holdover, jitter cleanup, and phase transient control JESD204B support for analog-to-digital converter (ADC) and digital-to-analog converter (DAC) clocking Cable infrastructures Carrier Ethernet

AD9546/PCBZ

Analog Devices Inc.The AD9546 incorporates digitized clocking technology that efficiently transports and distributes clock signals in systems. Digitized clocking allows the design of flexible and scalable clock transport systems with well controlled phase (time) alignment. These characteristics make the AD9546 a leading choice for the design of network equipment that must meet the synchronization requirements for IEEE? 1588? boundary clocks per ITU-T G.8273.2 Class D. Digitized clocking is also relevant in applications requiring the accurate transport of frequency and phase to multiple usage endpoints (for example, distributing synchronized system reference (SYSREF) clocks to an array of ADC channels). The AD9546 supports existing and emerging International Telecommunications Union (ITU) standards for the delivery of frequency, phase, and time of day over service provider packet networks (ITU-T G.8262, ITU-T G.812, ITU-T G.813, ITU-T G.823, ITU-T G.824, ITU-T G.825, and ITU-T G.8273.2). The 10 clock outputs of the AD9546 synchronize to any one of up to eight input references. The digital phase-locked loops (DPLLs) reduce timing jitter associated with the external references, and the analog phase-locked loops (APLLs) provide frequency translation with low jitter output clocks. The digitally controlled loop and holdover circuitry continuously generate a low jitter output signal, even when all reference inputs fail. The AD9546 is available in a 48-lead LFCSP (7 mm ? 7 mm) package and operates over the ?40?C to +85?C temperature range. Throughout this data sheet, a single function of a multifunction pin name may be referenced when only that function is relevant (for example, M5 for SDO/M5). APPLICATIONS5G timing transport high precision synchronization Global positioning system (GPS), precision time protocol (PTP) (IEEE 1588), and synchronous Ethernet (SyncE) jitter cleanup and synchronization Optical transport networks (OTN), synchronous digital hierarchy (SDH), and macro and small cell base stations Small base station clocking (baseband and radio) Stratum 2, Stratum 3e, and Stratum 3 holdover, jitter cleanup, and phase transient control JESD204B support for analog-to-digital converter (ADC) and digital-to-analog converter (DAC) clocking Carrier Ethernet

AD9559/PCBZ

Analog Devices Inc.The AD9559 is a low loop bandwidth clock multiplier that provides jitter cleanup and synchronization for many systems, including synchronous optical networks (SONET/SDH). The AD9559 generates an output clock synchronized to up to four external input references. The digital PLL allows for reduction of input time jitter or phase noise associated with the external references. The digitally controlled loop and holdover circuitry of the AD9559 continuously generates a low jitter output clock even when all reference inputs have failed.The AD9559 operates over an industrial temperature range of ?40?C to +85?C. If a single DPLL version of this part is needed, refer to the AD9557.APPLICATIONS Network synchronization, including Synchronous Ethernet and OTN mapping/de-mapping Cleanup of reference clock jitter SONET/SDH clocks up to OC-192, including FEC Stratum 3 holdover, jitter cleanup, and phase transient control Wireless base station controllers Cable infrastructure Data communications

AD9572-EVALZ-PEC

Analog Devices Inc.The AD9572 provides a multioutput clock generator function along with two on-chip PLL cores, optimized for fiber channel line card applications that include an Ethernet interface. The integer-N PLL design is based on the Analog Devices, Inc., proven portfolio of high performance, low jitter frequencysynthesizers to maximize network performance. Other applications with demanding phase noise and jitter requirements also benefit from this part. The PLL section consists of a low noise phase frequency detector (PFD), a precision charge pump (CP), a low phase noise voltage controlled oscillator (VCO), and a preprogrammed feedback divider and output divider. By connecting an external crystal or reference clock to the REFCLK pin, frequencies up to 156.25 MHz can be locked to the input reference. Each output divider and feedback divider ratio is preprogrammed for therequired output rates. A second PLL also operates as an integer-N synthesizer anddrives two LVPECL or LVDS output buffers for 106.25 MHzoperation. No external loop filter components are required, thusconserving valuable design time and board space. The AD9572 is available in a 40-lead, 6 mm ? 6 mm lead framechip scale package (LFCSP) and can be operated from a single3.3 V supply. The temperature range is ?40?C to +85?C.APPLICATIONSFiber channel line cards, switches, and routersGigabit Ethernet/PCIe support included Low jitter, low phase noise clock generation

AD9609-20EBZ

Analog Devices Inc.The AD9609 is a monolithic, single channel 1.8 V supply, 10-bit,20/40/65/80 MSPS analog-to-digital converter (ADC). It featuresa high performance sample-and-hold circuit and on-chip voltagereference.The product uses multistage differential pipeline architecturewith output error correction logic to provide 10-bit accuracy at80 MSPS data rates and to guarantee no missing codes over thefull operating temperature range.The ADC contains several features designed to maximize flexibilityand minimize system cost, such as programmable clock and dataalignment and programmable digital test pattern generation. Theavailable digital test patterns include built-in deterministic andpseudorandom patterns, along with custom user-defined testpatterns entered via the serial port interface (SPI).A differential clock input with selectable internal 1 to 8 divide ratiocontrols all internal conversion cycles. An optional duty cyclestabilizer (DCS) compensates for wide variations in the clock dutycycle while maintaining excellent overall ADC performance.The digital output data is presented in offset binary, gray code, ortwos complement format. A data output clock (DCO) is providedto ensure proper latch timing with receiving logic. Both 1.8 V and3.3 V CMOS levels are supported.The AD9609 is available in a 32-lead RoHS-compliant LFCSPand is specified over the industrial temperature range (?40?Cto +85?C).APPLICATIONS Communications Diversity radio systems Multimode digital receivers GSM, EDGE, W-CDMA, LTE, CDMA2000, WiMAX, TD-SCDMA Smart antenna systems Battery-powered instruments Handheld scope meters Portable medical imaging Ultrasound Radar/LIDAR PET/SPECT imagingPRODUCT HIGHLIGHTS1. The AD9609 operates from a single 1.8 V analog powersupply and features a separate digital output driver supplyto accommodate 1.8 V to 3.3 V logic families.2. The sample-and-hold circuit maintains excellent performancefor input frequencies up to 200 MHz and is designed for lowcost, low power, and ease of use.3. A standard serial port interface supports various productfeatures and functions, such as data output formatting,internal clock divider, power-down, DCO and data output(D9 to D0) timing and offset adjustments, and voltagereference modes.4. The AD9609 is packaged in a 32-lead RoHS compliantLFCSP that is pin compatible with the AD9629 12-bit ADCand the AD9649 14-bit ADC, enabling a simple migrationpath between 10-bit and 14-bit converters sampling from20 MSPS to 80 MSPS.

AD9625-2.0EBZ

Analog Devices Inc.The AD9625 is a 12-bit monolithic sampling analog-to-digital converter (ADC) that operates at conversion rates of up to 2.6 giga samples per second (GSPS). This product is designed for sampling wide bandwidth analog signals up to the second Nyquist zone. The combination of wide input bandwidth, high sampling rate, and excellent linearity of the AD9625 is ideally suited for spectrum analyzers, data acquisition systems, and a wide assortment of military electronics applications, such as radar and jamming/antijamming measures.The analog input, clock, and SYSREF? signals are differential inputs. The JESD204B-based high speed serialized output is configurable in a variety of one-, two-, four-, six-, or eight-lane configurations. The product is specified over the industrial temperature range of ?40?C to +85?C.PRODUCT HIGHLIGHTS High performance: exceptional SFDR in high sample rate applications, direct RF sampling, and on-chip reference. Flexible digital data output formats based on the JESD204B specification. Control path SPI interface port that supports various product features and functions, such as data formatting, gain, and offset calibration values.APPLICATIONS Spectrum analyzers Military communications Radar High performance digital storage oscilloscopes Active jamming/antijamming Electronic surveillance and countermeasures

AD9625-2.6EBZ

Analog Devices Inc.The AD9625 is a 12-bit monolithic sampling analog-to-digital converter (ADC) that operates at conversion rates of up to 2.6 giga samples per second (GSPS). This product is designed for sampling wide bandwidth analog signals up to the second Nyquist zone. The combination of wide input bandwidth, high sampling rate, and excellent linearity of the AD9625 is ideally suited for spectrum analyzers, data acquisition systems, and a wide assortment of military electronics applications, such as radar and jamming/antijamming measures.The analog input, clock, and SYSREF? signals are differential inputs. The JESD204B-based high speed serialized output is configurable in a variety of one-, two-, four-, six-, or eight-lane configurations. The product is specified over the industrial temperature range of ?40?C to +85?C.PRODUCT HIGHLIGHTS High performance: exceptional SFDR in high sample rate applications, direct RF sampling, and on-chip reference. Flexible digital data output formats based on the JESD204B specification. Control path SPI interface port that supports various product features and functions, such as data formatting, gain, and offset calibration values.APPLICATIONS Spectrum analyzers Military communications Radar High performance digital storage oscilloscopes Active jamming/antijamming Electronic surveillance and countermeasures

AD9635-125EBZ

Analog Devices Inc.The AD9635 is a dual, 12-bit, 80 MSPS/125 MSPS analog-to-digital converter (ADC) with an on-chip sample-and-hold circuit designed for low cost, low power, small size, and ease of use. The product operates at a conversion rate of up to 125 MSPS and is optimized for outstanding dynamic performance and low power in applications where a small package size is critical.The ADC requires a single 1.8 V power supply and LVPECL-/ CMOS-/LVDS-compatible sample rate clock for full performanceoperation. No external reference or driver components arerequired for many applications.The ADC automatically multiplies the sample rate clock for theappropriate LVDS serial data rate. A data clock output (DCO) for capturing data on the output and a frame clock output (FCO) forsignaling a new output byte are provided. Individual channelpower-down is supported; the AD9635 typically consumes lessthan 2 mW in the full power-down state. The ADC providesseveral features designed to maximize flexibility and minimize system cost, such as programmable output clock and data alignment and digital test pattern generation. The available digital test patterns include built-in deterministic and pseudorandom patterns, along with custom user-defined test patterns entered via the serial port interface (SPI).The AD9635 is available in a RoHS-compliant, 32-lead LFCSP. It is specified over the industrial temperature range of ?40?Cto +85?C. PRODUCT HIGHLIGHTS Small Footprint. Two ADCs are contained in a small, spacesaving package. Low Power. The AD9635 uses 115 mW/channel at 125 MSPS with scalable power options. Pin Compatibility with the AD9645, a 14-Bit Dual ADC. Ease of Use. A data clock output (DCO) operates at frequencies of up to 500 MHz and supports double data rate (DDR) operation. User Flexibility. The SPI control offers a wide range of flexible features to meet specific system requirements. APPLICATIONS Communications Diversity radio systems Multimode digital receivers GSM, EDGE, W-CDMA, LTE, CDMA2000, WiMAX, TD-SCDMA I/Q demodulation systems Smart antenna systems Broadband data applications Battery-powered instruments Hand held scope meters Portable medical imaging and ultrasound Radar/LIDAR

LTM9002-LA | 12-Bit, 65Msps, DC-25MHz LPF, 8dB/20dB Gain, No Trim DAC (Requires DC890)

Analog Devices Inc.DC1298A-LA: Demo Board for the LTM9002-LA 12-Bit, 65Msps Dual-Channel IF/Baseband Receiver Subsystem

LTC6421CUD-20 | Dual Matched 1.3GHz Differential Amplifiers/ADC Drivers

Analog Devices Inc.DC1299A-B: Demo Board for the LTC6421-20 Dual Matched 1.3GHz Differential Amplifiers/ADC Drivers

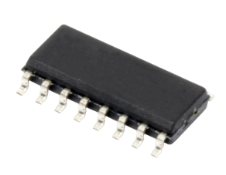

DC1300A-C

Analog Devices Inc.The LTC3726 is a secondary-side controller for synchronous forward converters. When used in conjunction with the LTC3705/LTC3725 gate driver and primary-side controllers, the part creates a complete isolated power supply that combines the simplicity of OPTI-LOOP? compensation with the speed of secondary-side control.The LTC3726 has been designed to simplify the design of highly efficient, secondary-side forward converters. Working in concert with the LTC3705 or LTC 3725, the LTC3726 forms a robust, self-starting converter that eliminates the need for the separate bias regulator that is commonly used in secondary-side control applications. In addition, a proprietary scheme is used to multiplex gate drive signals and DC bias power across the isolation barrier through a single, tiny pulse transformer.The LTC3726 is available in a 16-lead SSOP package.Applications Isolated 48V Telecommunication Systems Internet Servers and Routers Distributed Power Step-Down Converters Automotive and Heavy Equipment

DC1310A

Analog Devices Inc.The LTC3612 is a low quiescent current monolithic synchronous buck regulator using a current mode, constant frequency architecture. The no-load DC supply current in sleep mode is only 70?A while maintaining the output voltage (Burst Mode operation) at no load, dropping to zero current in shutdown. The 2.25V to 5.5V input supply voltage range makes the LTC3612 ideally suited for single Li-Ion as well as fixed low voltage input applications. 100% duty cycle capability provides low dropout operation, extending the operating time in battery-powered systems.The operating frequency is externally programmable up to 4MHz, allowing the use of small surface mount inductors. For switching noise-sensitive applications, the LTC3612 can be synchronized to an external clock at up to 4MHz.Forced continuous mode operation in the LTC3612 reduces noise and RF interference. Adjustable compensation allows the transient response to be optimized over a wide range of loads and output capacitors.The internal synchronous switch increases efficiency and eliminates the need for an external catch diode, saving external components and board space. The LTC3612 is offered in a leadless 20-pin 3mm ? 4mm QFN or a thermally enhanced 20-pin TSSOP package.APPLICATIONS Point-of-Load Supplies Distributed Power Supplies Portable Computer Systems DDR Memory Termination Handheld Devices

LTC3805 Isolated Demo Board | Flyback Controller, 18V ≤ VIN ≤ 72V, VOUT = 3.3V @ 3A

Analog Devices Inc.Demonstration circuit 1311 is a Telecom isolated DC/DC converter featuring the LTC3805/-5 constant frequency current mode flyback controller. The DC1311 converts 18V to 72V input voltage to an isolated 3A of output current at 3.3V. The 300kHz constant frequency operation is maintained down to very light load to reduce low frequency noise generated over a wide range of load current. The converter provides high output voltage accuracy (typically ±2%) over wide load range with no minimum load requirement.

The DC1311 also provides non-isolated design by removing opto coupler and LTC4430 circuit. The demonstration circuit can be easily modified to generate different output voltages up to 15V. As output voltage is increased, the maximum output current must be reduced to limit the output power to no more than 10W.

LT1913EDD | 36V, 3.5A, 2.4MHz Step-Down Switching Regulator

Analog Devices Inc.DC1316A: Demo Board for LT1913 25V, 3.5A, 2.4MHz Step-Down Switching Regulator.

DC1317A-C

Analog Devices Inc.The LT1952/LT1952-1 are current mode PWM controllers optimized to control the forward converter topology, using one primary MOSFET. The LT1952/LT1952-1 provide synchronous rectifier control, resulting in extremely high efficiency. A programmable Volt-Second clamp provides a safeguard for transformer reset that prevents saturation. This allows a single MOSFET on the primary side to reliably run at greater than 50% duty cycle for high MOSFET, transformer and rectifier utilization. The devices include soft-start for controlled exit from shutdown and undervoltage lockout. A precision 107mV current limit threshold, independent of duty cycle, combines with softstart to provide hiccup short circuit protection. The LT1952 is optimized for micropower bootstrap startup from high input voltages. The LT1952-1 allows startup from lower input voltages. Programmable slope compensation and leading edge blanking allow optimization of loop bandwidth with a wide range of inductors and MOSFETs. Each device can be programmed over a 100kHz to 500kHz frequency range and the part can be synchronized to an external clock. The error amplifier is a true op amp, allowing a wide range of compensation networks. The LT1952/LT1952-1 are available in a small 16-pin SSOP package.Applications Telecommunications Power Supplies Industrial and Distributed Power Isolated and Non-Isolated DC/DC Converters