EVAL-AD5172SDZ

Analog Devices Inc.The AD5172 / AD5173?are dual-channel, 256-position, one-time programmable (OTP) digital potentiometers that employ fuse link technology to achieve memory retention of resistance settings. The digital potentiometer, VR, and RDAC terms are used interchangeably. OTP is a cost-effective alternative to EEMEM for users who do not need to program the digital potentiometer setting in memory more than once. These devices perform the same electronic adjustment function as mechanical potentiometers or variable resistors but with enhanced resolution, solid-state reliability, and superior low temperature coefficient performance.TheAD5172 / AD5173 are programmed using a 2-wire, I2C-compatible digital interface. Unlimited adjustments are allowed before permanently setting the resistance value. During OTP activation, a permanent blow fuse command freezes the wiper position (analogous to placing epoxy on a mechanical trimmer).Unlike traditional OTP digital potentiometers, the AD5172 / AD5173 have a unique temporary OTP overwrite feature that allows for new adjustments even after a fuse is blown. However, the OTP setting is restored during subsequent power-up conditions. This allows users to treat these digital potentiometers as volatile potentiometers with a programmable preset.APPLICATIONS Systems calibration Electronics level setting Mechanical trimmers replacement in new designs Permanent factory PCB setting Transducer adjustment of pressure, temperature, position, chemical, and optical sensors RF amplifier biasing Gain control and offset adjustment

EVAL-AD7766EDZ

Analog Devices Inc.The AD7766/AD7766-1/AD7766-2 are high performance,24-bit, oversampled SAR analog-to-digital converters (ADCs).The AD7766/AD7766-1/AD7766-2 combine the benefits of alarge dynamic range and input bandwidth, consuming 15 mW,10.5 mW, and 8.5 mW power, respectively, and are contained ina 16-lead TSSOP package.Ideal for ultralow power data acquisition (such as PCI- and USBbasedsystems), the AD7766/AD7766-1/AD7766-2 provide 24-bitresolution. The combination of exceptional SNR, wide dynamicrange, and outstanding dc accuracy make the AD7766/AD7766-1/AD7766-2 ideally suited for measuring small signal changes over awide dynamic range. This is particularly suitable for applicationswhere small changes on the input are measured on larger ac ordc signals. In such an application, the AD7766/AD7766-1/AD7766-2 accurately gather both ac and dc information.The AD7766/AD7766-1/AD7766-2 include an on-board digitalfilter (complete with linear phase response) that acts to eliminateout-of-band noise by filtering the oversampled input voltage.The oversampled architecture also reduces front-end antialiasrequirements. Other features of the AD7766/AD7766-1/AD7766-2include a SYNC/PD (synchronization/power-down) pin, allowingthe synchronization of multiple AD7766/AD7766-1/AD7766-2devices. The addition of an SDI pin provides the option of daisychaining multiple AD7766/AD7766-1/AD7766-2 devices.The AD7766/AD7766-1/AD7766-2 operate from a 2.5 V supplyusing a 5 V reference. The devices operate from ?40?C to +105?C. Applications Low power PCI/USB data acquisition systems Low power wireless acquisition systems Vibration analysis Instrumentation High precision medical acquisition

EVAL-AD7262EDZ

Analog Devices Inc.The AD7262/AD7262-5 are dual, 12-bit, high speed, low power, successive approximation ADCs that operate from a single 5 V power supply. The AD7262 features throughput rates of up to 1 MSPS per on-chip ADC. The AD7262-5 features throughput rates of up to 500 kSPS. Two complete ADC functions allow simultaneous sampling and conversion of two channels. Each ADC is preceded by a true differential analog input with a PGA. There are 14 gain settings available: ?1, ?2, ?3, ?4, ?6, ?8, ?12, ?16, ?24, ?32, ?48, ?64, ?96, and ?128.The AD7262/AD7262-5 contain four comparators. Comparator A and Comparator B are optimized for low power, while Comparator C and Comparator D have fast propagation delays. The AD7262/AD7262-5 feature a calibration function to remove any device offset error and programmable gain adjust registers to allow for input path (for example, sensor) offset and gain compensation. The AD7262/AD7262-5 have an on-chip 2.5 V reference that can be disabled if an external reference is preferred.The AD7262/AD7262-5 are ideally suited for monitoring small amplitude signals from a variety of sensors. They include all the functionality needed for monitoring the position feedback signals from a variety of analog encoders used in motor control systems.Product Highlights Integrated PGA with a variety of flexible gain settings to allow detection and conversion of low level analog signals. Each PGA is followed by a dual simultaneous sampling ADC, featuring throughput rates of 1 MSPS per ADC for the AD7262. The conversion results of both ADCs are simultaneously available on separate data lines or in succession on one data line if only one serial port is available. Four integrated comparators that can be used to count signals from pole sensors in motor control applications. Internal 2.5 V reference.

EVAL-AD7793EBZ

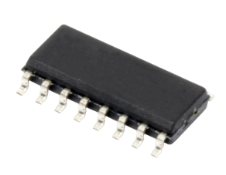

Analog Devices Inc.The?AD7792/AD7793 are low power, low noise, complete analog front ends for high precision measurement applications. The AD7792/AD7793 contain a low noise 16-/24-bit ?-? ADC with three differential analog inputs. The on-chip, low noise instrumentation amplifier means that signals of small amplitude can be interfaced directly to the ADC. With a gain setting of 64, the rms noise is 40 nV when the update rate equals 4.17 Hz.The devices contain a precision low noise, low drift internal band gap reference and can accept an external differential reference. Other on-chip features include programmable excitation current sources, burnout currents, and a bias voltage generator. The bias voltage generator sets the common-mode voltage of a channel to AVDD/2The devices can be operated with either the internal clock or an external clock. The output data rate from the parts is software-programmable and can be varied from 4.17 Hz to 470 Hz.The parts operate with a power supply from 2.7 V to 5.25 V. They consume a current of 400 ?A typical and are housed in a 16-lead TSSOP package.Applications Thermocouple measurements RTD measurements Thermistor measurements Gas analysis Industrial process control Instrumentation Portable instrumentation Blood analysis Smart transmitters Liquid/gas chromatography 6-digit DVM

128159-HMC822LP6CE

Analog Devices Inc.The HMC822LP6CE is a fully functioned Fractional-N Phase-Locked-Loop (PLL) Frequency Synthesizer with an Integrated Voltage Controlled Oscillator (VCO). The synthesizer consists of an integrated low noise VCO with a triband output, an autocalibration subsystem for low voltage VCO tuning, a very low noise digital Phase Detector (PD), a precision controlled charge pump, a low noise reference path divider and a fractional divider.The fractional synthesizer features an advanced delta-sigma modulator design that allows both ultra-fine step sizes and low spurious products. The phase detector (PD) features cycle slip prevention (CSP) technology to allow faster frequency hopping times. Ultra low in-close phase noise and low spurious also allows wider loop bandwidths for faster frequency hopping and low micro-phonics.For theory of operation and register map refer to the 'PLLs with Integrated VCO - RF VCOs' Operating Guide.Applications Cellular/4G Infrastructure Repeaters and Femtocells Communications Test Equipment CATV Equipment Phased Array Applications DDS Replacement? Very High Data Rate Radios

129538-HMC974LC3C

Analog Devices Inc.The HMC974LC3C is a silicon germanium (SiGe) monolithic, ultra fast window comparator that features reduced swing positive emitter-coupled logic (RSPECL) output drivers that are level latched. Three output ports detect whether an analog input signal is above, below, or between two reference levels supplied at the input.The outputs are single-ended negative logic. Incorporating two proven comparators at the input provides good dc and dynamic matching and reduces the input capacitance. The reduced swingoutput stages are designed to directly drive 400 mV into 50 ? terminated to a voltage (VTERM = VCCO ? 2 V).HMC974LC3C features high speed latches that can either be enabled to latch the output data or left in the track mode toimplement a tracking window comparator.Applications Automatic test equipment (ATE) High speed instrumentation Clock and data restoration Semiconductor test systems Threshold detection in electronic warfare systems

AD8337-EVALZ

Analog Devices Inc.The AD8337 is a low noise, single-ended, linear-in-dB, general-purpose variable gain amplifier (VGA) usable at frequencies from dc to 100 MHz; the ?3 dB bandwidth is 280 MHz. Excellent bandwidth uniformity across the entire gain range and low output-referred noise makes the AD8337 ideal for gain trim applications and for driving high speed analog-to-digital converters (ADCs).Excellent dc characteristics combined with high speed make the AD8337 particularly suited for industrial ultrasound, PET scanners, and video applications. Dual-supply operation enables gain control of negative-going pulses such as generated by photodiodes or photomultiplier tubes.The AD8337 uses the popular and versatile X-AMP? architecture, exclusively from Analog Devices, Inc., with a gain range of 24 dB. The gain control interface provides precise linear-in-dB scaling of 19.7 dB/V, referenced to VCOM.The AD8337 includes an uncommitted operational current-feedback preamplifier (PrA) that operates in inverting or noninverting configurations. Using external resistors, the device can be configured for gains of 6 dB or greater. The AD8337 is characterized by a noninverting PrA gain of 2? using two external 100 ? resistors. The attenuator has a range of 24 dB, and the output amplifier has a fixed gain of 8? (18.06 dB). The lowest nominal gain range is 0 dB to 24 dB and can be shifted up or down by adjusting the preamp gain. Multiple AD8337s can be connected in series for larger gain ranges, and for interstage filtering to suppress noise and distortion, and for nulling offset voltages.The operating temperature range is ?40?C to +85?C, and it is available in an 8-lead, 3 mm ? 3 mm LFCSP.Applications Gain trim PET scanners High performance AGC systems I/Q signal processing Video Industrial and medical ultrasound Radar receivers

AD9250-250EBZ

Analog Devices Inc.The AD9250 is a dual, 14-bit ADC with sampling speeds of up to 250 MSPS. The AD9250 is designed to support communications applications where low cost, small size, wide bandwidth, and versatility are desired.The ADC cores feature a multistage, differential pipelined architecture with integrated output error correction logic. The ADC cores feature wide bandwidth inputs supporting a variety of user-selectable input ranges. An integrated voltage reference eases design considerations. A duty cycle stabilizer is provided to compensate for variations in the ADC clock duty cycle, allowing the converters to maintain excellent performance. The JESD204B high speed serial interface reduces board routing requirements and lowers pin count requirements for the receiving device.By default, the ADC output data is routed directly to the two JESD204B serial output lanes. These outputs are at CML voltage levels. Four modes support any combination of M = 1 or 2 (single or dual converters) and L = 1 or 2 (one or two lanes). For dual ADC mode, data can be sent through two lanes at the maximum sampling rate of 250 MSPS. However, if data is sent through one lane, a sampling rate of up to 125 MSPS is supported. Synchronization inputs (SYNCINB? and SYSREF?) are provided.Flexible power-down options allow significant power savings, when desired. Programmable overrange level detection is supported for each channel via the dedicated fast detect pins.Programming for setup and control are accomplished using a 3-wire SPI-compatible serial interface.The AD9250 is available in a 48-lead LFCSP and is specified over the industrial temperature range of ?40?C to +85?C.Product Highlights Integrated dual, 14-bit, 170 MSPS/250 MSPS ADC. The configurable JESD204B output block supports up to 5 Gbps per lane. An on-chip, phase-locked loop (PLL) allows users to provide a single ADC sampling clock; the PLL multiplies the ADC sampling clock to produce the corresponding JESD204B data rate clock. Support for an optional RF clock input to ease system board design. Proprietary differential input maintains excellent SNR performance for input frequencies of up to 400 MHz. Operation from a single 1.8 V power supply. Standard serial port interface (SPI) that supports various product features and functions such as controlling the clock DCS, power-down, test modes, voltage reference mode, over range fast detection, and serial output configuration.Applications Diversity radio systems Multimode digital receivers (3G) TD-SCDMA, WiMAX, W-CDMA, CDMA2000, GSM, EDGE, LTE DOCSIS 3.0 CMTS upstream receive paths HFC digital reverse path receivers I/Q demodulation systems Smart antenna systems Electronic test and measurement equipment Radar receivers COMSEC radio architectures IED detection/jamming systems General-purpose software radios Broadband data applications

AD9251-65EBZ

Analog Devices Inc.The AD9251 is a monolithic, dual-channel, 1.8 V supply, 14-bit, 20 MSPS/40 MSPS/65 MSPS/80 MSPS analog-to-digital converter (ADC). It features a high performance sample-and hold circuit and on-chip voltage reference.The product uses multistage differential pipeline architecture with output error correction logic to provide 14-bit accuracy at80 MSPS data rates and to guarantee no missing codes over the full operating temperature range.The ADC contains several features designed to maximize flexibility and minimize system cost, such as programmable clock and data alignment and programmable digital test pattern generation. The available digital test patterns include built-in deterministic and pseudorandom patterns, along with custom user-defined test patterns entered via the serial port interface (SPI).A differential clock input controls all internal conversion cycles. An optional duty cycle stabilizer (DCS) compensates for wide variations in the clock duty cycle while maintaining excellent overall ADC performance.The digital output data is presented in offset binary, gray code, or twos complement format. A data output clock (DCO) is provided for each ADC channel to ensure proper latch timing with receiving logic. Both 1.8 V and 3.3 V CMOS levels are supported and output data can be multiplexed onto a single output bus.The AD9251 is available in a 64-lead RoHS Compliant LFCSP and is specified over the industrial temperature range (?40?C to +85?C).PRODUCT HIGHLIGHTS The AD9251 operates from a single 1.8 V analog power supply and features a separate digital output driver supply to accommodate 1.8 V to 3.3 V logic families. The patented sample-and-hold circuit maintains excellent performance for input frequencies up to 200 MHz and is designed for low cost, low power, and ease of use. A standard serial port interface supports various product features and functions, such as data output formatting, internal clock divider, power-down, DCO/DATA timing and offset adjustments, and voltage reference modes. The AD9251 is packaged in a 64-lead RoHS compliant LFCSP that is pin compatible with the AD9268 16-bit ADC, the AD9258 14-bit ADC, the AD9231 12-bit ADC, and the AD9204 10-bit ADC, enabling a simple migration path between 10-bit and 16-bit converters sampling from 20 MSPS to 125 MSPS.?APPLICATIONS Communications Diversity radio systems Multimode digital receivers GSM, EDGE, W-CDMA, LTE, CDMA2000, WiMAX, TD-SCDMA I/Q demodulation systems Smart antenna systems Battery-powered instruments Hand held scope meters Portable medical imaging Ultrasound Radar/LIDAR

AD9255-105EBZ

Analog Devices Inc.The AD9255 is a 14-bit, 125 MSPS analog-to-digital converter (ADC). The AD9255 is designed to support communications applications where high performance combined with low cost, small size, and versatility is desired.The ADC core features a multistage, differential pipelined architecture with integrated output error correction logic to provide 14-bit accuracy at 125 MSPS data rates and guarantees no missing codes over the full operating temperature range.The ADC features a wide bandwidth differential sample-and-hold analog input amplifier supporting a variety of user-selectable input ranges. It is suitable for multiplexed systems that switch full-scale voltage levels in successive channels and for sampling single-channel inputs at frequencies well beyond the Nyquist rate. Combined with power and cost savings over previously available ADCs, the AD9255 is suitable for applications in communications, instrumentation, and medical imaging.A differential clock input controls all internal conversion cycles. A duty cycle stabilizer provides the means to compensate for variations in the ADC clock duty cycle, allowing the converters to maintain excellent performance over a wide range of input clock duty cycles. An integrated voltage reference eases design considerations.The ADC output data format is either parallel 1.8 V CMOS or LVDS (DDR). A data output clock is provided to ensure proper latch timing with receiving logic.Programming for setup and control is accomplished using a 3-wire SPI-compatible serial interface. Flexible power-down options allow significant power savings, when desired. An optional on-chip dither function is available to improve SFDR performance with low power analog input signals.The AD9255 is available in a Pb-free, 48-lead LFCSP and is specified over the industrial temperature range of ?40?C to +85?C.PRODUCT HIGHLIGHTS On-chip dither option for improved SFDR performance with low power analog input. Proprietary differential input that maintains excellent SNR performance for input frequencies up to 300 MHz. Operation from a single 1.8 V supply and a separate digital output driver supply accommodating 1.8 V CMOS or LVDS outputs. Standard serial port interface (SPI) that supports various product features and functions, such as data formatting (offset binary, twos complement, or gray coding), enabling the clock DCS, power-down, test modes, and voltage reference mode. ?Pin compatibility with the AD9265, allowing a simple migration up to 16 bits.Applications Communications Multimode digital receivers (3G) GSM, EDGE, W-CDMA, LTE, CDMA2000, WiMAX, and TD-SCDMA Smart antenna systems General-purpose software radios Broadband data applications Ultrasound equipment

AD9268-125EBZ

Analog Devices Inc.The AD9268 is a dual, 16-bit, 80 MSPS/105 MSPS/125 MSPS analog-to-digital converter (ADC). The AD9268 is designed to support communications applications where high performance, combined with low cost, small size, and versatility, is desired.The dual ADC core features a multistage, differential pipelined architecture with integrated output error correction logic. Each ADC features wide bandwidth, differential sample-and-hold analog input amplifiers that support a variety of user-selectable input ranges. An integrated voltage reference eases design considerations. A duty cycle stabilizer is provided to compensate for variations in the ADC clock duty cycle, allowing the converters to maintain excellent performance.The ADC output data can be routed directly to the two external 16-bit output ports. These outputs can be set to either 1.8 V CMOS or LVDS.Flexible power-down options allow significant power savings, when desired.Programming for setup and control is accomplished using a 3-wire SPI-compatible serial interface.The AD9268 is available in a 64-lead LFCSP and is specified over the industrial temperature range of ?40?C to +85?C.PRODUCT HIGHLIGHTS On-chip dither option for improved SFDR performance with low power analog input. Proprietary differential input that maintains excellent SNR performance for input frequencies up to 300 MHz. Operation from a single 1.8 V supply and a separate digital output driver supply accommodating 1.8 V CMOS or LVDS outputs. Standard serial port interface (SPI) that supports various product features and functions, such as data formatting (offset binary, twos complement, or gray coding), enabling the clock DCS, power-down, test modes, and voltage reference mode. Pin compatibility with the AD9258, allowing a simple migration from 16 bits to 14 bits. The AD9268 is also pin compatible with the AD9251, AD9231, and AD9204 family of products for lower sample rate, low power applications.APPLICATIONS Communications Diversity radio systems Multimode digital receivers (3G) GSM, EDGE, W-CDMA, LTE, CDMA2000, WiMAX, TD-SCDMA I/Q demodulation systems Smart antenna systems General-purpose software radios Broadband data applications Ultrasound equipment

AD9269-80EBZ

Analog Devices Inc.The AD9269 is a monolithic, dual-channel, 1.8 V supply, 16-bit, 20/40/65/80 MSPS analog-to-digital converter (ADC). It features a high performance sample-and-hold circuit and on-chip voltage reference.The product uses multistage differential pipeline architecture with output error correction logic to provide 16-bit accuracy at 80 MSPS data rates and to guarantee no missing codes over the full operating temperature range.The AD9269 incorporates an optional integrated dc correction and quadrature error correction block (QEC) that corrects for dc offset, gain, and phase mismatch between the two channels. This functional block can be very beneficial to complex signal processing applications such as direct conversion receivers.The ADC also contains several features designed to maximize flexibility and minimize system cost, such as programmable clock and data alignment and programmable digital test pattern generation. The available digital test patterns include built-in deterministic and pseudorandom patterns, along with custom user-defined test patterns entered via the serial port interface (SPI).A differential clock input controls all internal conversion cycles. An optional duty cycle stabilizer (DCS) compensates for wide variations in the clock duty cycle while maintaining excellent overall ADC performance.The digital output data is presented in offset binary, gray code, or twos complement format. A data output clock (DCO) is pro-vided for each ADC channel to ensure proper latch timing with receiving logic. Both 1.8 V and 3.3 V CMOS levels are supported, and output data can be multiplexed onto a single output bus.The AD9269 is available in a 64-lead RoHS-compliant LFCSP and is specified over the industrial temperature range (?40?C to +85?C).APPLICATIONS Communications Diversity radio systems Multimode digital receivers GSM, EDGE, W-CDMA, LTE, CDMA2000, WiMAX, TD-SCDMA I/Q demodulation systems Smart antenna systems Battery-powered instruments Hand held scope meters Portable medical imaging Ultrasound Radar/LIDAR

AD9284-250EBZ

Analog Devices Inc.The AD9284 is a dual 8-bit, monolithic sampling, analog-to-digital converter (ADC) that supports simultaneous operation and is optimized for low cost, low power, and ease of use. Each ADC operates at up to a 250 MSPS conversion rate with outstanding dynamic performance.The ADC requires a single 1.8 V supply and an encode clock for full performance operation. No external reference components are required for many applications. The digital outputs are LVDS compatible.The AD9284 is available in a Pb-free, 48-lead LFCSP that is specified over the industrial temperature range of ?40?C to +85?C.PRODUCT HIGHLIGHTS Integrated dual 8-bit , 250 MSPS ADC. Single 1.8 V supply operation with LVDS outputs. Power-down option that is controlled through a pin programmable setting.APPLICATIONS Communications Diversity radio systems I/Q demodulation systems Battery-powered instruments Handheld scope meters Low cost digital oscilloscopes OTS: video over fiber

AD9508/PCBZ

Analog Devices Inc.The AD9508 provides clock fanout capability in a design thatemphasizes low jitter to maximize system performance. Thisdevice benefits applications like clocking data converters withdemanding phase noise and low jitter requirements.There are four independent differential clock outputs, each withvarious types of logic levels available. Available logic typesinclude LVDS (1.65 GHz), HSTL (1.65 GHz), and 1.8 V CMOS(250 MHz). In 1.8 V CMOS output mode, the differential outputbecomes two CMOS single-ended signals. The CMOS outputsare 1.8 V logic levels, regardless of the operating supply voltage.Each output has a programmable divider that can be bypassedor be set to divide by any integer up to 1024. In addition, theAD9508 supports a coarse output phase adjustment betweenthe outputs.The device can also be pin programmed for various fixedconfigurations at power-up without the need for SPI or I2C programming.The AD9508 is available in a 24-lead LFCSP and operates froma either a single 2.5 V or 3.3 V supply. The temperature range is?40?C to +85?C.Applications Low jitter, low phase noise clock distribution Clocking high speed ADCs, DACs, DDSs, DDCs, DUCs, MxFEs High performance wireless transceivers High performance instrumentation Broadband infrastructure

AD9517-1A/PCBZ

Analog Devices Inc.The AD9517-11?provides a multi-output clock distribution function with subpicosecond jitter performance, along with an on-chip PLL and VCO. The on-chip VCO tunes from 2.30 GHz to 2.65 GHz. Optionally, an external VCO/VCXO of up to 2.4 GHz can be used.The AD9517-1 emphasizes low jitter and phase noise to maximize data converter performance, and it can benefit other applications with demanding phase noise and jitter requirements.The AD9517-1 features four LVPECL outputs (in two pairs) and four LVDS outputs (in two pairs). Each LVDS output can be reconfigured as two CMOS outputs. The LVPECL outputs operate to 1.6 GHz, the LVDS outputs operate to 800 MHz, and the CMOS outputs operate to 250 MHz.For applications that require additional outputs, a crystal reference input, zero-delay, or EEPROM for automatic configuration at startup, the AD9520 and AD9522 are available. In addition, the AD9516 and AD9518 are similar to the AD9517 but have a different combination of outputs.Each pair of outputs has dividers that allow both the divide ratio and coarse delay (or phase) to be set. The range of division for the LVPECL outputs is 1 to 32. The LVDS/CMOS outputs allow a range of divisions up to a maximum of 1024.The AD9517-1 is available in a 48-lead LFCSP and can be operated from a single 3.3 V supply. An external VCO, which requires an extended voltage range, can be accommodated by connecting the charge pump supply (VCP) to 5 V. A separate LVPECL power supply can be from 2.5 V to 3.3 V (nominal).The AD9517-1 is specified for operation over the industrial range of ?40?C to +85?C.Applications Low jitter, low phase noise clock distribution 10/40/100 Gb/sec networking line cards, including SONET, Synchronous Ethernet, OTU2/3/4 Forward error correction (G.710) Clocking high speed ADCs, DACs, DDSs, DDCs, DUCs, MxFEs High performance wireless transceivers ATE and high performance instrumentation 1AD9517 is used throughout the data sheet to refer to all the members of the AD9517 family. However, when AD9517-1 is used, it is refers to that specific member of the AD9517 family.

AD9530/PCBZ

Analog Devices Inc.The AD9530 is a fully integrated PLL and distribution supporting, clock cleanup, and frequency translation device for 40 Gbps/ 100 Gbps OTN applications. The internal PLL can lock to one of two reference frequencies to generate four discrete output frequencies up to 2.7 GHz.The AD9530 features an internal 5.11 GHz to 5.4 GHz, ultralow noise voltage controlled oscillator (VCO). All four outputs are individually divided down from the internal VCO using two high speed VCO dividers (the Mx dividers) and four individual 8-bit channel dividers (the Dx dividers). The high speed VCO dividers offer fixed divisions of 2, 2.5, 3, and 3.5 for wide coverage of possible output frequencies. The AD9530 is configurable for loop bandwidths

AD9549A/PCBZ

Analog Devices Inc.The AD9549 provides synchronization for many systems, including synchronous optical networks (SONET/SDH). The AD9549 generates an output clock, synchronized to one of two external input references. The external references may contain significant time jitter, also specified as phase noise. Using a digitally controlled loop and holdover circuitry, the AD9549 continues to generate a clean (low jitter), valid output clock during a loss of reference condition, even when both references have failed.The AD9549 operates over an industrial temperature range of ?40?C to +85?C.APPLICATIONS Network synchronization Reference clock jitter cleanup SONET/SDH clocks up to OC-192, including FEC Stratum 3/3E reference clocks Wireless base stations, controllers Cable infrastructure Data communications