bq20z80 EVM Data Flash Settings for Num of Serial Cells/Pack Cap (Rev. B)

Texas InstrumentsThis application report describes the configuration changes in the data flash constants in the Texas Instruments bq20z80 Gas Gauge Evaluation Software for a variety of battery-pack configurations.

What's an LFSR? (Rev. A)

Texas InstrumentsThis document describes the linear feedback shift register (LFSR), fault grading, pseudorandom pattern generation (PRPG), and a parallel signature analyser (PSA). An LFSR and PSA are used to test a T

Configuring the bq27000/200 for Gas Gauge Applications

Texas InstrumentsUsers of the bq27000 and bq27200 ICs can program ten EEPROM locations to optimize setups for particular battery and host requirements. This application report describes how to configure these ICs for those requirements.

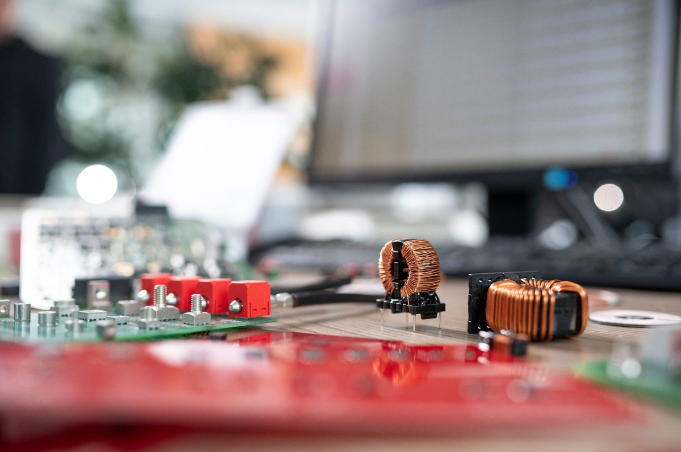

Improved Start-up Performance for Charge Pumps TPS6030x

Texas InstrumentsThis document shows a solution to enhance the start-up performance of the TPS603x charge pumps. With the circuitry shown, the device can drive at start-up into full load (40 mA).

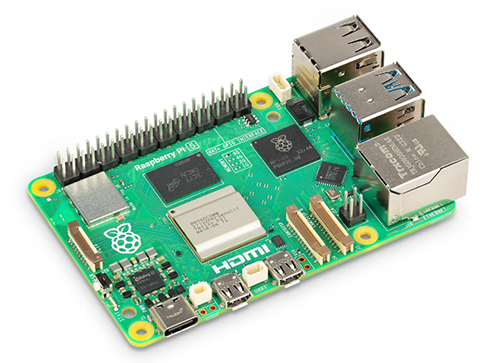

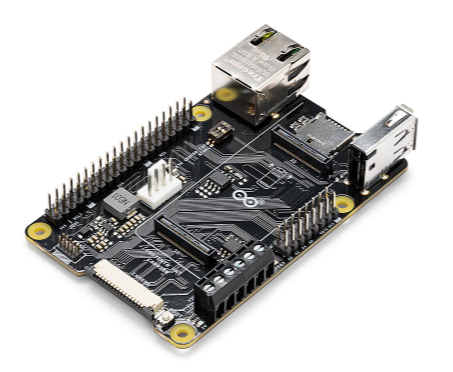

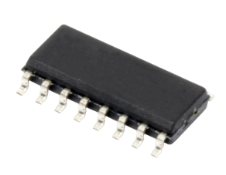

Recent Advancements In Bus-Interface Packaging And Processing (Rev. A)

Texas InstrumentsDesigners need a wide range of fine-pitch surface mount packages to meet today?s systems constraints in broad area and total volume. The SSOP and SQFP packages allow bus-interface logic devices to meet the wider data bus trends and provide superior electrical performance while minimizing space requirements. This document discusses the evolution of bus-interface packages their impedance the 3.3-

Floating-Point Arithmetic With the TMS32020 ( Contains Scanned Text)

Texas InstrumentsThis report presents algorithm and code implementing floating-point addition subtraction multiplication and division with the TMS320. The support of floating-point operations by the TI processors has made possible some applications such as implementation of the CCITT Adaptive Differential Pulse Code Modulation (ADPCM) algorithm and image/graphics operations.

DN601 -- CC-Antenna-DK Board #4 OTA Test Results (868 MHz) with EB (Rev. A)

Texas InstrumentsDN601 -- CC-Antenna-DK Board #4 OTA Test Results (868 MHz) with EB

Ground Loop Break (GLB) Circuits

Texas InstrumentsGround loops can be introduced when different components in audio systems are connected with standardaudio cables and these loops can cause annoying interference. In many cases the interference can bereduced significantly with a ground loop break (GLB) circuit including a low-value resistor and differentialamplifiers. This paper explains this approach and how to design a GLB circuit.

H.261 Implementation on the TMS320C80 DSP

Texas InstrumentsThis report describes the coding requirements techniques and decisions whichmust be made to utilize the TMS320C80 DSP as an integrated services digitalnetwork (ISDN) video-system manager and provides an overview on how theprocessor handles video signal in the ISDN narrow-band format in conformancewith the International Telecommunications Union (ITU)?T H.261 Recommendation.

TI Logic Solutions for Memory Interleaving With the Intel440BX Chipset

Texas InstrumentsIncreasing performance requirements of personal computers that necessitate a larger number of SDRAMs and DIMMs can be met by an FET-switch muliplexer. Four devices for memory interleaving for the 440BX and other core-logic chipsetsincorporate internal pulldown resistors damping resistors and make-before-break features that increase speed while maintaining minimal simultaneous-switching noise.

Channel Equalization for the IS-54 Digital Cellular System With the TMS320C5x

Texas InstrumentsToday?s communications equipment requires DSPs to perform complicated algorithms in a limited amount of time. One such algorithm is the equalizer in a digital receiver. The equalizer removes distortions caused by the communications link between the transmit and receive antennae. This document discusses implementing an equalizer for the IS-54 standard on the fixed point TMS320C5x DSP. Background fo

Using a Decompensated Operational Amplifier for Improved Performance

Texas InstrumentsDecompensated operational amplifiers have improved noise slew rate harmonic distortion etc. but required external compensation for stable operation. This report shows how to compensate such an amplifier and achieve the performance enchancement it provides in a unity-gain configuration.The THS4011 and THS4021 operational amplifiers are used to illustrate the superior performance mentioned a

Using TI's Embedded Processor Software Toolkit for Medical Imaging (MED-STK)

Texas InstrumentsAdvances in digital signal processors (DSPs) are driving both high-computational performance and power efficiency into ever increasing application areas. The medical diagnostic ultrasound industry can

AM/DM37x Power Estimation Spreadsheet

Texas InstrumentsThis article has been contributed to the TI Developer Wiki. To see the most recently updated version or tocontribute visit this topic at:

http://processors.wiki.ti.com/index.php/AM/DM37x_Power_Estimation_Spreadsheet

This article discusses the power consumption of the Texas Instruments AM/DM37x high