Parallel Camera Interface for Sitara Processors

Description

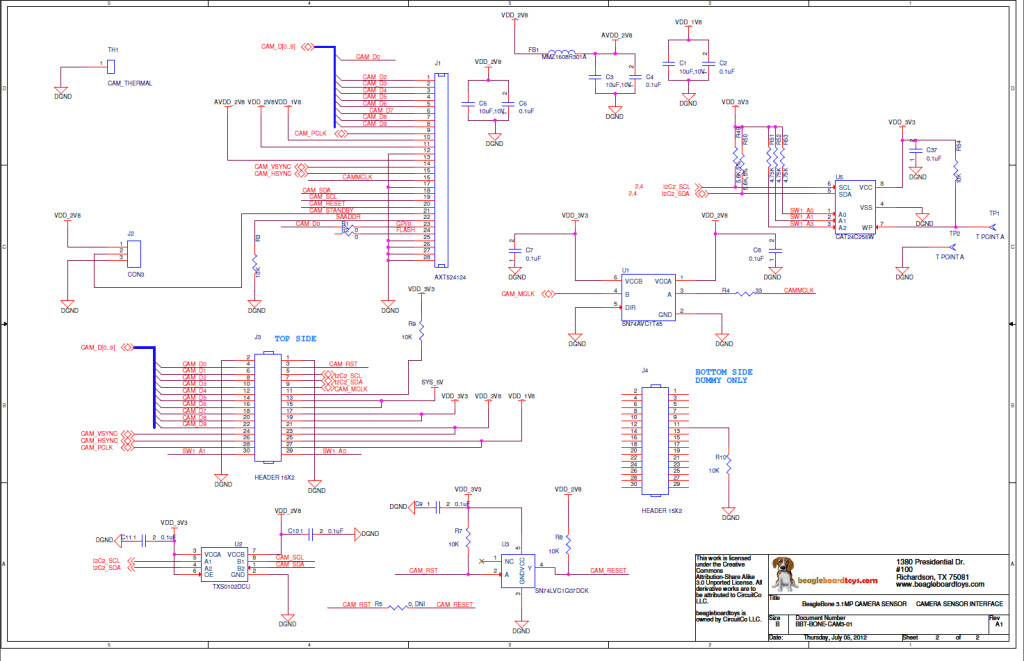

This camera interface design connects to a 10-bit parallel interface to the AM335x general purpose memory controller (GPMC) 16-bit multiplexed address/data bus. This design consumes roughly 150mW less power than typical USB solutions: and is ideal for applications like portable data terminals: ruggedized handhelds: portable consumer: industrial handhelds and others. The reference design is based on the QuickLogic 3.1 MP Camera Sensor (using an Aptina 3.1 MP sensor) connected to a camera expansion board. Together: they connect to the BeagleBone platform. The BeagleBone and the QuickLogic 3.1 MP camera add-on board are available for purchase.More information on QuickLogic: http://www.quicklogic.comMore information about BeagleBone: http://www.ti.com/tool/beaglebnMore information about the QuickLogic 3.1 MP camera add-on board for the BeagleBone: including design files and software: http://www.quicklogic.com/solutions/reference-designs/ti-sitara-beaglebone-camera-cape/

Features

- Supports up to 5MP camera at 10fps with DMAUp to 30 frames per second (fps) at VGA (640 x 480) resolutionReduces system power consumption up to 150mWNo software effort required for OEM6x6mm: non-HDI rules packageThis is an example sub-system design that includes schematics: BOM: Gerbers and other design files.

Applications

- Barcode scanner

- Machine vision camera

- Video doorbell

- Barcode reader

- Automated sorting equipment

- Optical inspection

- Eye

- ear

- nose & throat exam

- Thermal imaging camera

- Drone payload control

- Vision sensors

- Analog security camera

- IP network camera

- Wireless security camera

Product Categories

| Download the bill of materials for TIDEP0018 | Download |

Design File

Download ready-to-use system files to speed your design process. Get Viewer.

Download the design file for TIDEP0018Test Data

Get results faster with test and simulation data that's been verified.

Download the test file for TIDEP0018| Title | Updated | Type | Size (KB) | |

|---|---|---|---|---|

| Parallel Camera interface for Sitara Processors CAD Design Files | 30 Jul 2014 | ZIP | 141 | |

| Parallel Camera Interface for Sitara Processors PCB Layout Design Files | 30 Jul 2014 | ZIP | 1460 | |

| Parallel Camera interface for Sitara Processors Gerber Design Files | 30 Jul 2014 | ZIP | 1460 | |

| Parallel Camera interface for Sitara Processors Bill of Materials (BOM) | 30 Jul 2014 | ZIP | 22 | |

| Parallel Camera interface for Sitara Processors Schematic | 30 Jul 2014 | ZIP | 150 |